XDC介紹

XDC 是 Xilinx Design Constraints 的簡(jiǎn)寫,但其基礎(chǔ)語(yǔ)法來(lái)源于業(yè)界統(tǒng)一的約束規(guī)范SDC。XDC 在本質(zhì)上就是 Tcl 語(yǔ)言,但其僅支持基本的 Tcl 語(yǔ)法如變量、列表和運(yùn)算符等等,對(duì)其它復(fù)雜的循環(huán)以及文件 I/O 等語(yǔ)法可以通過(guò)在 Vivado 中 source 一個(gè) Tcl 文件的方式來(lái)補(bǔ)充。

SDC、XDC跟 Vivado Tcl 的關(guān)系如下圖所示。

XDC的基本語(yǔ)法可以分為時(shí)鐘約束、I/O約束以及時(shí)序例外約束三大類。根據(jù)Xilinx的UltraFast設(shè)計(jì)方法學(xué)中Baseline部分的建議(UG949中有詳細(xì)介紹),對(duì)一個(gè)設(shè)計(jì)進(jìn)行約束的先后順序也可以依照這三類約束依次進(jìn)行。本文對(duì)可以在幫助文檔中查到的基本XDC語(yǔ)法不做詳細(xì)解釋,會(huì)將重點(diǎn)放在使用方法和技巧上。

時(shí)鐘約束

時(shí)鐘約束必須最早創(chuàng)建,對(duì)7系列FPGA來(lái)說(shuō),端口進(jìn)來(lái)的主時(shí)鐘以及GT的輸出RXCLK/TX CLK都必須由用戶使用create_clock自主創(chuàng)建。而衍生時(shí)鐘則分為以下兩類:

MMCM/PLL/BUFR的輸出時(shí)鐘都可以由Vivado自動(dòng)推導(dǎo),無(wú)需用戶創(chuàng)建。若用戶僅希望改變衍生鐘的名字,其余頻率等都由工具自動(dòng)推導(dǎo),則只需寫明三個(gè)option,其余不寫即可:create_generated_clock [-name arg] [-source args] [-master_clock arg] 工具不能自動(dòng)推導(dǎo)出衍生鐘的情況,包括使用寄存器和組合邏輯搭建的分頻器等,必須由用戶使用create_generated_cl ock來(lái)創(chuàng)建。

I/O約束

在設(shè)計(jì)的初級(jí)階段,可以不加I/O約束,讓工具專注于滿足FPGA內(nèi)部的時(shí)序要求。當(dāng)時(shí)序要求基本滿足后,再加上I/O約束跑實(shí)現(xiàn)。

XDC中的I/O約束有以下幾點(diǎn)需要注意:

① 不加任何I/O約束的端口時(shí)序要求被視作無(wú)窮大。

② XDC中的set_input_delay / set_output_delay對(duì)應(yīng)于UCF中OFFSET IN / OFFSET OUT,但視角相反。OFFSET IN / OFFSET OUT是從FPGA內(nèi)部延時(shí)的角度來(lái)約束端口時(shí)序,set_input_de lay / set_output_ delay則是從系統(tǒng)角度來(lái)約束。

③ 典型的I/O時(shí)序,包括系統(tǒng)同步、源同步、SDR和DDR等等,在Vivado圖形界面的XDC templates中都有示例。2014.1版后還有一個(gè)Timing Constraints Wizard可供使用。

時(shí)序例外約束

時(shí)序例外約束包括set_max_delay/set_min_delay ,set_multicycle_path,set_false_path等,這類約束除了要滿足XDC的先后順序優(yōu)先級(jí)外,還受到自身優(yōu)先級(jí)的限制。一個(gè)總的原則就是針對(duì)同一條路徑,對(duì)約束目標(biāo)描述越具體的優(yōu)先級(jí)越高。不同的時(shí)序例外約束以及同一約束中不同條件的優(yōu)先級(jí)如下所示:

舉例來(lái)說(shuō),依次執(zhí)行如下兩條XDC,盡管第二條最后執(zhí)行,但工具仍然認(rèn)定第一條約束設(shè)定的15為clk1到clk2之間路徑的max delay值。

再比如,對(duì)圖示路徑依次進(jìn)行如下四條時(shí)序例外約束,優(yōu)勝者將是第二條。但如果再加入最后一條約束,false path的優(yōu)先級(jí)最高,會(huì)取代之前所有的時(shí)序例外約束。

高效的時(shí)鐘約束

約束最終是為了設(shè)計(jì)服務(wù),所以要用好XDC就需要深入理解電路結(jié)構(gòu)和設(shè)計(jì)需求。接下來(lái)我們就以常見(jiàn)FPGA設(shè)計(jì)中的時(shí)鐘結(jié)構(gòu)來(lái)舉例,詳細(xì)闡述XDC的約束技巧。

時(shí)序的零起點(diǎn)

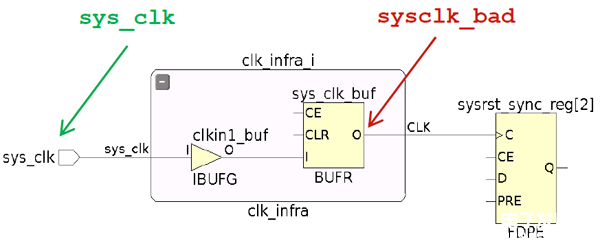

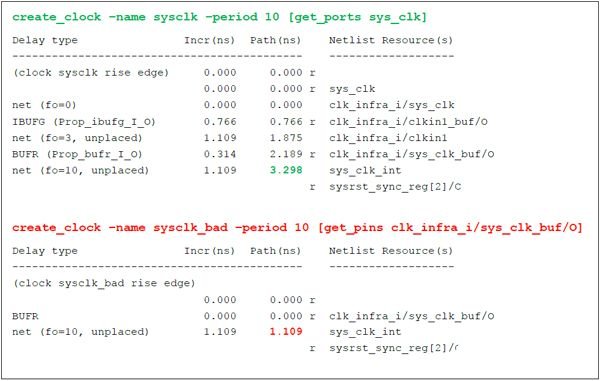

用create_clock定義的主時(shí)鐘的起點(diǎn)即時(shí)序的“零起點(diǎn)”,在這之前的上游路徑延時(shí)都被工具自動(dòng)忽略。所以主時(shí)鐘創(chuàng)建在哪個(gè)“點(diǎn)”很重要,以下圖所示結(jié)構(gòu)來(lái)舉例,分別于FPGA輸入端口和BUFG輸出端口創(chuàng)建一個(gè)主時(shí)鐘,在時(shí)序報(bào)告中體現(xiàn)出的路徑延時(shí)完全不同,很明顯sysclk_bad的報(bào)告中缺少了之前一段的延時(shí),時(shí)序報(bào)告不可信。

時(shí)鐘定義的先后順序

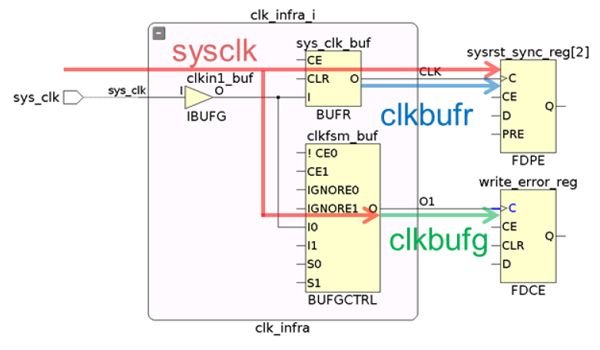

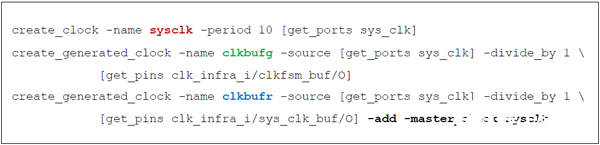

時(shí)鐘的定義也遵從XDC/Tcl的一般優(yōu)先級(jí),即:在同一個(gè)點(diǎn)上,由用戶定義的時(shí)鐘會(huì)覆蓋工具自動(dòng)推導(dǎo)的時(shí)鐘,且后定義的時(shí)鐘會(huì)覆蓋先定義的時(shí)鐘。若要二者并存,必須使用 -add 選項(xiàng)。

上述例子中BUFG的輸出端由用戶自定義了一個(gè)衍生鐘clkbufg,這個(gè)衍生鐘便會(huì)覆蓋此處原有的sysclk。此外,圖示BUFR工作在bypass模式,其輸出不會(huì)自動(dòng)創(chuàng)建衍生鐘,但在BUFR的輸出端定義一個(gè)衍生鐘clkbufr,并使用-add 和 -master_clock 選項(xiàng)后,這一點(diǎn)上會(huì)存在sysclk和clkbufg兩個(gè)重疊的時(shí)鐘。如下的Tcl命令驗(yàn)證了我們的推論。

不同于UCF約束,在XDC中,所有的時(shí)鐘都會(huì)被缺省認(rèn)為是相關(guān)的,也就是說(shuō),網(wǎng)表中所有存在的時(shí)序路徑都會(huì)被Vivado分析。這也意味著FPGA設(shè)計(jì)人員必須通過(guò)約束告訴工具,哪些路徑是無(wú)需分析的,哪些時(shí)鐘域之間是異步的。

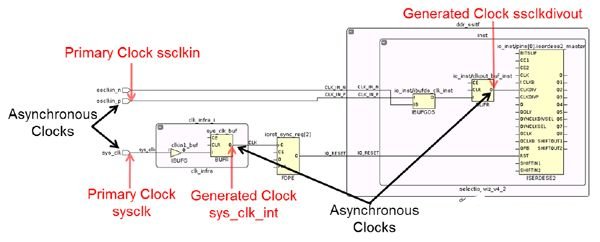

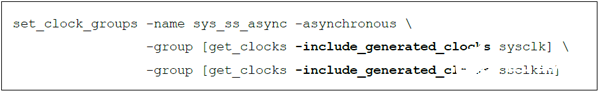

如上圖所示,兩個(gè)主時(shí)鐘ssclkin和sysclk由不同的端口進(jìn)入FPGA,再經(jīng)由不同的時(shí)鐘網(wǎng)絡(luò)傳遞,要將它們?cè)O(shè)成異步時(shí)鐘,可以使用如下約束:

其中,-include_generated_clocks 表示所有衍生鐘自動(dòng)跟其主時(shí)鐘一組,從而與其它組的時(shí)鐘之間為異步關(guān)系。不加這個(gè)選項(xiàng)則僅僅將時(shí)鐘關(guān)系的約束應(yīng)用在主時(shí)鐘層面。

重疊(單點(diǎn)多個(gè))時(shí)鐘

重疊時(shí)鐘是指多個(gè)時(shí)鐘共享完全相同的時(shí)鐘傳輸網(wǎng)絡(luò),例如兩個(gè)時(shí)鐘經(jīng)過(guò)一個(gè)MUX選擇后輸出的時(shí)鐘,在有多種運(yùn)行模式的設(shè)計(jì)中很常見(jiàn)。

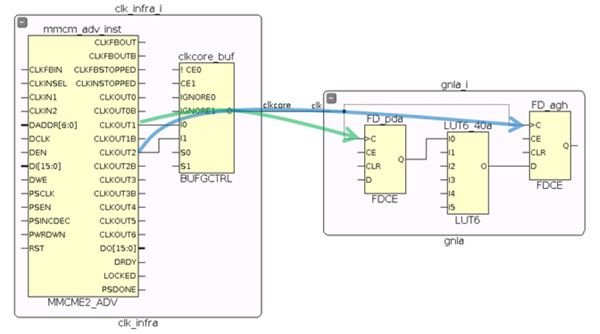

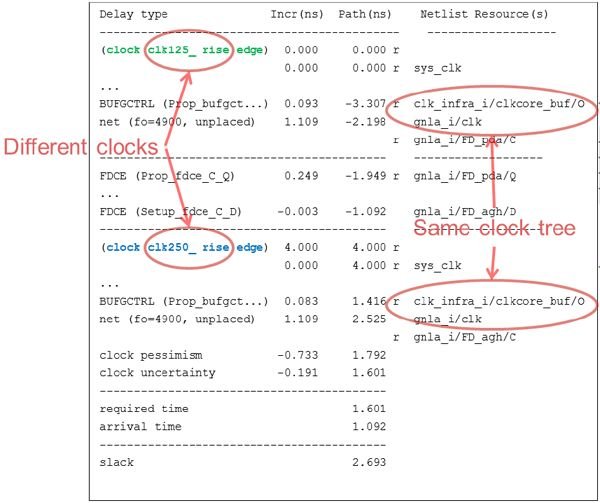

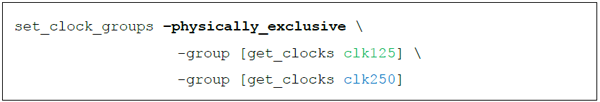

如下圖所示,clk125和clk250是clkcore_buf的兩個(gè)輸入時(shí)鐘,不約束時(shí)鐘關(guān)系的情況下,Vivado會(huì)對(duì)圖示路徑做跨時(shí)鐘域(重疊時(shí)鐘之間)分析。這樣的時(shí)序報(bào)告即便沒(méi)有違例,也是不可信的,因?yàn)閏lk125和clk250不可能同時(shí)驅(qū)動(dòng)這條路徑上的時(shí)序元件。這么做也會(huì)增加運(yùn)行時(shí)間,并影響最終的實(shí)現(xiàn)效果。

如果clk125和clk250除了通過(guò)clkcore_buf后一模一樣的扇出外沒(méi)有驅(qū)動(dòng)其它時(shí)序元件,我們要做的僅僅是補(bǔ)齊時(shí)鐘關(guān)系的約束。

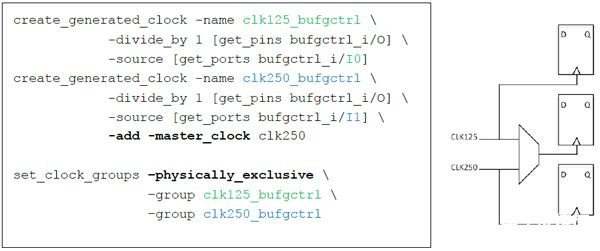

在很多情況下,除了共同的扇出,其中一個(gè)時(shí)鐘或兩個(gè)都還驅(qū)動(dòng)其它的時(shí)序元件,此時(shí)建議的做法是在clkcore_buf的輸出端上創(chuàng)建兩個(gè)重疊的衍生鐘,并將其時(shí)鐘關(guān)系約束為-physically_exclusive 表示不可能同時(shí)通過(guò)。這樣做可以最大化約束覆蓋率,也是ISE和UCF中無(wú)法做到的。

其它高級(jí)約束

時(shí)鐘的約束是XDC的基礎(chǔ),熟練掌握時(shí)鐘約束,也是XDC約束技巧的基礎(chǔ)。其它高級(jí)約束技巧,包括復(fù)雜的CDC(Clock Domain Crossing)約束和接口時(shí)序(SDR、DDR、系統(tǒng)同步接口和源同步接口)約束等方面還有很多值得注意的地方。

-

Vivado

+關(guān)注

關(guān)注

19文章

830瀏覽量

68278 -

時(shí)鐘約束

+關(guān)注

關(guān)注

0文章

15瀏覽量

6103

發(fā)布評(píng)論請(qǐng)先 登錄

介紹三種常見(jiàn)的MySQL高可用方案

FPGA時(shí)序約束之設(shè)置時(shí)鐘組

一文詳解Vivado時(shí)序約束

GaN、超級(jí)SI、SiC這三種MOS器件的用途區(qū)別

示波器的三種觸發(fā)模式

時(shí)序約束一主時(shí)鐘與生成時(shí)鐘

三種封裝形式下的400G光模塊概述

什么是PID調(diào)節(jié)器的三種模式

I2S有左對(duì)齊,右對(duì)齊跟標(biāo)準(zhǔn)的I2S三種格式,那么這三種格式各有什么優(yōu)點(diǎn)呢?

基本放大電路有哪三種

mosfet的三種工作狀態(tài)及工作條件是什么

單片機(jī)的三種總線結(jié)構(gòu)

三種功率器件的應(yīng)用區(qū)別

評(píng)論