前言

很多人第一次接觸Altera Cyclone系列FPGA的時(shí)候,可能會(huì)被其復(fù)雜的專用管腳給搞混淆,在這里我們Altera Cyclone系列FPGA的專用管腳一一列出供您參考,希望對(duì)您的設(shè)計(jì)有幫助。本文適用于Altera Cyclone III系列FPGA,對(duì)Cyclone II以及IV絕大部分的是適用的,但是個(gè)別的管腳,例如MSEL等不適用。具體到您的設(shè)計(jì),還請(qǐng)您仔細(xì)查看您器件的Datasheet。

Altera Cyclone系列FPGA配置模式

Altera公司的Cyclone系列低端FPGA的特殊管腳基本都是用于配置用途,其支持以下幾種配置模式:

Active parallel (AP) for Cyclone III devices only

Passive serial (PS)

Fast passive parallel (FPP)

Joint Test Action Group (JTAG)

在大部分設(shè)計(jì)中,出于成本以及節(jié)約IO的考慮采用的是串行FLASH-AS模式+JTAG。以下就是所用到的一些管腳的說(shuō)明:

Altera Cyclone系列FPGA專用管腳說(shuō)明

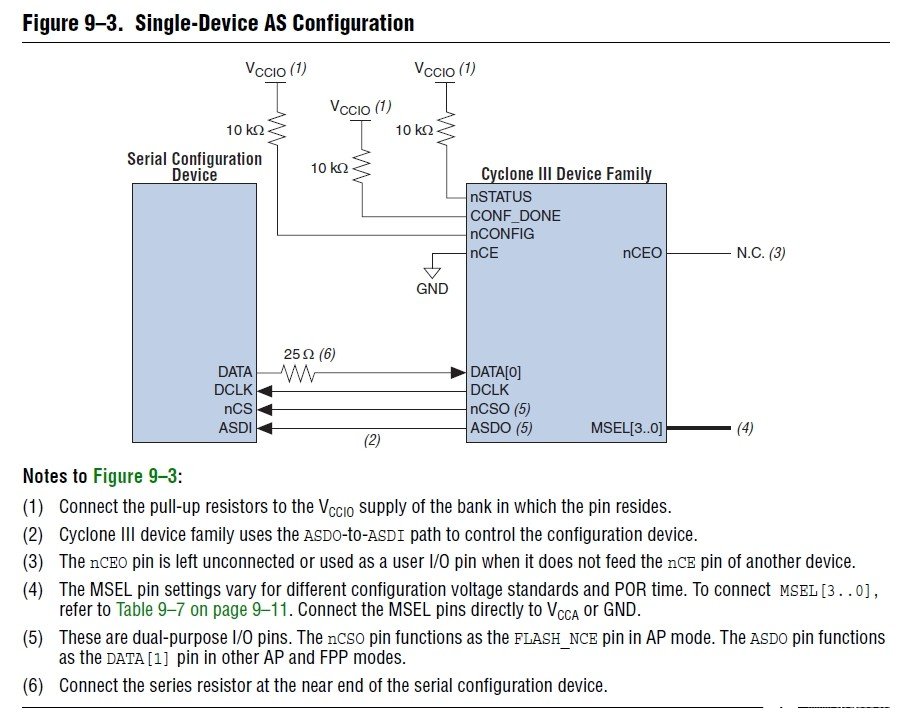

AS配置引腳接線圖

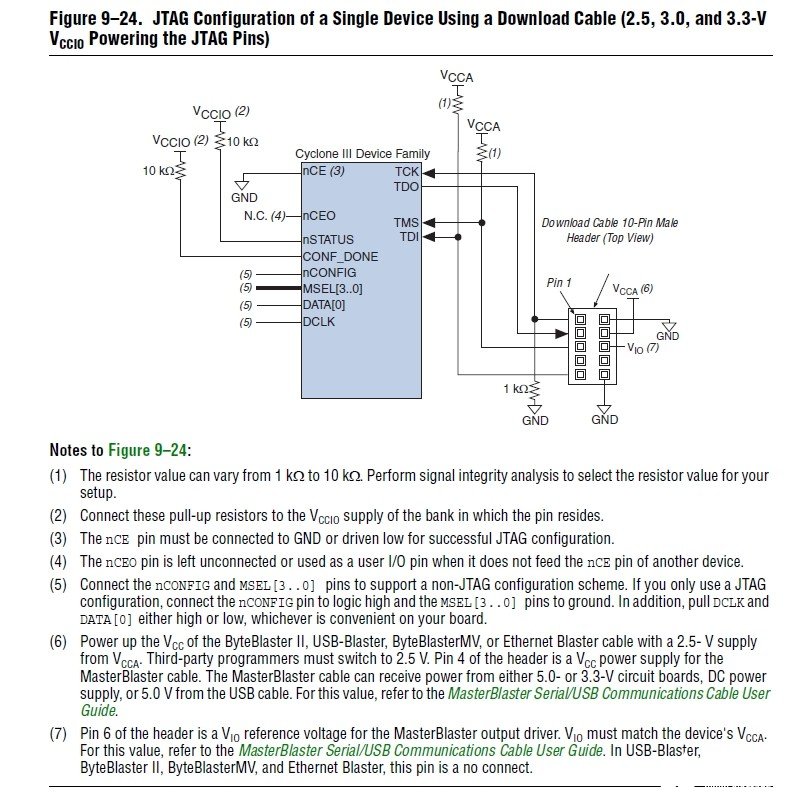

JTAG引腳接線圖

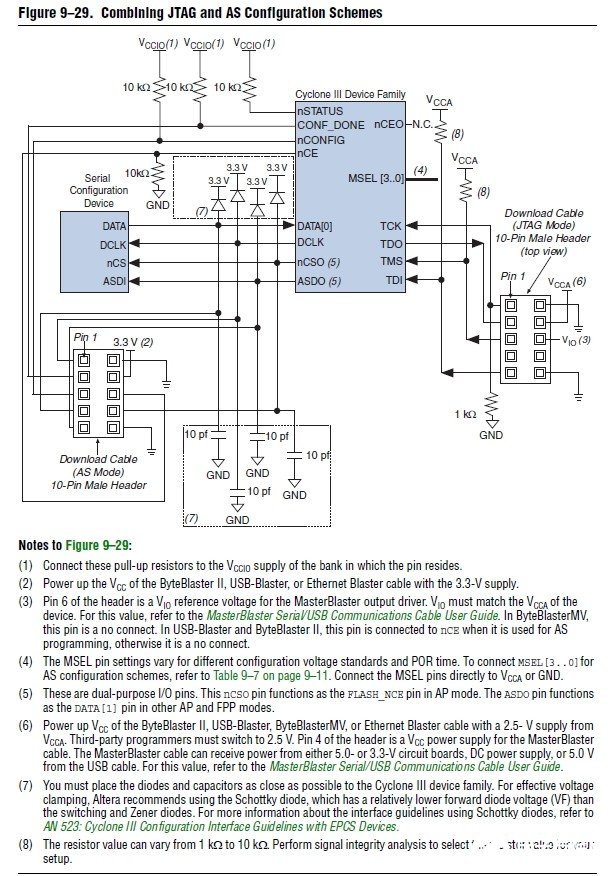

完整的JTAG+AS接線圖

以下就是Altera Cyclone系列FPGA專用管腳說(shuō)明:

1.I/O,nCSO

在AS 模式下是專用輸出腳,在PS 和JTAG 模式下可以當(dāng)I/O 腳來(lái)用。在AS 模式下,這個(gè)腳是CIII 用來(lái)給外面的串行配置芯片發(fā)送的使能腳。在AS 模式下,ASDO 有一個(gè)內(nèi)部的上拉電阻,一直有效。這個(gè)腳是低電平有效的。直接接到配置芯片的/CS 腳(第1腳)。

2.I/O, ASDO

在AS 模式下是專用輸出腳,在PS 和JTAG 模式下可以當(dāng)I/O 腳來(lái)用。在AS 模式下,這個(gè)腳是CIII 向串行配置芯片發(fā)送控制信號(hào)的腳。也是用來(lái)從配置芯片中讀配置數(shù)據(jù)的腳。在AS 模式下,ASDO 有一個(gè)內(nèi)部的上拉電阻,一直有效,配置完成后,該腳就變成三態(tài)輸入腳。ASDO 腳直接接到配置芯片的ASDI 腳(第5 腳)。

3.I/O,CRC_ERROR

當(dāng)錯(cuò)誤檢測(cè)CRC 電路被選用時(shí),這個(gè)腳就被作為CRC_ERROR 腳,如果不用默認(rèn)就用來(lái)做I/O。但要注意,這個(gè)腳是不支持漏極開(kāi)路和反向的。當(dāng)它作為CRC_ERROR 時(shí),高電平輸出則表示出現(xiàn)了CRC 校驗(yàn)錯(cuò)誤(在配置SRAM 各個(gè)比特時(shí)出現(xiàn)了錯(cuò)誤)。CRC 電路的支持可以在setting 中加上。這個(gè)腳一般與nCONFIG 腳配合起來(lái)用。即如果配置過(guò)程出錯(cuò),重新配置。

4.I/O,CLKUSR

當(dāng)在軟件中打開(kāi)Enable

User-supplled start-up clock(CLKUSR)選項(xiàng)后,這個(gè)腳就只可以作為用戶提供的初始化時(shí)鐘輸入腳。在所有配置數(shù)據(jù)都已經(jīng)被接收后,CONF_DONE 腳會(huì)變成高電平,CIII 器件還需要299 個(gè)時(shí)鐘周期來(lái)初始化寄存器,I/O 等等狀態(tài),F(xiàn)PGA 有兩種方式,一種是用內(nèi)部的晶振(10MHz),另一種就是從CLKUSR 接進(jìn)來(lái)的時(shí)鐘(最大不能超過(guò)100MHz)。有這個(gè)功能,可以延緩FPGA 開(kāi)始工作的時(shí)間,可以在需要和其它器件進(jìn)行同步的特殊應(yīng)用中用到。

5.I/O,VREF

用來(lái)給某些差分標(biāo)準(zhǔn)提供一個(gè)參考電平。沒(méi)有用到的話,可以當(dāng)成I/O 來(lái)用。

6. DATA0

專用輸入腳。在AS 模式下,配置的過(guò)程是:CIII 將nCSO 置低電平,配置芯片被使能。CIII然后通過(guò)DCLK 和ASDO 配合操作,發(fā)送操作的命令,以及讀的地址給配置芯片。配置芯片然后通過(guò)DATA 腳給CIII 發(fā)送數(shù)據(jù)。DATA 腳就接到CIII 的DATA0 腳上。CII接收完所有的配置數(shù)據(jù)后,就會(huì)釋放CONF_DONE 腳(即不強(qiáng)制使CONF_DONE 腳為低電平),CONF_DONE 腳是漏極開(kāi)路(Open-Drain)的。這時(shí)候,因?yàn)镃ONF_DONE 在外部會(huì)接一個(gè)10K 的電阻,所以它會(huì)變成高電平。同時(shí),CII 就停止DCLK 信號(hào)。在CONF_DONE 變成高電平以后(這時(shí)它又相當(dāng)于變成一個(gè)輸入腳),初始化的過(guò)程就開(kāi)始了。所以,CONF_DONE 這個(gè)腳外面一定要接一個(gè)10K 的電阻,以保證初始化過(guò)程可以正確開(kāi)始。 DATA0,DCLK,NCSO,ASDO 腳上都有微弱的上拉電阻,且一直有效。在配置完成后,這些腳都會(huì)變成輸入三態(tài),并被內(nèi)部微弱的上拉電阻將電平置為高電平。在AS 模式下,DATA0就接到配置芯片的DATA(第2 腳)。主語(yǔ),DATA0需要接一個(gè)25歐的電阻,用來(lái)減少過(guò)沖。

7. DCLK

PS 模式下是輸入,AS 模式下是輸出。在PS 模式下,DCLK 是一個(gè)時(shí)鐘輸入腳,是外部器件將配置數(shù)據(jù)傳送給FPGA 的時(shí)鐘。數(shù)據(jù)是在DCLK 的上升沿把數(shù)據(jù),在AS 模式下,DCLK腳是一個(gè)時(shí)鐘輸出腳,就是提供一個(gè)配置時(shí)鐘。直接接到配置芯片的DCLK 腳上去(第6腳)。無(wú)論是哪種配置模式,配置完成后,這個(gè)腳都會(huì)變成三態(tài)。如果外接的是配置器件,配置器件會(huì)置DCLK 腳為低電平。如果使用的是主控芯片,可以將DCLK 置高也可以將DCLK 置低。配置完成后,觸發(fā)這個(gè)腳并不會(huì)影響已配置完的FPGA。這個(gè)腳帶了輸入Buffer,支持施密特觸發(fā)器的磁滯功能。

8. nCE

專用輸入腳。這個(gè)腳是一個(gè)低電平有效的片選使能信號(hào)。nCE 腳是配置使能腳。在配置,初始化以及用戶模式下,nCE 腳必須置低。在多個(gè)器件的配置過(guò)程中,第一個(gè)器件的nCE 腳要置低,它的nCEO 要連接到下一個(gè)器件的nCE 腳上,形成了一個(gè)鏈。nCE腳在用JTAG編程模式下也需要將nCE 腳置低。 這個(gè)腳帶了輸入Buffer,支持施密特觸發(fā)器的磁滯功能。

9. nCONFIG

專用的輸入管腳。這個(gè)管腳是一個(gè)配置控制輸入腳。如果這個(gè)腳在用戶模式下被置低,F(xiàn)PGA就會(huì)丟失掉它的配置數(shù)據(jù),并進(jìn)入一個(gè)復(fù)位狀態(tài),并將所有的I/O 腳置成三態(tài)的。nCONFIG從低電平跳變到高電平的過(guò)程會(huì)初始化重配置的過(guò)程。如果配置方案采用增強(qiáng)型的配置器件或EPC2,用戶可以將nCONFIG 腳直接接到VCC 或到配置芯片的nINIT_CONF 腳上去。這個(gè)腳帶了輸入Buffer,支持施密特觸發(fā)器的磁滯功能。實(shí)際上,在用戶模式下,nCONFIG信號(hào)就是用來(lái)初始化重配置的。當(dāng)nCONFIG 腳被置低后,初始化進(jìn)程就開(kāi)始了。當(dāng)nCONFIG腳被置低后,CIII 就被復(fù)位了,并進(jìn)入了復(fù)位狀態(tài),nSTATUS 和CONF_DONE 腳被置低,所有的I/O腳進(jìn)入三態(tài)。nCONFIG 信號(hào)必須至少保持2us。當(dāng)nCONFIG 又回到高電平狀態(tài)后,nSTATUS 又被釋放。重配置就開(kāi)始了。在實(shí)際應(yīng)用過(guò)程中可以將nCONFIG 腳接一個(gè)10K 的上拉電阻到3.3V.

10. DEV_OE

I/O 腳或全局I/O 使能腳。在Quartus II 軟件中可以使能DEV_OE 選項(xiàng)(Enable Device-wideoutput Enable),如果使能了這一個(gè)功能,這個(gè)腳可以當(dāng)全局I/O 使能腳,這個(gè)腳的功能是,如果它被置低,所有的I/O 都進(jìn)入三態(tài)。

11. INIT_DONE

I/O 腳或漏極開(kāi)路的輸出腳。當(dāng)這個(gè)腳被使能后,該腳上從低到高的跳變指示FPGA 已經(jīng)進(jìn)入了用戶模式。如果INIT_DONE 輸出腳被使能,在配置完成以后,這個(gè)腳就不能被用做用戶I/O 了。在QuartusII 里面可以通過(guò)使能Enable INIT_DONE 輸出選項(xiàng)使能這個(gè)腳。

12. nCEO

I/O 腳或輸出腳。當(dāng)配置完成后,這個(gè)腳會(huì)輸出低電平。在多個(gè)器件的配置過(guò)程中,這個(gè)腳會(huì)連接到下一個(gè)器件的nCE 腳,這個(gè)時(shí)候,它還需要在外面接一個(gè)10K 的上拉電阻到Vccio。多個(gè)器件的配置過(guò)程中,最后一個(gè)器件的nCEO 可以浮空。如果想把這個(gè)腳當(dāng)成可用的I/O,需要在軟件里面做一下設(shè)置。另外,就算是做I/O,也要等配置完成以后。

13. nSTATUS

這是一個(gè)專用的配置狀態(tài)腳。雙向腳,當(dāng)它是輸出腳時(shí),是漏極開(kāi)路的。在上電之后,F(xiàn)PGA立刻將nSTATUS 腳置成低電平,并在上電復(fù)位(POR)完成之后,釋放它,將它置為高電平。作為狀態(tài)輸出腳時(shí),在配置過(guò)程中如果有任何一個(gè)錯(cuò)誤發(fā)生了,nSTATUS腳會(huì)被置低。作為狀態(tài)輸入腳時(shí),在配置或初始化過(guò)程中,外部控制芯片可以將這個(gè)腳拉低,這時(shí)候FPGA就會(huì)進(jìn)入錯(cuò)誤狀態(tài)。這個(gè)腳不能用作普通I/O 腳。nSTATUS 腳必須上拉一個(gè)10K 歐的電阻。

14. CONF_DONE

這是一個(gè)專用的配置狀態(tài)腳。雙向腳,當(dāng)它是輸出腳時(shí),是漏極開(kāi)路的。當(dāng)作為狀態(tài)輸出腳時(shí),在配置之前和過(guò)程中,它都被置為低電平。一旦配置數(shù)據(jù)接收完成,并且沒(méi)有任何錯(cuò)誤,初始化周期一開(kāi)始,CONF_DONE 就會(huì)被釋放。當(dāng)作為狀態(tài)輸入腳時(shí),在所有數(shù)據(jù)都被接收后,要將它置為高電平。之后器件就開(kāi)始初始化再進(jìn)入用戶模式。它不可以用作普通I/O來(lái)用。這個(gè)腳外成也必須接一個(gè)10K 歐的電阻。

15. MSEL[3:0]

這些腳要接到GND或電源,表示高電平或低電平。AS模式分為快速和標(biāo)準(zhǔn),此外,IO電源電壓不同,MSEL也不盡相同, JTAG 模式跟MSEL 無(wú)關(guān),即用JTAG模式,MSEL 會(huì)被忽略,一般3.3VAS模式采用0010。

16.DEV_CLRn

I/O 或全局的清零輸入端。在QuartusII 里面,如果選上Enable Device-Wide Reset(DEV_CLRn)這個(gè)功能。這個(gè)腳就是全局清零端。當(dāng)這個(gè)腳被置低,所有的寄存器都會(huì)被清零。這個(gè)腳不會(huì)影響到JTAG 的邊界掃描或編程的操作。

-

FPGA

+關(guān)注

關(guān)注

1644文章

22006瀏覽量

616273 -

Altera

+關(guān)注

關(guān)注

37文章

803瀏覽量

155716 -

串行

+關(guān)注

關(guān)注

0文章

237瀏覽量

34406

發(fā)布評(píng)論請(qǐng)先 登錄

怎樣為自己的設(shè)計(jì)選擇Altera Cyclone V FPGA?

在高清晰LCD HDTV 中使用Cyclone III FPGA

Altera Cyclone III FPGA緊湊型集成電源解決方案

什么是Altera系列低成本Cyclone IV FPGA?

MCU配置Altera-Cyclone系列FPGA的相關(guān)資料下載

開(kāi)源硬件-TIDA-00604-采用 TPS65023 的 Altera Cyclone III FPGA 電源 PCB layout 設(shè)計(jì)

Altera Cyclone III HSMC視頻方案

利用高級(jí)Cyclone III FPGA PLL,提高靈活性

Altium推出采用Altera Cyclone III F

Altium推出采用Altera Cyclone III的最

ETL-002 Altera Cyclone III系列FPGA開(kāi)發(fā)板簡(jiǎn)介

Altera Cyclone IV GX系列FPGA開(kāi)發(fā)方案

Altera Cyclone IV GX系列的特性及FPGA開(kāi)發(fā)套件的設(shè)計(jì)方案介紹

Altera Cyclone III系列FPGA開(kāi)發(fā)板的庫(kù)文件免費(fèi)下載

評(píng)論