(文章來源:驅動之家)

由于在7nm節點激進地采用了EUV工藝,三星的7nm工藝量產時間比臺積電要晚了一年,目前采用高通的驍龍765系列芯片使用三星7nm EUV工藝量產。在這之后,三星已經加快了新工藝的進度,日前6nm工藝也已經量產出貨,今年還會完成3nm GAE工藝的開發。

在進入10nm節點之后,半導體工藝制造越來越困難,但需求還在不斷提升,這就導致臺積電、三星把不同的工藝改進下就推出新工藝了,而三星的6nm工藝實際上也就是7nm工藝的改進版,在7nm EUV基礎上應用三星獨特的Smart Scaling方案,可以大大縮小芯片面積,帶來超低功耗。

消息人士透露,三星晶圓制造業務的高管已經確認6nm工藝的芯片出貨量產,交付給北美的客戶——雖然三星官方沒有提及具體信息,但這個北美客戶應該是高通公司,目前還不確定是哪款芯片。如果6nm成功量產,那三星手里現在進入真正量產階段的工藝就有7nm EUV、6nm LPP兩種了,可以更好地從臺積電手中搶市場了。

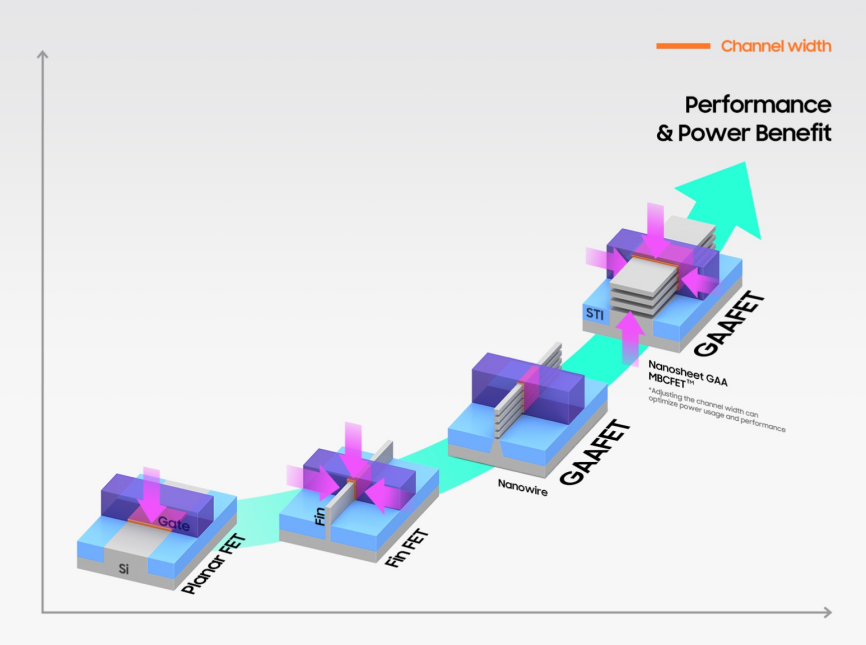

在6nm之后,三星還希望今年推出5nm EUV工藝,臺積電也是預定今年上半年量產5nm EUV工藝的,這樣一來三星總算上追上臺積電的工藝進度了,不過三星依然沒有公布5nm的客戶是誰。三星真正有希望超越臺積電的工藝是3nm,他們是第一家官宣使用全新GAA晶體管的,在3nm節點將會用GAA環繞柵極晶體管取代FinFET晶體管,三星希望2021年量產3nm工藝,而今年上半年完成3nm工藝開發。

(責任編輯:fqj)

-

芯片

+關注

關注

459文章

51897瀏覽量

433347 -

三星電子

+關注

關注

34文章

15885瀏覽量

181980

發布評論請先 登錄

相關推薦

三星3nm良率僅20%,仍不放棄Exynos 2500處理器,欲打造“十核怪獸”

三星在4nm邏輯芯片上實現40%以上的測試良率

千億美元打水漂,傳三星取消1.4nm晶圓代工工藝

千億美元打水漂,傳三星取消1.4nm晶圓代工工藝?

臺積電產能爆棚:3nm與5nm工藝供不應求

三星電子:18FDS將成為物聯網和MCU領域的重要工藝

評論