引言

現在,各種系列的傳輸設備或傳輸系統均使用價格便宜、取材方便的雙絞線。來傳輸高質量的視頻信號、音頻信號和控制數據。且其傳輸距離可選。雖然使用品牌系列雙絞線所組成的傳輸系統具有獨特亮度/色度處理、多級瞬態沖擊保護及超強的干擾抑制能力,但在數據高速傳輸中,其高可靠性技術指標卻并不能符合要求,其所面臨的問題是如何應用先進的技術來保證數據在雙絞線纜中的高速傳輸。而將低電壓差分信號(LVDS)串行器一解串器用于雙絞線電纜數據高速傳輸系統不失為一種新技術,MAXIM公司的MAX9205/MAX9206正是利用這種技術完成了高頻信號的遠端傳輸。

1、 LVDS技術及其優勢

LVDS接口又稱RS-644總線接口,是20世紀90年代出現的一種數據傳輸和接口技術。LVDS是一種小振幅差分信號技術,使用非常低的幅度信號(約350 mV),它通過一對差分PCB走線或平衡電纜來傳輸數據。其單個信道傳輸速率可達到每秒數百兆比特。其特有的低振幅及恒流源驅動方式只產生極低的噪聲,且其功耗非常小。其傳輸介質可以是銅質的PCB連線,也可以是平衡電纜。

LVDS技術和其它接口相比。有著很大的優勢,主要表現在下面幾個方面:

(1)高速率

由于LVDS邏輯狀態間的電壓變化僅為300mV,因而能非常快地改變狀態,從而實現高速率。

(2)低功耗

隨著工作頻率的增加,LVDS的電源電流仍保持平坦,而CMOS和TTL技術的電源電流則會隨頻率增加而指數上升,這得益于使用恒流線路驅動器。LVDS的電流源可把輸出電流限制到約3.5mA,同時也能限制跳變期間產生的任何尖峰電流。這樣,在得到高達1.5 Gbps的高數據率的同時卻不明顯增加功耗。恒流驅動輸出還能容忍傳輸線的短路或接地而不會產生熱問題。由于LVDS降低了終端電阻壓降,因此也降低了電路的總功耗。

(3)噪聲性能好

LVDS產生的電磁干擾很低,這是因為采用了低電壓擺幅、低邊沿速率、奇模式差分信號、恒流驅動器的原因。其Icc尖峰只產生很低的輻射。通過減小電壓擺幅和電流能量,LVDS可把場強減到了最小;其差分驅動器還引入了奇模式傳輸,即等量方向相反的電流分別在傳輸線上傳輸。以形成電流環路。從而使電流回路產生最低的電磁干擾;在差分信號的傳輸中,由于差分接收器只響應正負輸入之差,因此當噪聲同時出現在兩個輸入中時,其差分信號的幅度并不受影響。

(4)具有故障安全(fail-safe)特性

由于恒流式驅動不會對系統造成任何損害,所以,LVDS驅動器可以帶電插拔。LVDS的另一特點是接收器的故障保護功能,LVDS接收器在內部提供了可靠性線路。故可保證在接收器輸入懸空、短路以及接收器輸入處于驅動器三態輸出或驅動器供電終止等情況下的可靠輸出(約定為“1”),從而防止輸出產生振蕩。

(5)集成能力強

由于可在標準的CMOS工藝中實現高速LVDS,故采用LVDS模擬電路集成復雜的數字功能是非常有利的。

基于LVDS技術的眾多優點。面向LVDS的電路模塊越來越多。本文的LVDS串行器/解串器MAX9205/MAX9206就是其中最典型的一對器件。

2 、MAX9205和MAX9206概述

MAX9205和MAX9206是美信公司推出的一組差分信號芯片組。其中MAX9205可將1O位并行COM數據或TTL數據轉換成具有內嵌時鐘的高速串行數據流;MAX9206則是可接收該串行數據流并將它們轉換為并行數據的解串器。同時又可以重建并行時鐘。該器件組進行數據轉換采用的是內嵌時鐘,這樣就可有效的解決由于時鐘與數據的不嚴格同步而制約高速傳輸的瓶頸問題。MAX9205/MAX9206的內部結構及應用方法如圖1所示。

2.1 MAX9205和MAX9206的工作原理

MAX9205 LVDS串行器和MAX9206 LVDS解串器能夠通過差分特性阻抗為100 Ω的串行點對點鏈路來傳輸高速數據。MAX9205和MAX9206的并行時鐘頻率范圍為16~40 MHz。在數據轉換的時候,串行器元件內部將自動加上兩個數據位,即在并行送入的10位數據中加上一個起始位(1)和一個終止位(0),這樣,串行器輸出就形成了一個12位的串行數據流,而解串器在接收數據的同時,則根據接收數據終止位和起始位之間的上升沿來恢復并行時鐘頻率。

2.2 MAX9205/MAX9206的工作模式

MAX9205和MAX9206具有初始化、同步模式、數據傳輸模式和節電模式這四種工作狀態.現分別介紹如下:

(1)初始化

上電后,各個管腳的輸出為高阻狀態.之后啟動鎖相環工作并跟隨本地時鐘,一旦鎖存時鐘信號后,就可以準備發送數據信號。

(2)同步模式

MAX9205具有兩個同步模式選擇位SYNC1和SYNC2,初始化之后就可以根據這兩位的狀態來決定芯片是進行同步模式還是數據傳輸模式。當兩者之中有一個管腳持續6個周期的高狀態后.芯片就會傳輸1024個周期的同步信號。同步信號是由6個連續的0和6個連續的1組成的串行數據流。

(3)數據傳輸模式

初始化完成后,若同步管腳都為0。則進行數據傳輸。此時串行器用TCLK端選通輸入數據并存入10位輸入鎖存器。發送時從中取出數據,再加上作為內嵌時鐘的起始位(1)和終止位(0)各一位,將總共12位數據順序發送至串行差分端口,然后由解串器將接收到的串行數據轉換為10位并行數據并存入輸出鎖存器,同時從內嵌時鐘中恢復并重建并行時鐘,并以此時鐘來選通輸出鎖存器及輸出數據。

(4)節電模式

串行器和解串器均可以工作在節電模式。當沒有數據傳輸時,可以通過設置管腳pwden將芯片置于節電模式。這時鎖相環停止工作,輸出為三態,電流也降低到幾個毫安。

3 、遠端高速數據傳輸系統的實現

在高速遠端數據傳輸中,信號的傳輸質量是整個系統功效的一個測試標準,由于高頻率信號的變換較快,加上外部噪聲和傳輸線路的衰減以及器件本身的限制等影響,高速數據系統的設計一直是工程上的一個難題。綜合考慮這些因素,本系統采用串行器/解串器的方法來進行數據的傳輸設計。

3.1 系統工作流程

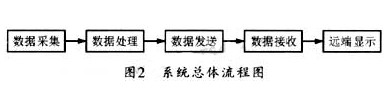

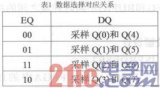

本設計是一個遠端顯示的系統設計,要求將接收并處理過的數據在遠端顯示出來。其具體過程是使發射系統每3 600μs發送一幀數據,由數據采集系統對外部信號進行A/D采樣.再送入DSP中進行信號處理以得到信號的某些特征。然后由DSP將處理過的信息發送給FPGA.這些處理過的數據是6000個八位的視頻數據,速率為2MB/s。FPGA先將接收到的數據存儲在雙口RAM中。然后從雙口RAM中將數據送入串行器。并通過串行器將信號發送給傳輸線,遠端的接收系統再通過解串器進行一個反過程以將信號恢復為八位并行數據,最后送給顯示系統。其總體流程如圖2所示。

3.2 數據發送及接收的實現

數據的采集及處理主要是根據具體的系統要求來獲取信號的某些特征。這里著重介紹了信號的發送和接收部分以及其中用到的LVDS技術。

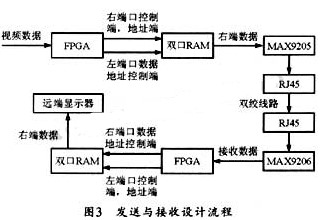

傳統的高速信號送入雙絞線路進行遠端傳輸的主要是利用軟件方法將并行信號轉換為串行信號,然后經過差分芯片將這種單路信號轉換為兩路信號,再送入雙絞線路進行傳輸,最后在接收端將接收到的信號采用軟件將串行轉換為并行。這種方法結構簡單,軟件設計也較為容易。但是,這種方法存在數據和時鐘的同步問題,即在接收端很難提取到時鐘信號。從而會導致傳輸的失敗。基于此,設計時可選擇串行器解串器的方法,即采用元件的內嵌時鐘來自動恢復。實踐證明:這種方法的確能夠很好的恢復發送端的信號。發送過程和接收過程的流程圖如圖3所示。

目前串行器解串器產品發展十分迅速.有些產品已經突破700 Mbps的傳輸速率。因此,對于更高傳輸要求的系統設計.這種方法不失為一種很好的解決方案。

3.3 設計中應注意的問題

由于MAX9205/MAX9206工作頻率較高,可以實現160~400 Mbps的數據傳輸率,因此。其應用要求也比較嚴格。下面是在系統設計和應用過程中需要注意的問題:

(1)由于串行器和解串器都存在兩種電平信號(TTL乘LVDS),所以在電路板設計過程中,推薦將這兩種電平信號放置在不同的層面進行走線,并在中間用電源層或地層隔開,以防兩種電平信號之間出現干擾。

(2)由于信號的頻率較高,所以LVDS信號走線要盡量短,并且兩路差分信號走線距離要盡量相等,以防兩路信號存在相位差異。減小信號的傳輸誤差。

(3)系統的時鐘信號要求比較嚴格,MAX9205要求時鐘的抖動最大為150 ps,時鐘轉換時間最大為6 ns,因此,在器件的選擇以及時鐘線的走線上要謹慎處理。盡量保證時鐘信號的質量。

(4)串行器和解串器的應用有嚴格要求,阻抗匹配問題也要注意,以保證接收端能夠接收到正確的信號。

(5)雙絞線傳輸媒介的平衡性也是決定信號質量的一個重要因素。

4 、結束語

LVDS技術是一種低擺幅的電壓差分信號,由于其抗噪聲能力較強、功耗較低,目前LVDS技術能在廣泛的應用領域里解決高速數據傳輸問題。近年來,隨著體系結構技術和半導體工藝的發展,IC芯片上的時鐘頻率提高很快。但這也對芯片、電路底版、機箱以及機柜之間的互連速度提出了更迫切的要求。現代高性能微處理器的速度已經突破了1 GHz,芯片間的傳輸速率也達到了幾百兆赫茲。但是,常規的CMOS和TTL由于自身的電路特性和信號特點。很難在芯片外進行200 MHz以上的信號傳輸。因此,大多數的微處理器的外部工作頻率都降低到內部的一半,甚至更低。這就大大限制了微處理器高速性能的發揮。對于這個問題,LVDS技術也可作為一個有效的解決方法。因此,LVDS技術必將具有廣泛的應用前景。基于LVDS技術電路的模塊也必將得到更廣泛的應用。

責任編輯:gt

-

FPGA

+關注

關注

1629文章

21729瀏覽量

603016 -

pcb

+關注

關注

4319文章

23081瀏覽量

397525 -

lvds

+關注

關注

2文章

1043瀏覽量

65795

發布評論請先 登錄

相關推薦

FPGA編程LVDS信號圖像處理技術

labview FPGA技術的優勢

LVDS接口技術在DAC系統中的應用

基于FPGA技術和LabVIEW圖形化系統實現大型射頻數據共享

遠端射頻系統為網絡運營商提供了明顯的成本和技術優勢

基于FPGA和PCI9054的LVDS數據通信卡的設計

基于FPGA的總線型LVDS通信系統設計

基于FPGA的LVDS過采樣技術研究并用Xilinx評估板進行驗證

LVDS技術的應用優勢及基于FPGA實現遠端顯示系統的設計

LVDS技術的應用優勢及基于FPGA實現遠端顯示系統的設計

評論