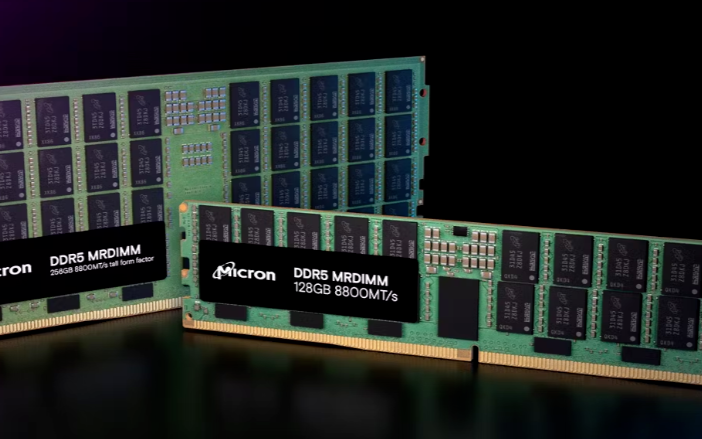

美光于前日宣布已經(jīng)開始向業(yè)界中的核心客戶出樣DDR5內(nèi)存(RDIMM)了,目前他們在DDR5內(nèi)存上面使用的是自家最新的1z nm工藝。

JEDEC于2016年就開始制定DDR5 SDRAM規(guī)范了,不過到目前為止,DDR5標(biāo)準(zhǔn)仍然處于完善期,JEDEC還沒有公布它的最終版本,預(yù)計(jì)它將會在今年正式完成DDR5標(biāo)準(zhǔn)的制定。反而是LPDDR5快了一步,在去年2月份標(biāo)準(zhǔn)就已經(jīng)正式公布,并且有廠商已經(jīng)推出了實(shí)際產(chǎn)品,并且在今年已經(jīng)有移動處理器支持它了。

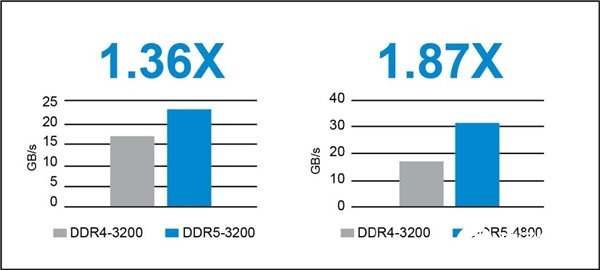

美光的DDR5技術(shù)文檔也得以讓我們一窺DDR5內(nèi)存的特性。首先,在同樣的等效頻率下,DDR5內(nèi)存能夠提供更高的有效帶寬,比如同樣處于3200MT/s下,DDR5-3200的有效帶寬比DDR4-3200的要高出36%;其次是DDR5(在JEDEC標(biāo)準(zhǔn)范圍內(nèi))的等效頻率能夠去到更高,可以達(dá)到DDR5-6400,而在DDR5-4800時(shí),其有效帶寬就已經(jīng)是DDR4-3200的1.87倍了。

最近幾年CPU的核心數(shù)在顯著的增多,不止是服務(wù)器端,桌面端在Coffee Lake和Zen、Zen 2的推動下也是有越來越多的核心,核心數(shù)是多了,但是內(nèi)存帶寬仍然只有這么點(diǎn),這使得每個(gè)核心在同時(shí)間可以吃到的內(nèi)存帶寬在減少,這將給處理器整體的性能帶來負(fù)面影響,目前在桌面端它表現(xiàn)的還不是非常明顯,可能也就是Ryzen 9 3950X這種用著雙通道DDR4內(nèi)存的16核處理器上能夠看到。

美光還在計(jì)劃新的工藝節(jié)點(diǎn),在目前的1z nm節(jié)點(diǎn)之后,他們規(guī)劃了1α、1β和1γ,將繼續(xù)提升內(nèi)存的存儲密度,這也將是DDR5的一個(gè)重要特征。

責(zé)任編輯:wv

-

內(nèi)存

+關(guān)注

關(guān)注

8文章

3105瀏覽量

74945 -

美光

+關(guān)注

關(guān)注

5文章

721瀏覽量

52083 -

DDR5

+關(guān)注

關(guān)注

1文章

441瀏覽量

24667

發(fā)布評論請先 登錄

DDR4漲價(jià)20%,DDR5上調(diào)5%!

不挑硬件,親民之選,亦逍遙DDR5內(nèi)存裝機(jī)評測

創(chuàng)見推出DDR5 6400 CUDIMM內(nèi)存條

國產(chǎn)DDR5內(nèi)存上市,內(nèi)存市場價(jià)格戰(zhàn)一觸即發(fā)

雷克沙推出全新戰(zhàn)神之翼系列DDR5內(nèi)存條

DDR5內(nèi)存與DDR4內(nèi)存性能差異

瑞薩電子發(fā)布全新DDR5 MRDIMM內(nèi)存接口芯片組

DDR5內(nèi)存的工作原理詳解 DDR5和DDR4的主要區(qū)別

美光發(fā)布新型CUDIMM與CSODIMM內(nèi)存產(chǎn)品

DDR5內(nèi)存面臨漲價(jià)潮,存儲巨頭轉(zhuǎn)向HBM生產(chǎn)

Introspect DDR5/LPDDR5總線協(xié)議分析儀

DDR5 MRDIMM內(nèi)存標(biāo)準(zhǔn)將發(fā),存儲廠商方案先行

DDR5內(nèi)存條上的時(shí)鐘走線

0706線下活動 I DDR4/DDR5內(nèi)存技術(shù)高速信號專題設(shè)計(jì)技術(shù)交流活動

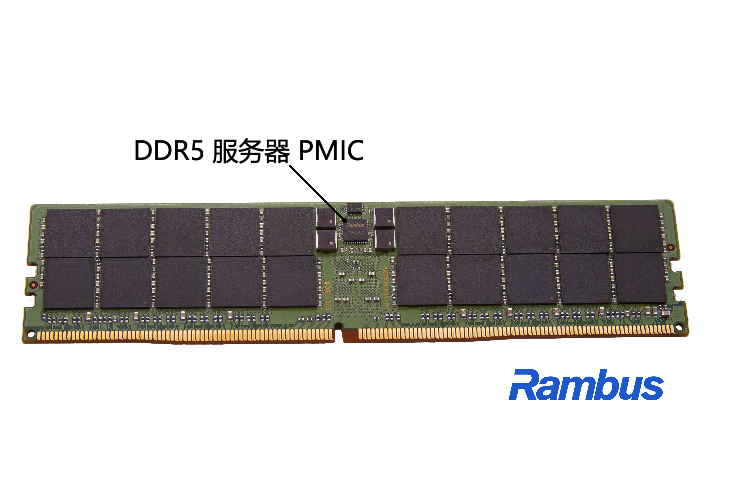

Rambus 通過 DDR5 服務(wù)器 PMIC 擴(kuò)展適用于高級數(shù)據(jù)中心內(nèi)存模塊的芯片組

評論