嵌入式開發(fā)中,大家免不了需要仿真調(diào)試代碼,尤其是當(dāng)應(yīng)用工程功能邏輯復(fù)雜到一定程度時,免不了在寫代碼時會引入一些邏輯 bug,僅靠代碼審查有時候并不一定能排除所有 bug,所以在線調(diào)試便成為排除 bug 最有效直接的方式,今天我們要聊的是調(diào)試?yán)镒罨A(chǔ)的東西,即接口標(biāo)準(zhǔn)。ARM 內(nèi)核原生支持 2 種業(yè)界通用的接口標(biāo)準(zhǔn),分別是 JTAG 和 SWD。本節(jié)課痞子衡先給大家詳細(xì)講講 JTAG 接口。

一、JTAG 接口標(biāo)準(zhǔn)

JTAG 全稱“Joint Test Action Group”,既是個標(biāo)準(zhǔn)也是個組織,這是個由幾家主要的電子制造商(IBM、AT&T、TI、Philips 等)成立于 1985 年的組織,這個組織成立的目的是發(fā)起制訂一種 PCB和芯片測試標(biāo)準(zhǔn)。

JTAG 標(biāo)準(zhǔn)于 1990 年被 IEEE 批準(zhǔn)為 IEEE1149.1 測試訪問端口和邊界掃描結(jié)構(gòu)標(biāo)準(zhǔn)。JTAG 標(biāo)準(zhǔn)規(guī)定了進行邊界掃描所需要的硬件和軟件,主要應(yīng)用于電路的邊界掃描測試和可編程芯片的在線系統(tǒng)編程。

1.1 IEEE 1149.1 標(biāo)準(zhǔn)

IEEE 1149.1 工作組 http://grouper.ieee.org/groups/1149/1/

最初版手冊 1149.1-1990 http://standards.ieee.org/findstds/standard/1149.1-1990.html

最新版手冊 1149.1-2013 http://standards.ieee.org/findstds/standard/1149.1-2013.html

1.2 JTAG 接口信號

JTAG 接口,總稱測試訪問接口 TAP(Test Access Port),使用如下信號來實現(xiàn)邊界掃描操作:

TCK(測試時鐘):同步內(nèi)部狀態(tài)機操作的時鐘信號。

TMS(測試模式選擇):控制內(nèi)部狀態(tài)機轉(zhuǎn)換的模式信號(TCK 上升沿采樣)。

TDI(測試數(shù)據(jù)輸入):移入器件測試或編程邏輯的數(shù)據(jù)(TCK 上升沿采樣)。

TDO(測試數(shù)據(jù)輸出):移出器件測試或編程邏輯的數(shù)據(jù)(TCK 下降沿采樣)。

除了以上信號線外,還有 1 個可選的信號:

TRST(測試重置):重置 TAP 控制器的狀態(tài)機的復(fù)位信號。

1.3 JTAG 系統(tǒng)內(nèi)部構(gòu)造

JTAG 系統(tǒng)內(nèi)部最基本的單元是邊界掃描單元(其掃描獲取的值存在邊界掃描寄存器 BSR(Boundary Scan Register)中),每個邊界掃描單元都位于目標(biāo)器件的邊界上,所以很多時候 JTAG 測試也被稱為邊界掃描。

所有目標(biāo)器件核心邏輯與針腳之間的信號都會被串聯(lián)的邊界掃描單元所攔截。正常運行時,這些邊界掃描單元是不可見的。但是,在測試模式下這些單元可以被用來設(shè)置 / 讀取目標(biāo)器件針腳或核心邏輯的值。

除了上述 BSR 之外,JTAG 系統(tǒng)還需要以下 3 個寄存器:

指令寄存器:存儲當(dāng)前的指令,指令內(nèi)容被 TAP 控制器用來決定如何處理接收到的信號。

旁路寄存器(BYPASS):把信息從 TDI 傳到 TDO 的單位寄存器。

識別碼寄存器(IDCODES):含有器件的識別碼和版本序號,該信息可以使器件和它的邊界掃描描述語言(BSDL)文件相關(guān)聯(lián)。

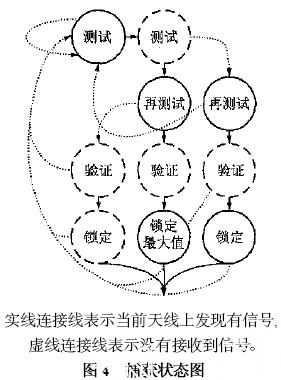

JTAG 系統(tǒng)最核心的是 TAP 控制器,TAP 控制器被設(shè)計用來與 JTAG 系統(tǒng)內(nèi)部寄存器相互動,TAP 控制器是一個被 TMS 信號控制轉(zhuǎn)換的同步狀態(tài)機,控制著 JTAG 系統(tǒng)的行為。

如上圖所示,TAP 控制器的內(nèi)部狀態(tài)機一共 16 個狀態(tài),關(guān)于各個狀態(tài)具體含義可查閱 IEEE1149.1 手冊。TAP 控制器的基本功能是產(chǎn)生 BSR 和指令寄存器正常工作所需要的時鐘和控制信號,其主要功能有以下幾點:

提供信號將指令裝入指令寄存器。

提供信號將輸入數(shù)據(jù)從 TDI 管腳移入內(nèi)部寄存器、把輸出數(shù)據(jù)從內(nèi)部寄存器移出到 TDO 管腳。

執(zhí)行相應(yīng)功能,如捕獲、移位和更新數(shù)據(jù)等。

指令寄存器是用來存儲需要解釋執(zhí)行的指令的,IEEE 1149.1 標(biāo)準(zhǔn)規(guī)定了 JTAG 兼容器件必須要具備的指令:

BYPASS:用單一單元旁路寄存器傳送數(shù)據(jù),縮短 JTAG 鏈上不必要的掃描鏈路。

EXTEST:將已知值(存在 BSR)驅(qū)動到芯片針腳上。

SAMPLE/PRELOAD:將捕獲到的芯片針腳值裝入 BSR。

除了必備的指令外,IEEE 1149.1 標(biāo)準(zhǔn)還規(guī)定了如下可選的指令:

IDCODE:將 IDCODES 寄存器中的數(shù)據(jù)移出。

INTEST:將已知值(存在 BSR)驅(qū)動到芯片核心邏輯上。

RUNBIST:當(dāng) TAP 進入測試運行空閑狀態(tài)時,芯片進行自檢。

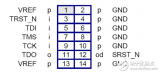

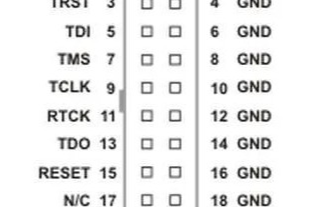

1.4 JTAG 調(diào)試工具 pinout

通常支持 JTAG 接口的調(diào)試編程工具其實只是利用了 JTAG 技術(shù)的四線 TAP 通信協(xié)議,而除了標(biāo)準(zhǔn) TAP 信號線外,有時還加入其他輔助信號線構(gòu)成完整 pinout,對于 ARM JTAG 調(diào)試工具來說,有兩種比較通用的 pinout 標(biāo)準(zhǔn),即 ARM20 JTAG header 和 ARM14 JTAG header:

上述兩種 ARM JTAG header 中除了標(biāo)準(zhǔn) TAP 信號線外,其他輔助信號線含義如下:

二、JTAG 接口進階

前面講完了 JTAG 基礎(chǔ)知識,下面痞子衡再給大家多介紹一些 JTAG 相關(guān)的“黑科技”。

2.1 BSDL 文件

現(xiàn)如今支持 JTAG 接口的芯片越來越多,為了統(tǒng)一各芯片廠商的具體 JTAG 實現(xiàn),促進整個電子行業(yè)的一致性,IEEE1149.1 標(biāo)準(zhǔn)制訂了 BSDL 語言規(guī)范。BSDL 是 JTAG 設(shè)備的標(biāo)準(zhǔn)建模語言,它的語法是 VHDL 的子集,是對 JTAG 器件的邊界掃描特性的描述,主要用來溝通芯片廠商、用戶與測試工具之間的聯(lián)系。

開源的 JTAG BSDL 庫網(wǎng)站(http://bsdl.info/),涵蓋主流廠商的主流芯片的 BSDL 文件

痞子衡隨便找一款芯片的 BSDL 文件(Freescale K60_1M(K24_144QFP))簡單分析下:

2.2 JTAG 菊花鏈

當(dāng)你的系統(tǒng)中有多個 JTAG 設(shè)備時,為解決 JTAG 口過多占用 PCB 的問題,JTAG 支持如下菊花鏈方式連接(在 FPGA 應(yīng)用尤其廣泛):

從上圖可以看出 TMS、TCK 是一主多從并聯(lián)的結(jié)構(gòu)(設(shè)備過多時 TMS,TCK 電路需加緩沖器(如 74LVC245)增加驅(qū)動能力);TDI、TDO 是一主一從串聯(lián)的結(jié)構(gòu),這種菊花鏈方式使得 PCB 上只需要一個 JTAG 接口便可以訪問所有 JTAG 設(shè)備。

-

嵌入式

+關(guān)注

關(guān)注

5082文章

19104瀏覽量

304816 -

接口

+關(guān)注

關(guān)注

33文章

8575瀏覽量

151019 -

JTAG

+關(guān)注

關(guān)注

6文章

399瀏覽量

71673

發(fā)布評論請先 登錄

相關(guān)推薦

四種嵌入式arm調(diào)試方法介紹

嵌入式系統(tǒng)交叉調(diào)試原理和方法

串口串行數(shù)據(jù)接口標(biāo)準(zhǔn)介紹

JTAG接口標(biāo)準(zhǔn)是什么?

一種嵌入式系統(tǒng)實現(xiàn)的JTAG調(diào)試器

jtag接口是什么_jtag接口定義

兩種遠(yuǎn)程調(diào)試嵌入式系統(tǒng)的介紹

嵌入式教程之嵌入式系統(tǒng)基礎(chǔ)的詳細(xì)資料說明

嵌入式軟件的開發(fā)流程_嵌入式軟件的調(diào)試

調(diào)試接口SWD和JTAG的區(qū)別

嵌入式調(diào)試?yán)锏慕涌跇?biāo)準(zhǔn)JTAG詳細(xì)介紹

嵌入式調(diào)試?yán)锏慕涌跇?biāo)準(zhǔn)JTAG詳細(xì)介紹

評論