3月23日的GTC大會可能是NVIDIA正式揭曉新一代GPU架構(gòu)的窗口時間。本周,名為KittyCorgi的爆料新人公布了不少Ampere(安培)核心的技術(shù)資料,雖說真實性還有待作證,但也不妨先瞧一瞧。

依據(jù)這份爆料,Ampere GPU核心面積高達826mm2,如果基于7nm打造的話,晶體管規(guī)模將相當(dāng)恐怖。

具體到內(nèi)部,對應(yīng)RTX 3080 Ti的“GA103”核心分為6組GPC單元,每組GPC擁有10個SM單元,一共是60個SM單元,3840個CUDA(若是一個SM單元增加到128個CUDA,那就是7680,基于核心面積,后者可能性倒是更大),顯存位寬320bit。此前,RTX 2080 Ti的TU102是72個SM單元,有效68個,總計4608個CUDA。

對應(yīng)RTX 3080的“GA104”核心同樣是6組GPC,每組GPC削減為8個SM單元,一共是48個SM,3072或6144個CUDA,256bit顯存位寬,都支持PCIe 4.0。

回到SM單元內(nèi)部,INT32單元不變,F(xiàn)P32規(guī)模翻倍,Tensor Core翻倍,L1增大,光追單元升級為RT Core Advanced。

期待老黃盡快揭曉Ampere、Hopper……

責(zé)任編輯:wv

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請聯(lián)系本站處理。

舉報投訴

相關(guān)推薦

雪崩晶體管(Avalanche Transistor)是一種具有特殊工作特性的晶體管,其核心在于其能夠在特定條件下展現(xiàn)出雪崩倍增效應(yīng)。以下是對雪崩晶

![的頭像]() 發(fā)表于

發(fā)表于 09-23 18:03

?979次閱讀

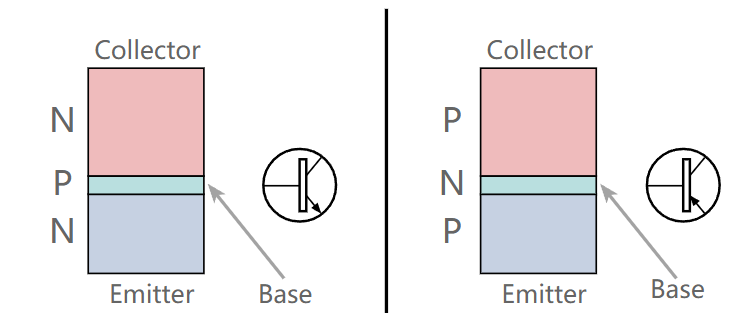

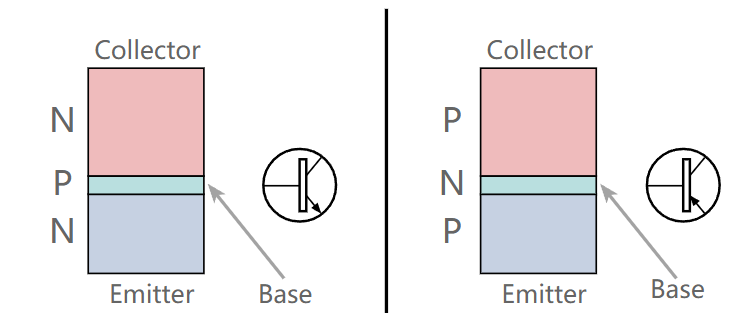

晶體管作為電子電路中的核心元件,其基本工作模式對于理解其工作原理和應(yīng)用至關(guān)重要。晶體管的工作模式主要可以分為兩大類:放大模式和開關(guān)模式。這兩種模式基于晶體管內(nèi)部PN結(jié)的特性,通過控制輸

![的頭像]() 發(fā)表于

發(fā)表于 09-13 16:40

?941次閱讀

CMOS晶體管尺寸規(guī)則是一個復(fù)雜且關(guān)鍵的設(shè)計領(lǐng)域,它涉及到多個方面的考量,包括晶體管的性能、功耗、面積利用率以及制造工藝等。以下將從CMOS晶體管

![的頭像]() 發(fā)表于

發(fā)表于 09-13 14:10

?2042次閱讀

NMOS晶體管和PMOS晶體管是兩種常見的金屬氧化物半導(dǎo)體場效應(yīng)晶體管(MOSFET)類型,它們在多個方面存在顯著的差異。以下將從結(jié)構(gòu)、工作原理、性能特點、應(yīng)用場景等方面詳細闡述NMOS晶體管

![的頭像]() 發(fā)表于

發(fā)表于 09-13 14:10

?3730次閱讀

一、引言 有關(guān)系。隨著集成電路技術(shù)的飛速發(fā)展,芯片晶體管作為電子設(shè)備的核心元件,其性能的優(yōu)化和制造技術(shù)的提升成為了行業(yè)關(guān)注的焦點。在晶體管的眾多設(shè)計參數(shù)中,深度和寬度是兩個至關(guān)重要的因

![的頭像]() 發(fā)表于

發(fā)表于 07-18 17:23

?709次閱讀

晶體管是一種半導(dǎo)體器件,廣泛應(yīng)用于電子電路中。晶體管的工作原理基于半導(dǎo)體材料的導(dǎo)電特性,通過控制基極電流來調(diào)節(jié)集電極電流,從而實現(xiàn)放大、開關(guān)等功能。晶體管的電流關(guān)系是其

![的頭像]() 發(fā)表于

發(fā)表于 07-09 18:22

?1708次閱讀

PNP晶體管是一種雙極性晶體管,用于電子電路中放大、開關(guān)和控制電流的器件。與NPN晶體管相對應(yīng),PNP晶體管的結(jié)構(gòu)特點在于其三個不同的半導(dǎo)體

![的頭像]() 發(fā)表于

發(fā)表于 07-01 17:45

?2666次閱讀

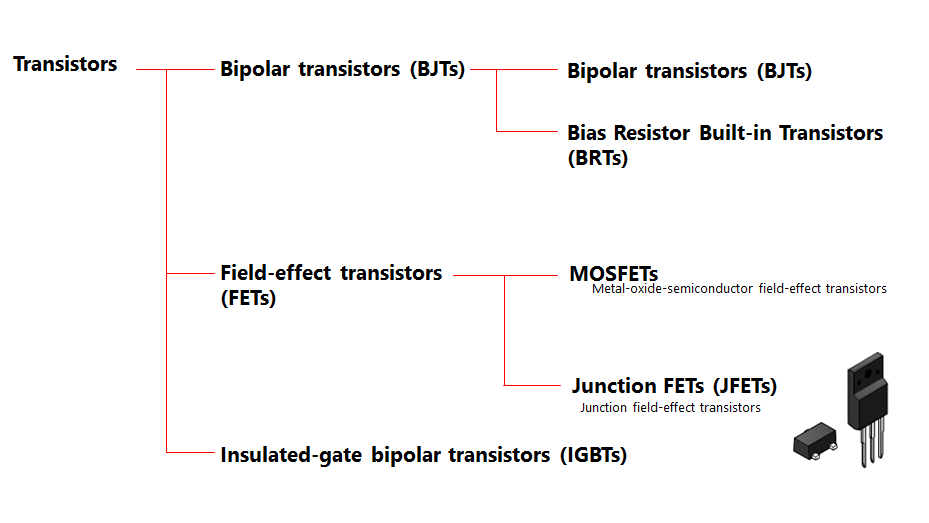

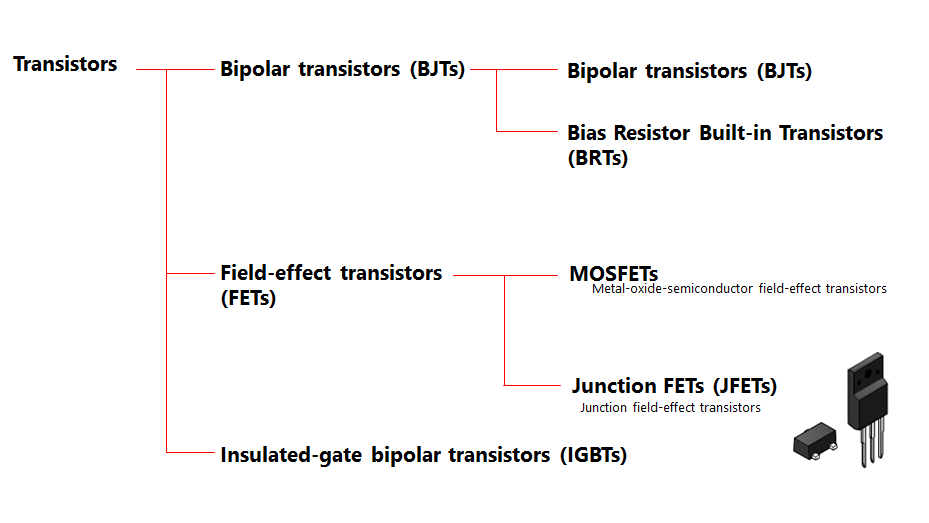

堅實的基礎(chǔ),更為后來的集成電路、大規(guī)模集成電路乃至超大規(guī)模集成電路的誕生和發(fā)展提供了可能。本文將詳細探討晶體管的分類及其作用,以期為讀者提供一個全面且深入的理解。

![的頭像]() 發(fā)表于

發(fā)表于 05-22 15:17

?1009次閱讀

,推理能力提升 15 倍

GB200由兩個B200Blackwell GPU和一個基于Arm的Grace CPU組成,采用[臺積電]4納米工藝制程,共有2080億個[晶體管],其AI性能為每秒20

發(fā)表于 05-13 17:16

陸行之表示,相比于其前身“Hopper”100的800億晶體管,“Blackwell”100擁有的2080億晶體管數(shù)量超過了前者1280億。此外,盡管兩款GPU均采用臺積電的4納米技術(shù)加工,但“Blackwell”100通過封裝

![的頭像]() 發(fā)表于

發(fā)表于 03-20 09:24

?748次閱讀

蘋果M3芯片的晶體管數(shù)量相當(dāng)可觀,相比前代產(chǎn)品有了顯著的提升。這款芯片搭載了高達250億個晶體管,比M2芯片多出50億個,這樣的設(shè)計使得M3

![的頭像]() 發(fā)表于

發(fā)表于 03-11 16:45

?924次閱讀

達林頓晶體管(Darlington Transistor)也稱為達林頓對(Darlington Pair),是由兩個或更多個雙極性晶體管(或其他類似的集成電路或分立元件)組成的復(fù)合結(jié)構(gòu)。通過這種結(jié)構(gòu),第一個雙極性

![的頭像]() 發(fā)表于

發(fā)表于 02-27 15:50

?5517次閱讀

晶體管并聯(lián)時,當(dāng)需要非常大的電流時,可以將幾個晶體管并聯(lián)使用。因為存在VBE擴散現(xiàn)象,有必要在每一個晶體管的發(fā)射極上串聯(lián)一個小電阻。電阻R用

發(fā)表于 01-26 23:07

管子多用于集成放大電路中的電流源電路。

請問對于這種多發(fā)射極或多集電極的晶體管時候該如何分析?按照我的理解,在含有多發(fā)射極或多集電極的晶體管電路時,如果多發(fā)射極或多集電極的每一極分別接到獨立的電源回路中

發(fā)表于 01-21 13:47

盡管使用帶有晶體管的分立電子元件會使用更多元件,但可以定制電路以提供所需的功能。因此,使用分立晶體管和一些附加電子元件的電路是電子電路設(shè)計的核心。

![的頭像]() 發(fā)表于

發(fā)表于 01-09 15:21

?1577次閱讀

曝NVIDIA新一代GPU晶體管規(guī)模將相當(dāng)恐怖 核心面積高達826mm2

曝NVIDIA新一代GPU晶體管規(guī)模將相當(dāng)恐怖 核心面積高達826mm2

評論