【嘉德點評】該項技術通過在編程期間估計多位快閃存儲器的BER,從而改進所述快閃存儲器的編程速度,大大提高其性能。

集微網(wǎng)消息,前不久鎧俠(原稱東芝存儲)半導體公司已研發(fā)出采用堆疊112層的3D NAND Flash產(chǎn)品,與目前96層的3D NAND產(chǎn)品相比,此次新產(chǎn)品的單位面積記憶容量提高約20%,除了鞏固和擴大SSD,PC,智能手機市場外,還將搶占5G、人工智能、自動駕駛等新市場需求。

NAND Flash是目前閃存中最主要的產(chǎn)品,具備非易失,高密度,低成本的優(yōu)勢,其陣列內(nèi)部包含由晶體管構成的行列單元。在利用NAND進行讀寫,即對芯片內(nèi)部編程操作時,需要將電壓脈沖施加到正在編程的晶體管,并將電荷注入到晶體管的柵極內(nèi)部。當使用最大電壓脈沖數(shù)目后,實際獲取的編程電壓仍未達到要求電壓,則對芯片編程失敗。

為描述NAND Flash存儲器的可靠性,需要提出一種方法高效而準確地估計存儲器中與編程單元相關的位錯誤率(BER),從而提高存儲器的性能,而現(xiàn)有的一些方法通過讀取編程到裝置中的數(shù)據(jù)與經(jīng)編程數(shù)據(jù)進行比較來估計位錯誤率,由于此過程中需要消耗大量時間,因此效率極低。

早在2018年7月18日,東芝存儲器(現(xiàn)稱鎧俠)就提出一項名為“用于估計NAND快閃存儲器的位錯誤率的快閃存儲器系統(tǒng)和方法”的發(fā)明專利(申請?zhí)枺?01810789084.X),申請人為東芝存儲器株式會社。

此發(fā)明專利涉及提到一種快閃存儲器系統(tǒng)和一種用于估計NAND快閃存儲器的位錯誤率的方法,通過在編程期間估計多位快閃存儲器的BER,從而改進所述快閃存儲器的編程速度。

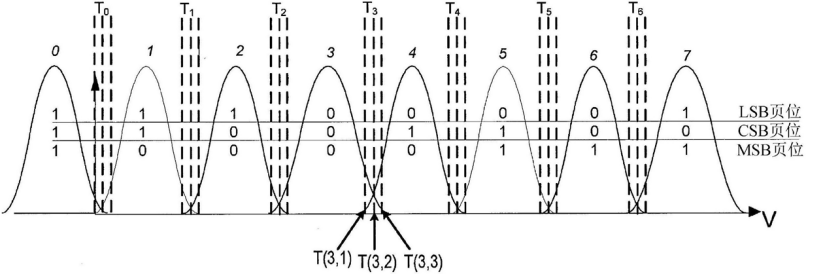

圖1

圖1是用于BER估計的三位每單元(bpc)快閃存儲器裝置的電壓閾值分布示意圖。通常來講,NAND單元重復的編程和擦除會致使電荷在存儲器單元中被捕獲,這些電荷可減少單元編程時間,且可在編程和讀取過程中引入錯誤,導致NAND快閃裝置的位錯誤率(BER)增大。此專利提出,針對每一電壓閾值設置三個相關的檢驗閾值,鄰近檢驗閾值之間的差值可為約50mV到100mV,并根據(jù)恰好在編程之后(這時估計BER)的每一程序等級的預期電壓閾值分布配置閾值差,利用這種增加每狀態(tài)檢驗電壓閾值的數(shù)目來改進所估計的BER的準確性。

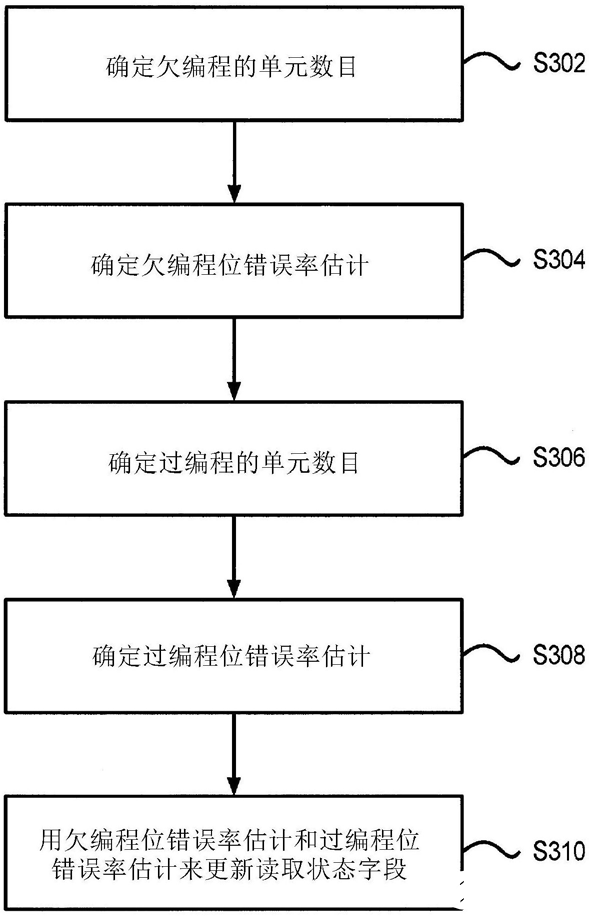

圖2

圖2是在圖1基礎上用于估計NAND快閃裝置BER的具體方法,采用編程-檢驗邏輯執(zhí)行,以在一或多個塊的編程期間估計NAND快閃裝置內(nèi)的一或多個塊的BER。首先步驟S302中確定與電壓閾值相關聯(lián)的欠編程單元數(shù)目,如圖1所示,由于每狀態(tài)有三個檢驗閾值狀態(tài),當單元被編程有第四狀態(tài)時,內(nèi)部邏輯可確定具有低于閾值電壓的單元數(shù)目。在步驟S304中確定針對每一電壓閾值的欠編程BER估計值passTHBER。接著在步驟S306中確定欠編程的單元的數(shù)目,具體表現(xiàn)為將塊內(nèi)每一單元處的電壓電平與三個指定檢驗閾值水平進行比較,以確定具有高于這些閾值中的每一者的電壓值的單元的數(shù)目。在步驟308中確定過編程的的BER估計,其值為與所有其它電壓閾值相關聯(lián)的BER值的最大值。最后在步驟S310中用所估計的欠編程的和過編程的BER估計來更新讀取狀態(tài)字段,并讀取狀態(tài)寄存器輸出BER估計,并在寄存器中做指示。

NAND Flash作為目前應用極為廣泛的非易失性存儲器,其性能的提高與成本的降低對未來自動駕駛、人工智能市場有著極大的推動作用,也必將促進半導體市場的創(chuàng)新活力與發(fā)展。

-

閃存

+關注

關注

16文章

1782瀏覽量

114895 -

存儲器

+關注

關注

38文章

7484瀏覽量

163765 -

東芝存儲

+關注

關注

0文章

6瀏覽量

3780

發(fā)布評論請先 登錄

相關推薦

預期提前,鎧俠再次加速,3D NAND準備沖擊1000層

【半導體存儲】關于NAND Flash的一些小知識

鎧俠投資360億日元研發(fā)CXL省電存儲器

鎧俠將開發(fā)新型CXL接口存儲器

三星與鎧俠計劃減產(chǎn)NAND閃存

鎧俠北上市NAND閃存新工廠竣工,預計2025年秋投產(chǎn)

鎧俠瞄準2027年:挑戰(zhàn)1000層堆疊的3D NAND閃存新高度

鎧俠結(jié)束NAND閃存減產(chǎn),工廠開工率已恢復至100%

鎧俠NAND閃存生產(chǎn)恢復

NAND存儲種類和優(yōu)勢

鎧俠半導體估計NAND快閃存儲器位錯誤率的專利

鎧俠半導體估計NAND快閃存儲器位錯誤率的專利

評論