前言

做深度學(xué)習(xí)加速器已經(jīng)兩年了,從RTL設(shè)計到仿真驗證,以及相應(yīng)的去了解了Linux驅(qū)動,深度學(xué)習(xí)壓縮方法等等。今天來捋一捋AI加速器都涉及到哪些領(lǐng)域,需要哪些方面的知識。可以用于AI加速器的主要有三種不同架構(gòu)的器件種類:CPU,GPU,AI芯片/FPGA。CPU是一個通用架構(gòu)芯片,其計算能力和數(shù)據(jù)帶寬相對受到限制,面對大計算量的深度學(xué)習(xí)就顯露出其缺點了。GPU含有大量的計算陣列,可以適用于大規(guī)模運算,而且其生態(tài)較為成熟和完整,所以現(xiàn)在包攬了所有的深度學(xué)習(xí)訓(xùn)練和絕大部分深度學(xué)習(xí)推理。要說有沒有缺陷,經(jīng)常被拿來比較的就是其功耗較大,而且并不是完全針對于深度學(xué)習(xí)網(wǎng)絡(luò)的結(jié)構(gòu),所以還并不能完全利用其計算和存儲資源。為了更有針對性的加速深度學(xué)習(xí)網(wǎng)絡(luò),AI芯片(FPGA)近兩年也出現(xiàn)了。Intel、阿里平頭哥、騰訊、百度等都開始設(shè)計自己的AI加速芯片,使用FPGA的有賽靈思、曠視科技等。FPGA用于深度學(xué)習(xí)加速和AI芯片的架構(gòu)具有通用性,兩者可以看做相同架構(gòu),只是用于不同硬件器件。而且通常AI芯片的前期驗證也是用FPGA完成的。這篇文章就捋一捋FPGA在做深度學(xué)習(xí)加速時需要的技能。

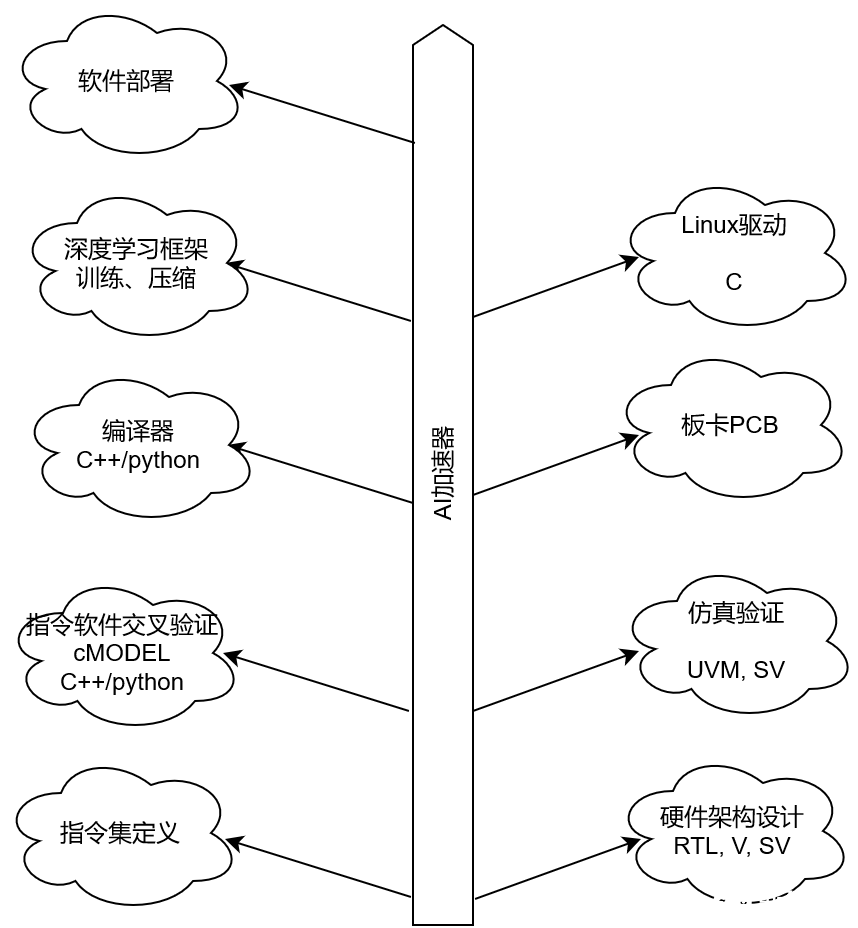

1. 一張圖

AI加速是一個同時涉及到軟件和硬件的領(lǐng)域,下面一張簡單的圖羅列了AI加速器所有知識。

2. RTL

RTL部分設(shè)計主要考慮到以下幾個方面:

1) 考察神經(jīng)網(wǎng)絡(luò)每個部分的計算量和參數(shù)數(shù)據(jù),選擇適合在FPGA上進(jìn)行加速的部分。比如對于CNN網(wǎng)絡(luò),卷積運算占據(jù)整個網(wǎng)絡(luò)的絕大部分計算,因此會占據(jù)FPGA中的絕大部分DSP資源。但是在卷積運算之間還存在激活函數(shù)、歸一化等操作,這些雖然計算量不大,但是會對整個加速形成瓶頸,因此如何能夠與卷積運算形成流水對性能影響也很大;

2) 設(shè)計加速算法。只要考慮好這兩點就解決了主要問題:一個是計算資源利用率,另外一個是miss ratio。計算資源利用率包括FPGA上空間資源利用率,還包括計算資源的時間利用率。空間利用率越高,說明算力越高,時間利用率越高表明有效計算越高,加速效果越好。Miss ratio反映了片上cache存儲的參數(shù)是否能夠及時供給計算使用。如果能及時供給使用,那么從片外加載數(shù)據(jù)的時間就可以被壓縮。

3) 架構(gòu)的通用性。基本上架構(gòu)都是基于指令集的,指令集主要依據(jù)加速器的計算核來定義的,算是復(fù)雜指令集。一個指令包含了參數(shù)的存儲位置,需要數(shù)量,計算方式等等。由于深度網(wǎng)絡(luò)操作數(shù)量比較單一,比如LSTM基本上就包括矩陣乘法、加法、向量乘法、激活等。大概也就有不超過10個指令就能涵蓋一個LSTM網(wǎng)絡(luò)了。為了適配這樣的指令,架構(gòu)大概包含以下結(jié)構(gòu):

外部總線:主要用于和外部ddr進(jìn)行數(shù)據(jù)交互。

內(nèi)部存儲:儲存要用到的參數(shù)和數(shù)據(jù),及時供給計算核。Cache緩存是為了解決讀取DDR帶寬瓶頸問題。

指令解析:獲取指令進(jìn)行解析,發(fā)送給相應(yīng)模塊進(jìn)行處理。

內(nèi)部總線:為每個計算核提供數(shù)據(jù)讀寫通路。

計算核:張量計算核,用于加速神經(jīng)網(wǎng)絡(luò)計算。

計算核互聯(lián)線:實現(xiàn)不同計算核之間的直接互聯(lián),可以實現(xiàn)不同計算核的pipeline。

Batch:包含了計算核、指令解析、計算核互聯(lián)線等。當(dāng)然如果內(nèi)部cache并不是用的很多,一個batch也可以包含有內(nèi)部cache。這些batch實際上可以看做神經(jīng)網(wǎng)絡(luò)運行的線程,多個batch就支持多線程神經(jīng)網(wǎng)絡(luò)計算。比如一個LSTM網(wǎng)絡(luò)可以在有batch=2的硬件上同時進(jìn)行兩個句子的運算。

線程控制:用于控制多batch操作。

3. 驗證

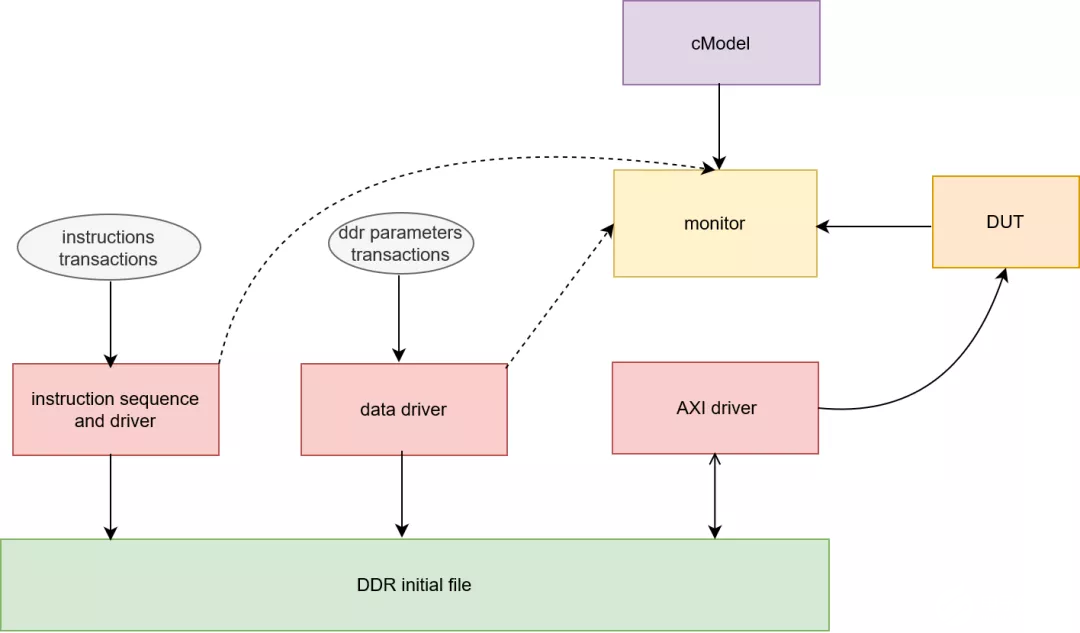

驗證主要包括兩個方面,一個是對指令集正確性進(jìn)行驗證,另外一個是對RTL代碼進(jìn)行仿真。指令集的驗證需要有一個CMODEL來對編譯器生成指令的正確性進(jìn)行校驗,校驗準(zhǔn)確才能夠給硬件使用。因為仿真環(huán)境也需要隨機(jī)化指令來對RTL代碼進(jìn)行校驗,所以cmodel也會用于仿真環(huán)境中。我以UVM為例來說明,其基本結(jié)構(gòu)如下:

指令隨機(jī)化:對指令進(jìn)行約束,生成隨機(jī)指令;

指令驅(qū)動:將指令轉(zhuǎn)換成文件,提供給cmodel,以及初始化到ddr文件中;

參數(shù)隨機(jī)化:隨機(jī)化權(quán)重等參數(shù);

參數(shù)驅(qū)動:將參數(shù)初始化為ddr文件;

AXI驅(qū)動:這個包含AXI讀寫ddr文件的驅(qū)動,用于和DUT進(jìn)行交互;

Monitor:監(jiān)測DUT行為,和cmodel的數(shù)據(jù)進(jìn)行對比;

4. 驅(qū)動

驅(qū)動主要是完成ddr的初始化,線程控制的配置以及中斷響應(yīng)等。首先將權(quán)重等參數(shù)初始化到ddr中,然后通過axi總線配置FPGA的寄存器,同時對FPGA產(chǎn)生的中斷進(jìn)行響應(yīng)。獲取ddr中結(jié)果數(shù)據(jù)等。一般如zynq等SoC器件,因為集成了arm核,所以驅(qū)動相對簡單。如果軟件端在服務(wù)器,那么還需要PCIE等驅(qū)動來支持和服務(wù)器的交互。以SoC器件為例,linux驅(qū)動正常工作需要以下步驟:

1. 制作RTL硬件工程,生成bit文件和hardware配置文件;

2. 利用SDK生成fsbl文件,這個主要完成對zynq器件的一些基本硬件配置;

3. 制作linux的uboot、kernel、devicetree等文件;

4. 用fsbl、bit、uboot、kernel、devicetree制作boot.bin;

5. 選擇linux文件系統(tǒng),如linaro等。制作SD卡鏡像,燒寫到SD卡中,啟動SoC器件;

5. 編譯器

編譯器主要能夠根據(jù)深度學(xué)習(xí)模型來生成指令,并優(yōu)化指令。以TVM為例,它基于計算圖,對接市場上主流的深度學(xué)習(xí)框架:tensorflow、pytorch等,將這些模型進(jìn)行計算圖的轉(zhuǎn)化,然后基于這些計算圖來進(jìn)行圖的優(yōu)化和指令優(yōu)化。TVM目標(biāo)是通用性,所以其兼容CPU、GPU、TPU,同時還要對接更多的深度學(xué)習(xí)框架。所以其很龐大。針對FPGA自身的AI加速器,可以以這個為借鑒,開發(fā)自己的compiler。同時依據(jù)自身硬件特點進(jìn)行指令的優(yōu)化。

計算圖是基本很多編譯器采用的圖結(jié)構(gòu),其貫穿了指令優(yōu)化和生成始終。計算圖中的節(jié)點包含了數(shù)據(jù)信息和相應(yīng)操作。這些節(jié)點相互連接形成了一個網(wǎng)絡(luò)計算的依賴關(guān)系。計算圖是一個基于tensor操作的圖,它并不像通用CPU編譯器的細(xì)化的標(biāo)量操作。因為FPGA加速器中計算核一般都是張量操作。這是和CPU不同的。而且這樣的計算圖也相對簡潔。

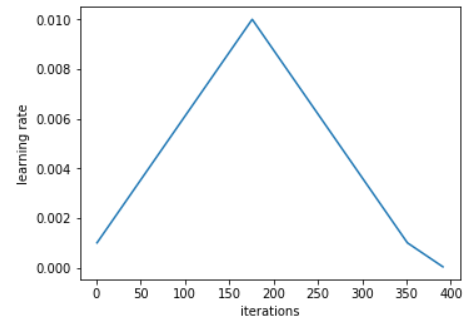

一個張量操作的實現(xiàn)有很多可能,因為依據(jù)數(shù)據(jù)之間的依賴關(guān)系和維度大小,可以對張量運算進(jìn)行分解為多步操作。這些分解有很多。因此優(yōu)化一個計算圖就會面臨很多這樣可能的步驟。這被稱為schedule,優(yōu)化就是在這些schedule空間中找出最優(yōu)的那個順序。TVM中提出了一個基于機(jī)器學(xué)習(xí)模型的優(yōu)化方法,去搜尋schedule空間,找到最適于硬件的圖。然后生成指令。

6. 模型壓縮

模型壓縮有很多方法,根據(jù)壓縮目標(biāo)主要包括量化和剪枝。量化就是將浮點定點化,剪枝就是去除一些冗余的連接或者數(shù)據(jù)。從一些文獻(xiàn)調(diào)研的結(jié)果有以下一些方式:

1) 二值化網(wǎng)絡(luò);

2) 向量壓縮方法;

3) 知識蒸餾;

4) CP分解;

5) 降維分解;

6) 深度壓縮;

7) 自動化搜索空間;

7. 軟件部署

因為FPGA并不適合加速神經(jīng)網(wǎng)絡(luò)的所有部分或者還沒有相應(yīng)IP來加速一些模塊,那么這些操作就會放在CPU上進(jìn)行,比如對于LSTM網(wǎng)絡(luò),前邊的embedding層還有后端的softmax或者類別生成。這些都更適合在CPU上做。因此軟件部署來調(diào)用FPGA硬核IP,和FPGA進(jìn)行交互。同時還有一些數(shù)據(jù)準(zhǔn)備、打印等操作,客戶展示。這些都是軟件部署要做的。

總結(jié)

一個AI加速涉及到了算法、軟件、驅(qū)動、硬件方面,因此通常做AI加速的團(tuán)隊都比較龐大,包含了算法到硬件的各種人才。

-

FPGA

+關(guān)注

關(guān)注

1629文章

21729瀏覽量

603009 -

AI

+關(guān)注

關(guān)注

87文章

30728瀏覽量

268889 -

深度學(xué)習(xí)

+關(guān)注

關(guān)注

73文章

5500瀏覽量

121113

發(fā)布評論請先 登錄

相關(guān)推薦

NPU在深度學(xué)習(xí)中的應(yīng)用

GPU深度學(xué)習(xí)應(yīng)用案例

FPGA加速深度學(xué)習(xí)模型的案例

AI大模型與深度學(xué)習(xí)的關(guān)系

深度學(xué)習(xí)GPU加速效果如何

FPGA做深度學(xué)習(xí)能走多遠(yuǎn)?

FPGA在人工智能中的應(yīng)用有哪些?

深度學(xué)習(xí)中的時間序列分類方法

深度學(xué)習(xí)與nlp的區(qū)別在哪

深度解析深度學(xué)習(xí)下的語義SLAM

FPGA在深度學(xué)習(xí)應(yīng)用中或?qū)⑷〈鶪PU

fpga學(xué)習(xí)需要具備哪些課程

為什么深度學(xué)習(xí)的效果更好?

FPGA做深度學(xué)習(xí)加速的技能總結(jié)

FPGA做深度學(xué)習(xí)加速的技能總結(jié)

評論