晶體管越來越小,但是高性能計算需求越來越高,有些人就反其道而行之,嘗試制造超大芯片。

之前我們就見識過Cerebras Systems打造的世界最大芯片WSE,擁有46225平方毫米面積、1.2萬億個晶體管、40萬個AI核心、18GB SRAM緩存……并得到了美國能源部的青睞和部署。

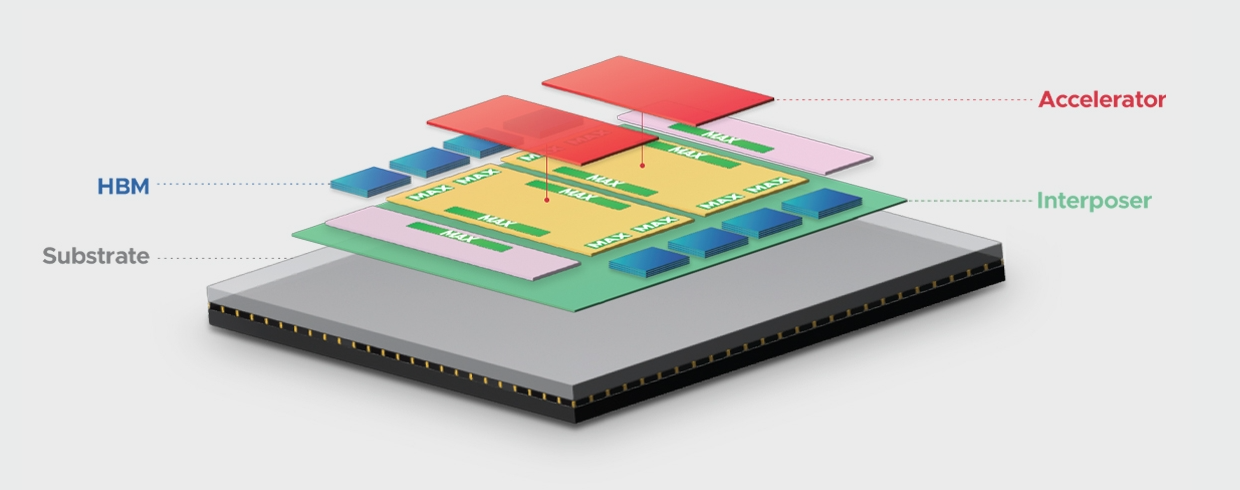

現在,臺積電、博通聯合宣布,雙方將利用晶圓上芯片封裝(CoWos)技術,打造面積達1700平方毫米的中介層(Interposer),是芯片蝕刻所用光掩模(光罩)尺寸極限858平方毫米的整整兩倍。

這樣規模的中介層顯然是無法一次性單個制造出來的,臺積電實際上是同時在晶圓上蝕刻多個中介層,然后將它們連接在一起,組成一個整體。

工藝上,臺積電也用上了最先進的5nm EUV(N5),它將在今年上半年投入量產。

所謂中介層,用途就是串聯不同裸片(Die)的橋梁,因為隨著現代芯片日益復雜,制造單個大型SoC的代價越來越大,所以行業普遍開發出了各種新的封裝技術,將不同的小芯片、模塊整合在一起,構成一顆大芯片。

博通就計劃用這個龐大無比的中介層,封裝多個SoC芯片,以及六顆HMB2內存,單顆容量16GB,總容量達96GB/s,帶寬也高達2.7TB/s。

臺積電和高通未透露這種龐大芯片的具體規格,只是說將用于高性能計算領域。

另外,臺積電還在改進CoWoS封裝技術,所以未來不排除面積超過1700平方毫米的更大芯片。

-

處理器

+關注

關注

68文章

19259瀏覽量

229654 -

臺積電

+關注

關注

44文章

5632瀏覽量

166414 -

cpu

+關注

關注

68文章

10854瀏覽量

211590 -

博通

+關注

關注

35文章

4325瀏覽量

106889

發布評論請先 登錄

相關推薦

16管能穿幾根六類網線

OpenAI攜手博通、臺積電打造內部芯片

OpenAI攜手博通臺積電打造自主芯片

臺積電新版CoWoS封裝技術拓寬系統級封裝尺寸

臺積電將制造兩倍于當今最大芯片尺寸的大型芯片,功率數千瓦

探索電動車電池電纜超聲金屬焊接技術

小米Redmi Note 13 Pro+港版上市,售價2999港元約合人民幣2774元

電機功率與配線直徑計算方法與步驟詳解

2毫米×2毫米SON中的汽車2.25兆赫1-A降壓轉換器TPS62590-Q1數據表

臺積電聯合博通打造1700平方毫米巨型中介層

臺積電聯合博通打造1700平方毫米巨型中介層

評論