(一)AXI接口

如何設(shè)計(jì)高效的 PL 和 PS 數(shù)據(jù)交互通路是 ZYNQ 芯片設(shè)計(jì)的重中之重。AXI 全稱 Advanced eXtensible Interface,是 Xilinx 從 6 系列的 FPGA 開始引入的一個(gè)接口協(xié)議,主要描述了主設(shè)備和從設(shè)備之間的數(shù)據(jù)傳輸方式。在 ZYNQ 中繼續(xù)使用,版本是 AXI4,所以我們經(jīng)常會(huì)看到 AXI4.0, ZYNQ 內(nèi)部設(shè)備都有 AXI 接口。其實(shí) AXI 就是 ARM 公司提出的AMBA(Advanced Microcontroller Bus Architecture)的一個(gè)部分,是一種高性能、高帶寬、低延遲的片內(nèi)總線。

AXI 協(xié)議主要描述了主設(shè)備和從設(shè)備之間的數(shù)據(jù)傳輸方式,主設(shè)備和從設(shè)備之間通過(guò)握手信號(hào)建立連接。當(dāng)從設(shè)備準(zhǔn)備好接收數(shù)據(jù)時(shí),會(huì)發(fā)出 READY 信號(hào)。當(dāng)主設(shè)備的數(shù)據(jù)準(zhǔn)備好時(shí),會(huì)發(fā)出和維持 VALID 信號(hào),表示數(shù)據(jù)有效。數(shù)據(jù)只有在 VALID 和 READY 信號(hào)都有效的時(shí)候才開始傳輸。當(dāng)這兩個(gè)信號(hào)持續(xù)保持有效,主設(shè)備會(huì)繼續(xù)傳輸下一個(gè)數(shù)據(jù)。主設(shè)備可以撤銷VALID 信號(hào),或者從設(shè)備撤銷 READY 信號(hào)終止傳輸。 AXI 的協(xié)議如圖, T2 時(shí),從設(shè)備的 READY信號(hào)有效, T3 時(shí)主設(shè)備的 VILID 信號(hào)有效,數(shù)據(jù)傳輸開始。

在 ZYNQ 中,支持 AXI-Lite, AXI4 和 AXI-Stream 三種總線,通過(guò)表以看到這三種AXI 接口的特性。

1、AXI4-Lite:

具有輕量級(jí),結(jié)構(gòu)簡(jiǎn)單的特點(diǎn),適合小批量數(shù)據(jù)、簡(jiǎn)單控制場(chǎng)合。不支持批量傳輸,讀寫時(shí)一次只能讀寫一個(gè)字(32bit)。主要用于訪問(wèn)一些低速外設(shè)和外設(shè)的控制。

2、AXI4:

接口和 AXI-Lite 差不多,只是增加了一項(xiàng)功能就是批量傳輸,可以連續(xù)對(duì)一片地址進(jìn)行一次性讀寫。也就是說(shuō)具有數(shù)據(jù)讀寫的 burst 功能。

上面兩種均采用內(nèi)存映射控制方式,即 ARM 將用戶自定義 IP 編入某一地址進(jìn)行訪問(wèn),讀寫時(shí)就像在讀寫自己的片內(nèi) RAM,編程也很方便,開發(fā)難度較低。代價(jià)就是資源占用過(guò)多,需要額外的讀地址線、寫地址線、讀數(shù)據(jù)線、寫數(shù)據(jù)線、寫應(yīng)答線。

3、AXI4-Stream:

這是一種連續(xù)流接口,不需要地址線(很像 FIFO,一直讀或一直寫就行)。對(duì)于這類 IP,ARM 不能通過(guò)上面的內(nèi)存映射方式控制(FIFO 根本沒有地址的概念),必須有一個(gè)轉(zhuǎn)換裝置,例如 AXI-DMA 模塊來(lái)實(shí)現(xiàn)內(nèi)存映射到流式接口的轉(zhuǎn)換。 AXI-Stream 適用的場(chǎng)合有很多:視頻流處理;通信協(xié)議轉(zhuǎn)換;數(shù)字信號(hào)處理;無(wú)線通信等。其本質(zhì)都是針對(duì)數(shù)值流構(gòu)建的數(shù)據(jù)通路,從信源(例如 ARM 內(nèi)存、 DMA、無(wú)線接收前端等)到信宿(例如 HDMI 顯示器、高速 AD 音頻輸出,等)構(gòu)建起連續(xù)的數(shù)據(jù)流。這種接口適合做實(shí)時(shí)信號(hào)處理。

在 ZYNQ 芯片內(nèi)部用硬件實(shí)現(xiàn)了 AXI 總線協(xié)議,包括 9 個(gè)物理接口,分別為 AXI-GP0~AXIGP3, AXI-HP0~AXI-HP3, AXI-ACP 接口。AXI_ACP 接口,是 ARM 多核架構(gòu)下定義的一種接口,中文翻譯為加速器一致性端口,用來(lái)管理 DMA 之類的不帶緩存的 AXI 外設(shè), PS 端是 Slave 接口。AXI_HP 接口,是高性能/帶寬的 AXI3.0 標(biāo)準(zhǔn)的接口,總共有四個(gè), PL 模塊作為主設(shè)備連接。主要用于 PL 訪問(wèn) PS 上的存儲(chǔ)器(DDR 和 On-Chip RAM)AXI_GP 接口,是通用的 AXI 接口,總共有四個(gè),包括兩個(gè) 32 位主設(shè)備接口和兩個(gè) 32 位從設(shè)備接口。

只有兩個(gè) AXI-GP 是 Master Port,即主機(jī)接口,其余 7 個(gè)口都是 Slave Port(從機(jī)接口)。主機(jī)接口具有發(fā)起讀寫的權(quán)限, ARM 可以利用兩個(gè) AXI-GP 主機(jī)接口主動(dòng)訪問(wèn) PL 邏輯,其實(shí)就是把 PL 映射到某個(gè)地址,讀寫 PL 寄存器如同在讀寫自己的存儲(chǔ)器。其余從機(jī)接口就屬于被動(dòng)接口,接受來(lái)自 PL 的讀寫,逆來(lái)順受。

另外這 9 個(gè) AXI 接口性能也是不同的。 GP 接口是 32 位的低性能接口,理論帶寬600MB/s,而 HP 和 ACP 接口為 64 位高性能接口,理論帶寬 1200MB/s。

位于 PS 端的 ARM 直接有硬件支持 AXI 接口,而 PL 則需要使用邏輯實(shí)現(xiàn)相應(yīng)的 AXI 協(xié)議。Xilinx 在 Vivado 開發(fā)環(huán)境里提供現(xiàn)成 IP 如 AXI-DMA, AXI-GPIO, AXI-Dataover, AXI-Stream 都實(shí)現(xiàn)了相應(yīng)的接口,使用時(shí)直接從 Vivado 的 IP 列表中添加即可實(shí)現(xiàn)相應(yīng)的功能。

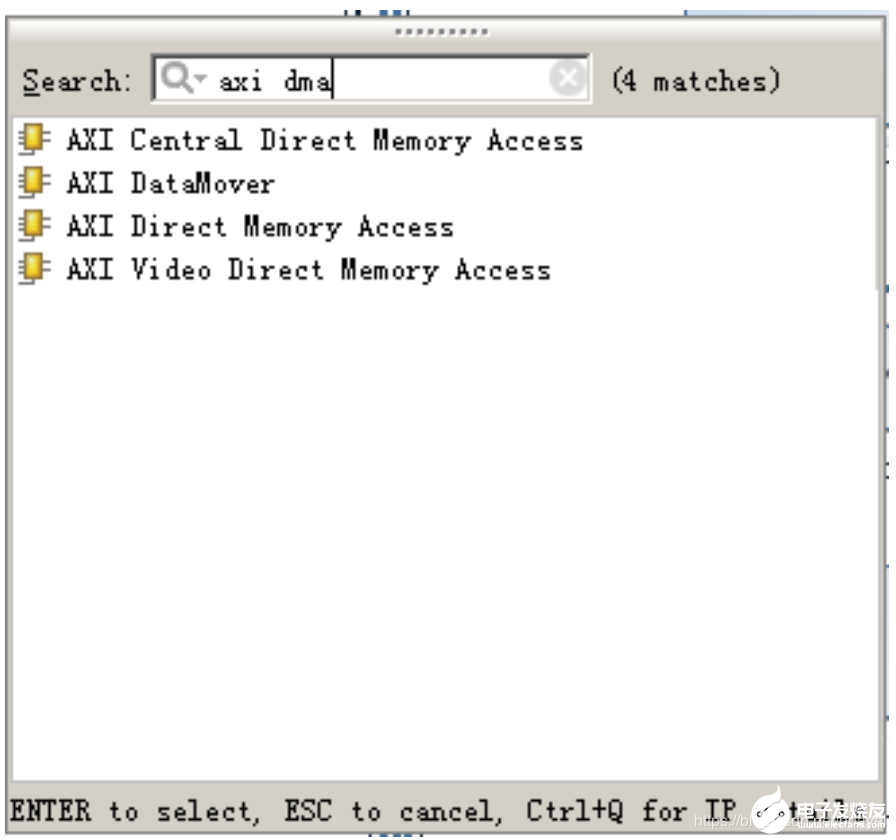

下圖為 Vivado 下的各種 DMA IP:

幾個(gè)常用的 AXI 接口 IP 的功能:

AXI-DMA:實(shí)現(xiàn)從 PS 內(nèi)存到 PL 高速傳輸高速通道 AXI-HP<---->AXI-Stream 的轉(zhuǎn)換

AXI-FIFO-MM2S:實(shí)現(xiàn)從 PS 內(nèi)存到 PL 通用傳輸通道 AXI-GP<----->AXI-Stream 的轉(zhuǎn)換

AXI-Datamover:實(shí)現(xiàn)從 PS 內(nèi)存到 PL 高速傳輸高速通道 AXI-HP<---->AXI-Stream 的轉(zhuǎn)換,只不過(guò)這次是完全由 PL 控制的, PS 是完全被動(dòng)的。

AXI-VDMA:實(shí)現(xiàn)從 PS 內(nèi)存到 PL 高速傳輸高速通道 AXI-HP<---->AXI-Stream 的轉(zhuǎn)換,只不過(guò)是專門針對(duì)視頻、圖像等二維數(shù)據(jù)的。

AXI-CDMA:這個(gè)是由 PL 完成的將數(shù)據(jù)從內(nèi)存的一個(gè)位置搬移到另一個(gè)位置,無(wú)需 CPU 來(lái)插手。

(二)AXI 交換機(jī)制

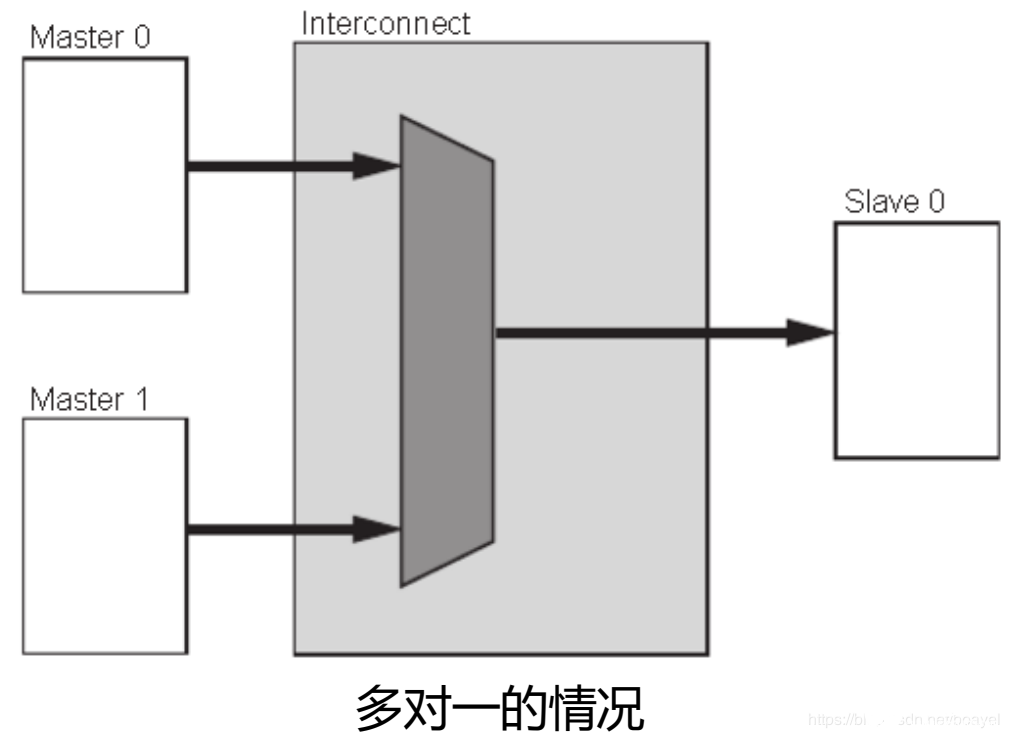

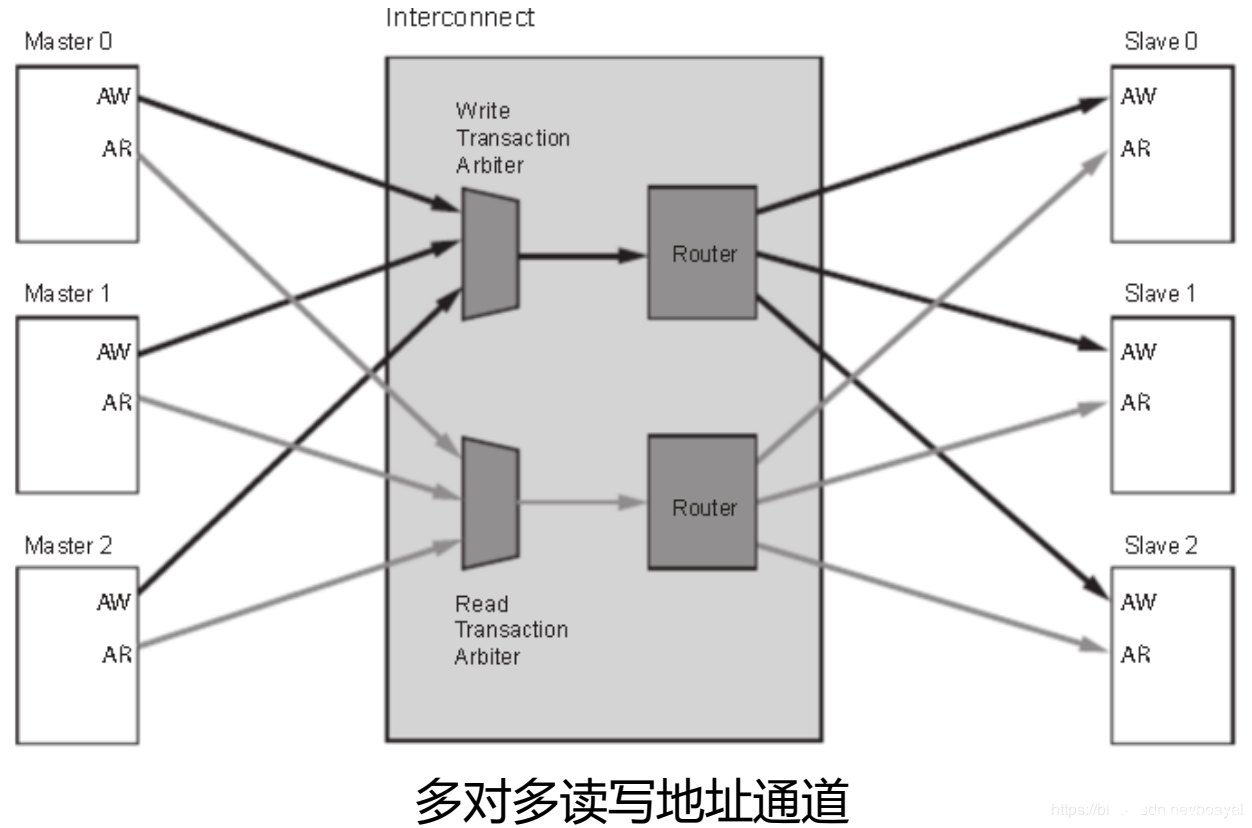

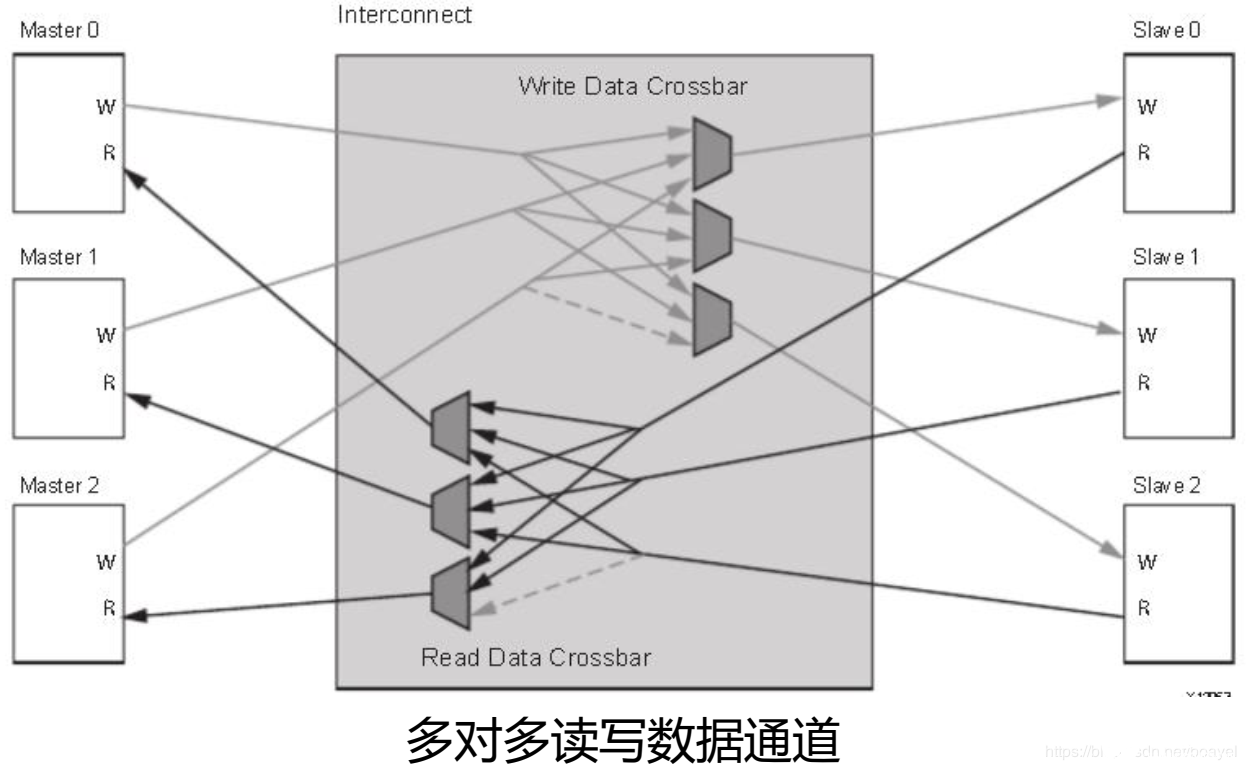

AXI 協(xié)議嚴(yán)格的講是一個(gè)點(diǎn)對(duì)點(diǎn)的主從接口協(xié)議,當(dāng)多個(gè)外設(shè)需要互相交互數(shù)據(jù)時(shí),我們需要加入一個(gè) AXI Interconnect 模塊,也就是 AXI 互聯(lián)矩陣,作用是提供將一個(gè)或多個(gè) AXI 主設(shè)備連接到一個(gè)或多個(gè) AXI 從設(shè)備的一種交換機(jī)制(有點(diǎn)類似于交換機(jī)里面的交換矩陣)。這個(gè) AXI Interconnect IP 核最多可以支持 16 個(gè)主設(shè)備、 16 個(gè)從設(shè)備,如果需要更多的接口,可以多加入幾個(gè) IP 核。

AXI Interconnect 基本連接模式有以下幾種:

N-to-1 Interconnect

to-N Interconnect

N-to-M Interconnect (Crossbar Mode)

N-to-M Interconnect (Shared Access Mode)

ZYNQ 內(nèi)部的 AXI 接口設(shè)備就是通過(guò)互聯(lián)矩陣的的方式互聯(lián)起來(lái)的,既保證了傳輸數(shù)據(jù)的高效性,又保證了連接的靈活性。 Xilinx 在 Vivado 里我們提供了實(shí)現(xiàn)這種互聯(lián)矩陣的 IP 核axi_interconnect,我們只要調(diào)用就可以。

-

接口

+關(guān)注

關(guān)注

33文章

8575瀏覽量

151021 -

IP核

+關(guān)注

關(guān)注

4文章

327瀏覽量

49485

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

AMBA AXI4接口協(xié)議概述

mosfet的三種工作狀態(tài)及工作條件是什么

單片機(jī)的三種總線結(jié)構(gòu)

放大電路的三種組態(tài)可以放大什么

電壓型逆變器可具體分為哪三種?

有關(guān)PL端利用AXI總線控制PS端DDR進(jìn)行讀寫(從機(jī)wready信號(hào)一直不拉高)

晶體管的三種工作狀態(tài)

淺析FreeRTOS任務(wù)調(diào)度器的三種調(diào)度算法和應(yīng)用

FPGA通過(guò)AXI總線讀寫DDR3實(shí)現(xiàn)方式

AMBA總線之AXI設(shè)計(jì)的關(guān)鍵問(wèn)題講解

VMware虛擬機(jī)的三種網(wǎng)絡(luò)模式

晶體管的三種工作狀態(tài)及其特點(diǎn)

運(yùn)放的三種應(yīng)用

運(yùn)動(dòng)控制的三種控制方式

淺析三種AXI接口的特點(diǎn)

淺析三種AXI接口的特點(diǎn)

評(píng)論