在AI技術(shù)應(yīng)用拓展與AI加速芯片設(shè)計(jì)等領(lǐng)域大有發(fā)展的Google,正在嘗試以基于機(jī)器學(xué)習(xí)算法的AI技術(shù)來進(jìn)行AI芯片開發(fā)。

Google研究人員在在一篇論文中表示:“我們相信正是AI本身將縮短芯片設(shè)計(jì)周期,在硬件與AI之間建立共生關(guān)系的手段,而兩者之間的相互推動(dòng)又推動(dòng)了這一進(jìn)步。”

Google的高級(jí)研究科學(xué)家AzaliaMirhoseini說,我們已經(jīng)看到有些算法或神經(jīng)網(wǎng)絡(luò)體系結(jié)構(gòu)……在現(xiàn)有的加速器中表現(xiàn)不佳,因?yàn)榧铀倨鞯脑O(shè)計(jì)是兩年前定義的,但那時(shí)的神經(jīng)網(wǎng)絡(luò)早便不存在了。如果能縮短芯片設(shè)計(jì)周期,那我們就我們可以縮小差距。

Mirhoseini和高級(jí)軟件工程師AnnaGoldie提出了一個(gè)神經(jīng)網(wǎng)絡(luò),可以學(xué)習(xí)做一個(gè)特別耗時(shí)的設(shè)計(jì)部分——placement。在對(duì)芯片設(shè)計(jì)進(jìn)行了足夠長(zhǎng)時(shí)間的研究后,它可以在不到24小時(shí)的時(shí)間內(nèi)為GoogleTensor處理單元完成設(shè)計(jì),這個(gè)產(chǎn)品在功耗,性能和面積方面的表現(xiàn),優(yōu)于人類專家花費(fèi)了數(shù)周時(shí)間設(shè)計(jì)的產(chǎn)品。

我們知道,placement非常復(fù)雜且耗時(shí),因?yàn)樗婕胺胖眠壿嫼蛢?nèi)存塊或稱為宏的那些塊的群集,從而使功率和性能較大化,并且芯片面積最小化。但這些設(shè)計(jì)面臨的挑戰(zhàn)是——必須在遵守互連密度規(guī)則的同時(shí)進(jìn)行所有這些工作。Goldie和Mirhoseini的目標(biāo)是芯片placement,,因?yàn)榧词故褂卯?dāng)今的先進(jìn)工具,人類專家也需要花費(fèi)數(shù)周的迭代時(shí)間才能得出可接受的設(shè)計(jì)。

Goldie和Mirhoseini將芯片placement建模為強(qiáng)化學(xué)習(xí)問題。與典型的深度學(xué)習(xí)不同,強(qiáng)化學(xué)習(xí)系統(tǒng)不會(huì)訓(xùn)練大量的標(biāo)簽數(shù)據(jù)。相反,他們會(huì)邊做邊學(xué),并在成功時(shí)根據(jù)獎(jiǎng)勵(lì)信號(hào)調(diào)整網(wǎng)絡(luò)中的參數(shù)。在這種情況下,獎(jiǎng)勵(lì)是降低功率,改善性能和減少面積的組合的替代指標(biāo)。結(jié)果,布局機(jī)器人執(zhí)行的設(shè)計(jì)越多,其任務(wù)就會(huì)越好。

該團(tuán)隊(duì)希望像他們一樣的AI系統(tǒng)將使得在同一時(shí)間段內(nèi)設(shè)計(jì)更多的芯片,以及運(yùn)行速度更快,功耗更低,制造成本更低,占地面積更少的芯片”的設(shè)計(jì)。

除了Google,還有兩大EDA巨頭Synopsys和Cadence也都發(fā)表了相關(guān)的AI設(shè)計(jì)芯片方案:

其中,Synopsys推出了業(yè)界一個(gè)用于芯片設(shè)計(jì)的自主人工智能應(yīng)用程序——DSO.ai?(DesignSpaceOptimizationAI),這是電子設(shè)計(jì)技術(shù)上所取得的重大突破。DSO.ai?解決方案的創(chuàng)新靈感來源于DeepMind的AlphaZero,使得AI在圍棋、象棋領(lǐng)域遠(yuǎn)超人類。作為一款人工智能和推理引擎,DSO.ai能夠在芯片設(shè)計(jì)的巨大求解空間里搜索優(yōu)化目標(biāo)。該解決方案大規(guī)模擴(kuò)展了對(duì)芯片設(shè)計(jì)流程選項(xiàng)的探索,能夠自主執(zhí)行次要決策,幫助芯片設(shè)計(jì)團(tuán)隊(duì)以專家級(jí)水平進(jìn)行操作,并大幅提高整體生產(chǎn)力,從而在芯片設(shè)計(jì)領(lǐng)域掀起新一輪革命。

根據(jù)官方介紹,DSO.ai解決方案通過實(shí)現(xiàn)廣泛設(shè)計(jì)空間的自主優(yōu)化,徹底革新了搜索較好解決方案的過程。該引擎通過獲取由芯片設(shè)計(jì)工具生成的大數(shù)據(jù)流,并用其來探索搜索空間、觀察設(shè)計(jì)隨時(shí)間的演變情況,同時(shí)調(diào)整設(shè)計(jì)選擇、技術(shù)參數(shù)和工作流程,以指導(dǎo)探索過程向多維優(yōu)化的目標(biāo)發(fā)展。DSO.ai采用新思科技研發(fā)團(tuán)隊(duì)發(fā)明的高端機(jī)器學(xué)習(xí)技術(shù)來執(zhí)行大規(guī)模搜索任務(wù),自主運(yùn)行成千上萬的探索矢量,并實(shí)時(shí)獲取千兆字節(jié)的高速設(shè)計(jì)分析數(shù)據(jù)。

同時(shí),DSO.ai可以自主執(zhí)行如調(diào)整工具設(shè)置等次要決策,為開發(fā)者減負(fù),并讓芯片設(shè)計(jì)團(tuán)隊(duì)接近專家級(jí)水平進(jìn)行操作。此外,整個(gè)設(shè)計(jì)團(tuán)隊(duì)可以高效分享和運(yùn)用相關(guān)知識(shí)。這樣級(jí)別的高生產(chǎn)效率,意味著開發(fā)者能處理更多項(xiàng)目,并專注于更具創(chuàng)造性、更有價(jià)值的任務(wù)。

他們進(jìn)一步指出,通過大規(guī)模擴(kuò)展設(shè)計(jì)工作流程,DSO.ai讓用戶能夠立即洞悉難以探索的設(shè)計(jì)、工藝和技術(shù)解決方案空間。借助可見性的增強(qiáng),芯片設(shè)計(jì)團(tuán)隊(duì)可以在預(yù)算和進(jìn)度內(nèi),將更好性能和更高能效的差異化產(chǎn)品推向市場(chǎng)。這意味著設(shè)計(jì)團(tuán)隊(duì)得以較大程度地發(fā)揮芯片工藝技術(shù)的優(yōu)勢(shì),并不斷突破設(shè)計(jì)規(guī)模的極限。

借助DSO.ai解決方案,開發(fā)者的工作效率將大大提高,次要任務(wù)則可實(shí)現(xiàn)完全自動(dòng)化執(zhí)行。DSO.ai能大幅縮短芯片設(shè)計(jì)團(tuán)隊(duì)為新市場(chǎng)創(chuàng)建產(chǎn)品的交付時(shí)間,同時(shí)加速開發(fā)現(xiàn)有產(chǎn)品的衍生品,這意味著芯片設(shè)計(jì)團(tuán)隊(duì)能輕松地根據(jù)產(chǎn)品的不同功能集合來重新定位不同市場(chǎng)。

此外,DSO.ai能充分利用較有價(jià)值的資源,即工程設(shè)計(jì)創(chuàng)造力。開發(fā)者能夠從費(fèi)時(shí)的手動(dòng)操作中解放出來,并接手新項(xiàng)目的工作,而新員工則能快速上手且達(dá)到經(jīng)驗(yàn)豐富的專家水平,此外設(shè)計(jì)和制造的總體成本也被降至較低。

另一個(gè)EDA巨頭Cadence則發(fā)布業(yè)界一款基于機(jī)器學(xué)習(xí)引擎的新版數(shù)字全流程。據(jù)官方介紹,這是一個(gè)已經(jīng)過數(shù)百次先進(jìn)工藝節(jié)點(diǎn)成功流片驗(yàn)證的新版Cadenceò數(shù)字全流程,進(jìn)一步優(yōu)化功耗,性能和面積,廣泛應(yīng)用于汽車,移動(dòng),網(wǎng)絡(luò),高性能計(jì)算和人工智能(AI)等各個(gè)領(lǐng)域。流程采用了支持機(jī)器學(xué)習(xí)(ML)功能的統(tǒng)一布局布線和物理優(yōu)化引擎等多項(xiàng)業(yè)界首創(chuàng)技術(shù),吞吐量較高提升3倍,PPA較高提升20%,助力實(shí)現(xiàn)卓越設(shè)計(jì)。

據(jù)介紹,經(jīng)過多項(xiàng)關(guān)鍵技術(shù),全新Cadence數(shù)字全流程實(shí)現(xiàn)了PPA和吞吐量的進(jìn)一步提升:

Cadence表示,iSpatial技術(shù)將Innovus?設(shè)計(jì)實(shí)現(xiàn)系統(tǒng)的GigaPlace?布線引擎和GigaOpt?優(yōu)化器集成到Genus?綜合解決方案,支持布線層分配,有效時(shí)鐘偏移和通孔支柱等特性。iSpatial技術(shù)讓用戶可以使用統(tǒng)一的用戶界面和數(shù)據(jù)庫(kù)完成從Genus物理綜合到Innovus設(shè)計(jì)實(shí)現(xiàn)的無縫銜接。

其集成的ML功能可以讓用戶用現(xiàn)有設(shè)計(jì)訓(xùn)練iSpatial優(yōu)化技術(shù),實(shí)現(xiàn)傳統(tǒng)布局布線流程設(shè)計(jì)裕度的最小化。此外數(shù)字全流程采用統(tǒng)一的設(shè)計(jì)實(shí)現(xiàn),時(shí)序簽核及電壓降簽核引擎,通過所有物理,時(shí)序和可靠性目標(biāo)設(shè)計(jì)的同時(shí)收斂來增強(qiáng)簽核性能,幫助客戶降低設(shè)計(jì)裕度,減少迭代。

也許,我們期待的AI改變芯片設(shè)計(jì)時(shí)代,很快就要到來。

-

Google

+關(guān)注

關(guān)注

5文章

1762瀏覽量

57507 -

機(jī)器學(xué)習(xí)

+關(guān)注

關(guān)注

66文章

8408瀏覽量

132573 -

ai技術(shù)

+關(guān)注

關(guān)注

1文章

1268瀏覽量

24291

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

新思科技Foundation IP:AI芯片低功耗設(shè)計(jì)必選項(xiàng)

AI大模型與深度學(xué)習(xí)的關(guān)系

Google AI技術(shù)助力中國(guó)品牌出海增長(zhǎng)

《AI for Science:人工智能驅(qū)動(dòng)科學(xué)創(chuàng)新》第二章AI for Science的技術(shù)支撐學(xué)習(xí)心得

RISC-V如何支持不同的AI和機(jī)器學(xué)習(xí)框架和庫(kù)?

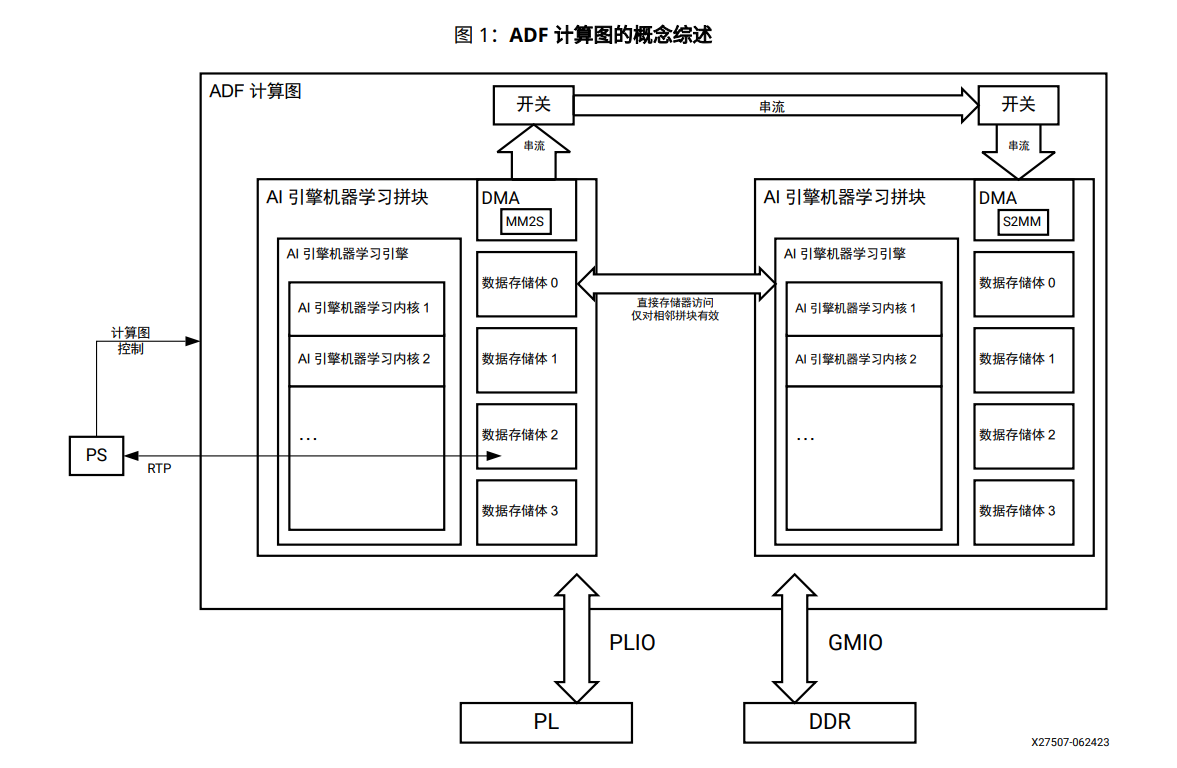

AI引擎機(jī)器學(xué)習(xí)陣列指南

平衡創(chuàng)新與倫理:AI時(shí)代的隱私保護(hù)和算法公平

risc-v多核芯片在AI方面的應(yīng)用

開發(fā)者手機(jī) AI - 目標(biāo)識(shí)別 demo

ai芯片是什么東西 ai芯片和普通芯片的區(qū)別

NanoEdge AI的技術(shù)原理、應(yīng)用場(chǎng)景及優(yōu)勢(shì)

AI芯片技術(shù)的演進(jìn)

分析 丨AI算法愈加復(fù)雜,但是機(jī)器視覺的開發(fā)門檻在降低

Google正在嘗試以基于機(jī)器學(xué)習(xí)算法的AI技術(shù)來進(jìn)行AI芯片開發(fā)

Google正在嘗試以基于機(jī)器學(xué)習(xí)算法的AI技術(shù)來進(jìn)行AI芯片開發(fā)

評(píng)論