今天我們講述一下如何使用模型添加法去添加相對傳輸延遲的等長規則,具體的操作步驟如下所示:

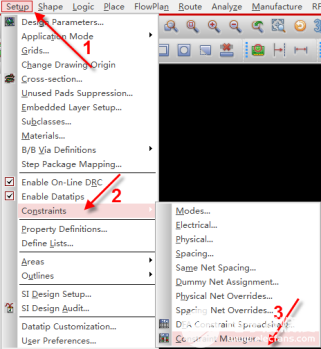

第一步,打開規則管理器,執行菜單命令Setup-Constraints,在下拉菜單中選擇Constraint Manager,如圖5-99所示,進入到規則管理器中;

圖5-99 規則管理器示意圖

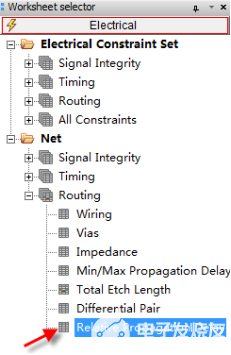

第二步,進入到規則管理器之后,在CM左側的目標欄中選擇Net,在Net中選擇相對傳輸延遲選項Relative Propagation Delay,如圖5-100所示;

圖5-100 相對傳輸延遲設置示意圖

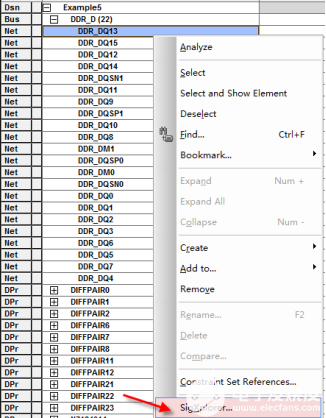

第三步,選中一根需要做等長其中一根信號線,點擊鼠標右鍵,選擇SigXplorer進行模型分析,如圖5-101所示;

圖5-101 模型分析設置示意圖

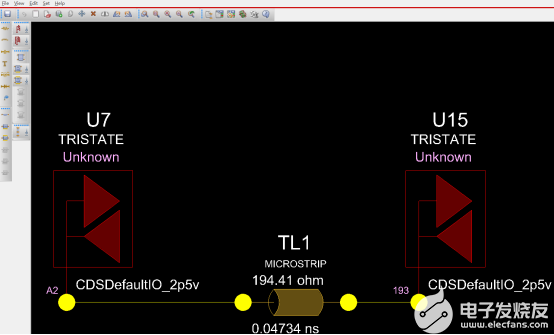

第四步,彈出的如圖5-102所示的界面,顯示了該網絡的鏈接拓撲結構以及網絡的連接關系,如圖5-102所示,U7與U15表示是的是元器件,下方的A2與193是器件的管腳標號;

圖5-102 信號走線拓撲結構示意圖

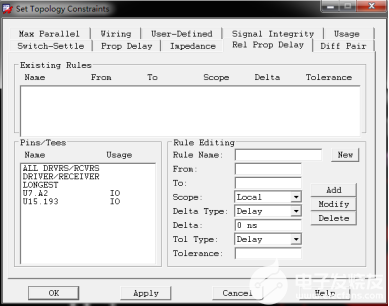

第五步,執行菜單命令Set-Constraints,設置規則即可,點擊之后彈出如圖5-103所示的界面,在這個界面進行規則的設定;

圖5-103 規則設定窗口示意圖

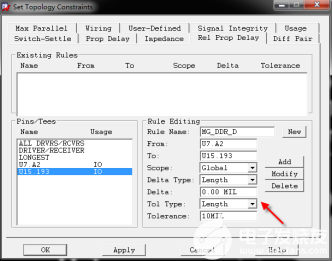

第六步,進入規則設定以后,我們需要選擇相對傳輸延遲,選擇Rel Prop Delay選項卡,在規則名稱一欄中輸入“MG_DDR_D”,From與To的選擇框不用手動去填寫,在左側的拓撲結構中直接選擇即可,其它設置參數如圖5-104所示;

圖5-104 規則參數設置示意圖

第七步,設置好規則以后,點擊Add按鈕,在規則窗口Existing Rules中就新添加了一個相對延遲的規則;

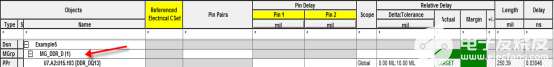

第八步,添加好規則以后,需要更新規則管理器,這樣規則才會更新到規則管理器中,執行菜單命令File-Update Constraints Manager或者是單擊Update CM的按鈕,效果也是一致的,更新以后,回到規則管理器,就會出現我們剛才添加的規則,如圖5-105所示;

圖5-105 約束模板示意圖

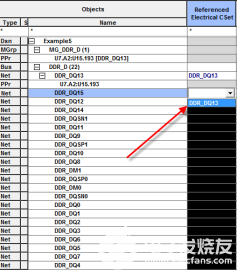

第九步,上述的操作,就成功添加了一個模型,我們還需要將這個模型應用到其它相同拓撲結構中去,如圖5-106所示;

圖5-106 應用模板示意圖

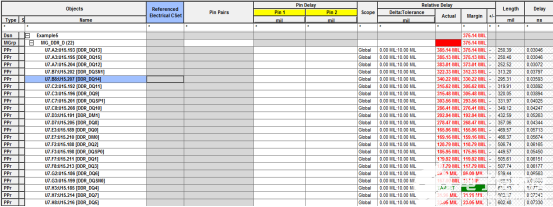

第十步,應用模板以后,所有相同拓撲結構的網絡都會自動添加到等長的集合當中,如圖5-107所示,這樣所有的等長規則就已經全部設定好了;

圖5-107 模型添加法完成示意圖

第十一步,應用好所有的模型之后,所有的需要等長的信號全部出現在等長列表中,按照直接添加法中的設置一樣,設置好目標線,回到PCB界面進行等長即可。

上述,就是在Allegro軟件中如何通過模型添加的方法,去添加相對傳輸延遲的等長規則的方法解析。

-

數據傳輸

+關注

關注

9文章

1889瀏覽量

64587 -

CM

+關注

關注

0文章

28瀏覽量

23111 -

信號

+關注

關注

11文章

2791瀏覽量

76754

發布評論請先 登錄

相關推薦

云服務器防火墻設置方法

傳輸接入設備怎么設置

網關的設置規則

AD9元器件間距規則如何設置

加法器是時序邏輯電路嗎

是否有uart命令來設置傳輸時的字符延遲?

使用ESP8266模塊進行UDP傳輸,重新連接路由后發送數據有延遲怎么避免?

串行加法器和并行加法器的區別?

Altium Designer電氣規則設置后無報錯原因解析

如何使用模型添加法設置相對傳輸延遲的等長規則

如何使用模型添加法設置相對傳輸延遲的等長規則

評論