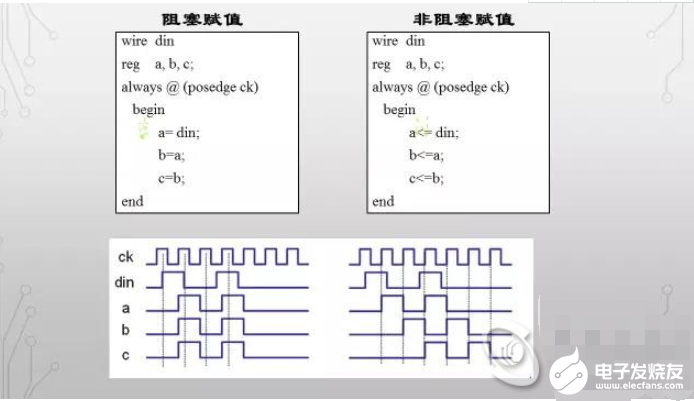

阻塞賦值對(duì)應(yīng)的電路往往與觸發(fā)沿沒(méi)有關(guān)系,只與輸入電平的變化有關(guān)系。

非阻塞賦值對(duì)應(yīng)的電路結(jié)構(gòu)往往與觸發(fā)沿有關(guān)系,只有在觸發(fā)沿時(shí)才有可能發(fā)生賦值的情況。

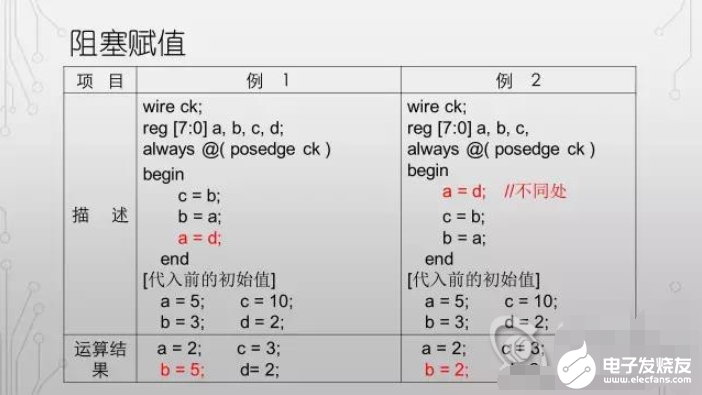

1、阻塞賦值操作符用等號(hào)(即 = )表示。“阻塞”是指在進(jìn)程語(yǔ)句(initial和always)中,當(dāng)前的賦值語(yǔ)句阻斷了其后的語(yǔ)句,也就是說(shuō)后面的語(yǔ)句必須等到當(dāng)前的賦值語(yǔ)句執(zhí)行完畢才能執(zhí)行。而且阻塞賦值可以看成是一步完成的,即:計(jì)算等號(hào)右邊的值并同時(shí)賦給左邊變量。例如:

當(dāng)執(zhí)行“x=next_x;”時(shí),x會(huì)立即的到next_x的值。而下一句“y=x;”必須等到“x=next_x;”執(zhí)行完畢才能被執(zhí)行。由于這兩條語(yǔ)句都沒(méi)有延遲(相當(dāng)于導(dǎo)線),導(dǎo)致他們的等價(jià)語(yǔ)句為“y=next_x;”。

賦值是實(shí)時(shí)的,計(jì)算完右面的馬上賦值給左邊的,然后再執(zhí)行下一句,操作時(shí)串行的,且在一個(gè)alway內(nèi)完成。

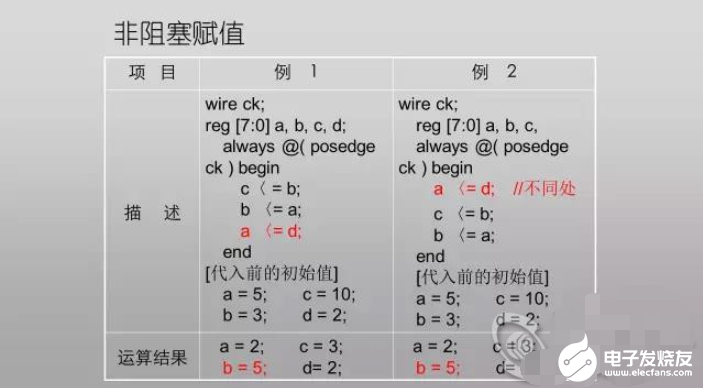

2、非阻塞賦值操作符用小于等于號(hào) (即 《= )表示。“非阻塞”是指在進(jìn)程語(yǔ)句(initial和always)中,當(dāng)前的賦值語(yǔ)句不會(huì)阻斷其后的語(yǔ)句。非阻塞語(yǔ)句可以認(rèn)為是分為兩個(gè)步驟進(jìn)行的:

①計(jì)算等號(hào)右邊的表達(dá)式的值,(我的理解是:在進(jìn)入進(jìn)程后,所有的非阻塞語(yǔ)句的右端表達(dá)式同時(shí)計(jì)算,賦值動(dòng)作只發(fā)生在順序執(zhí)行到當(dāng)前非阻塞語(yǔ)句那一刻)。

②在本條賦值語(yǔ)句結(jié)束時(shí),將等號(hào)右邊的值賦給等號(hào)左邊的變量。

例如:

當(dāng)執(zhí)行“x《=next_x;”時(shí),并不會(huì)阻斷語(yǔ)句“y《=x;”的執(zhí)行。因此,語(yǔ)句“y《=x;”中的x的值與語(yǔ)句“x《=next_x;”中的x的值不同:語(yǔ)句“y《=x;”中的x是第一個(gè)D觸發(fā)器的初值(Q0)。而語(yǔ)句“x《=next_x;”中的x的值是D觸發(fā)器經(jīng)過(guò)一個(gè)同步脈沖后的輸出值(Q1)。基于此這個(gè)進(jìn)程產(chǎn)生了與阻塞賦值進(jìn)程截然不同的結(jié)果,即:產(chǎn)生了移位寄存器的效果。

簡(jiǎn)單理解就是,阻塞賦值是按需執(zhí)行,非阻塞賦值是并行執(zhí)行。

為了更好地理解上述要點(diǎn),我們需要對(duì)Verilog 語(yǔ)言中的阻塞賦值和非阻塞賦值的功能和執(zhí)行時(shí)間上的差別有深入的了解。為了解釋問(wèn)題方便下面定義兩個(gè)縮寫(xiě)字:

RHS – 方程式右手方向的表達(dá)式或變量可分別縮寫(xiě)為:RHS表達(dá)式或RHS變量。LHS – 方程式左手方向的表達(dá)式或變量可分別縮寫(xiě)為:LHS表達(dá)式或LHS變量。

IEEE Verilog標(biāo)準(zhǔn)定義了有些語(yǔ)句有確定的執(zhí)行時(shí)間,有些語(yǔ)句沒(méi)有確定的執(zhí)行時(shí)間。若有兩條或兩條以上語(yǔ)句準(zhǔn)備在同一時(shí)刻執(zhí)行,但由于語(yǔ)句的排列次序不同(而這種排列次序的不同是IEEE Verilog標(biāo)準(zhǔn)所允許的), 卻產(chǎn)生了不同的輸出結(jié)果。這就是造成Verilog模塊冒險(xiǎn)和競(jìng)爭(zhēng)現(xiàn)象的原因。為了避免產(chǎn)生競(jìng)爭(zhēng),理解阻塞和非阻塞賦值在執(zhí)行時(shí)間上的差別是至關(guān)重要的。

-

Verilog

+關(guān)注

關(guān)注

29文章

1366瀏覽量

111899 -

阻塞賦值

+關(guān)注

關(guān)注

0文章

10瀏覽量

9236 -

非阻塞賦值

+關(guān)注

關(guān)注

0文章

11瀏覽量

10063

發(fā)布評(píng)論請(qǐng)先 登錄

Verilog語(yǔ)言中阻塞和非阻塞賦值的不同

在testbench中如何使用阻塞賦值和非阻塞賦值

Verilog中阻塞賦值和非阻塞賦值的正確使用

阻塞與非阻塞賦值的區(qū)別是什么?

阻塞賦值和非阻塞賦值的用法一篇文章就夠了

verilog中阻塞賦值和非阻塞賦值到底有什么區(qū)別

評(píng)論