ISSCC是半導體行業歷史最悠久的技術會議之一,每年二月在美國舊金山舉行。這次會議匯集了學術界和產業界人士,討論芯片電路設計的最新挑戰。該會議主要是一個電路設計會議,每個廠商都專注于他們的處理器中獨特電路設計的一個或多個特定方面。

今年的會議涵蓋了一系列深入主題,包括鎖相環、低功耗電路、內存、SerDes、DSP和處理器設計。處理器部分出現了領先的供應商,也有來自研究機構和學術界的項目。會議內容覆蓋了密集的芯片設計細節,下面介紹了處理器環節中有趣細節的突出部分。

這兩款5G智能手機的SOC設計分別來自聯發科和三星,它們關注的是為大公司混合不同Arm內核的CPU設計問題。此外,還解決了處理單元在重載時內部電壓下降檢測的問題。

第一個演示來自三星,該公司選擇構建一套三集群的CPU核心。三星在三個集群中的兩個使用了Arm授權的內核,但是性能最好的內核是由三星自己在Arm的架構許可下設計的——雙M4內核。雙M4核心有一個單獨的3MB L3緩存,核心目標是達到Intel i5的性能水平。

對于中等功率/性能范圍,三星使用了Arm Cortex-A75內核。“小型”節能內核是古老的Cortex-A55。三星M4核與Cortex-A55核之間的功率/性能差距太大,增加了Cortex-A75核來彌補這一差距。三星還在1024臺MAC電腦上增加了一個神經處理單元,但沒有提供太多細節。

高性能處理器中的電壓下降可能是一個問題。如果增加太多的保護帶,保持較高的電源電壓,那么會消耗更多的能量。在一個更節能的額定電壓下,當一個特定的耗電單元處于負載之下時——比如一個運行高分辨率游戲的GPU——內阻下降會導致內部電壓低于正常值。SOC供應商構建專門的電路來檢測這些壓降,并采取行動來緩解問題。他們的方法是延長時鐘,通過有效降低時鐘速度來降低電路速度和功耗。三星采用環形振蕩電路,可以根據電壓改變速度。壓降檢測在時鐘管理單元(CMU)中設置一個標志,并將時鐘速度減半。

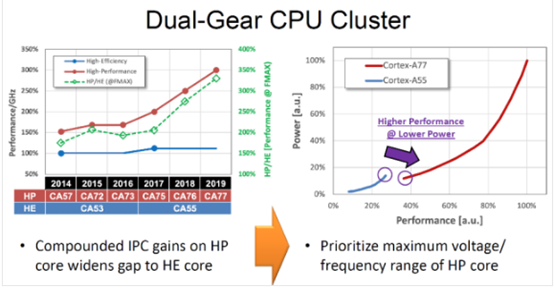

聯發科采取了不同的方式來選擇CPU核心,堅持ARM的big.LITTLE方案,聯發科稱之為雙齒輪設計。聯發科使用較新的Cortex-A77 CPU內核實現較強的性能內核。聯發科還指出,Cortex-A55小內核并沒有跟上性能內核的發展,他們沒有增加性能中等的核心,而是努力將A77的電壓范圍擴大到較低的速度。三星只有兩個性能核心,聯發科有四個A77核心。4個A77和4個A55內核共享一個2MB L3緩存。

聯發科對壓降的最初反應是在die上提供儲存電荷,可以提供一些瞬時電流,但這需要寶貴的die面積。因此,它決定將時鐘拉伸以節省die空間。

聯發科的一個重大變化是使用了鎖頻環(FLL),而不是鎖相環(PLL)。FLL設計有雙時鐘,但這個設計包含不確定性,因為它允許振蕩器隨電壓變化。有了FLL電路,聯發科Vmin大約有35mV的改進,節省了10%的功耗。聯發科還為該芯片構建了一個新穎的JTAG解決方案,該解決方案帶有一個網關TAP,用于分層訪問測試電路。

聯發科芯片還支持WiFi6,支持5G獨立和非獨立模式。A77核心支持高達2.6 GHz的時鐘速度,該芯片有一個Arm Mali G-77九核GPU。

-

處理器

+關注

關注

68文章

19312瀏覽量

230028 -

芯片

+關注

關注

456文章

50886瀏覽量

424163 -

三星電子

+關注

關注

34文章

15865瀏覽量

181040

原文標題:上網不用愁了!5G手機將支持WiFi 6!

文章出處:【微信號:SSDFans,微信公眾號:SSDFans】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

聯發科5G芯片供不應求,天璣9400獲手機廠追捧

三星或2025年推出三折智能手機

聯發科發布天璣9400手機芯片

三星發布新智能手機和無線耳機,引領移動科技新風尚

聯發科有望躋身三星旗艦供應鏈,天璣芯片或成Galaxy S25新選擇

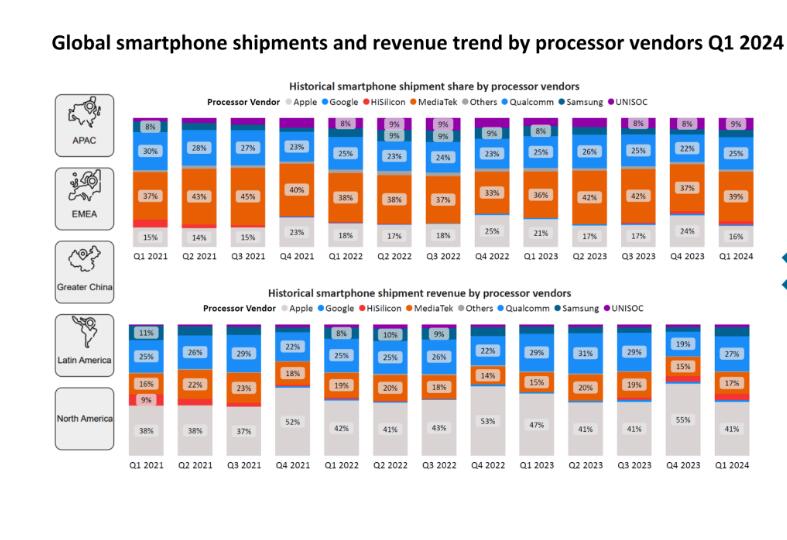

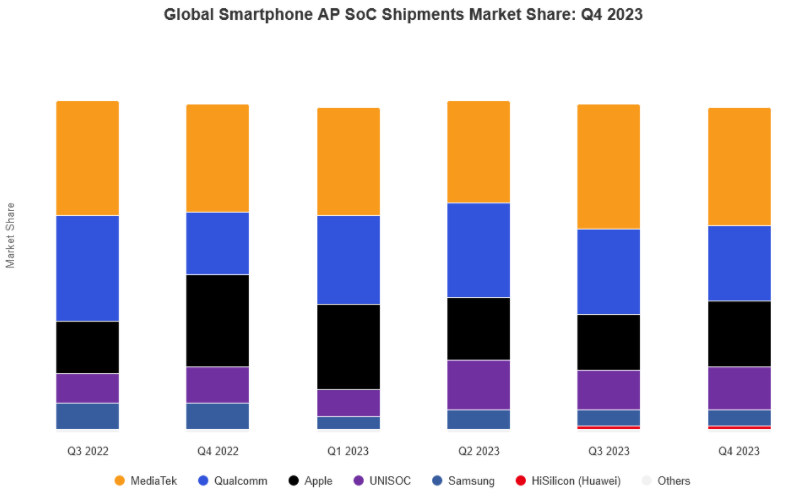

2024年第一季度全球智能手機SoC芯片出貨量及營收?

聯發科發布旗艦5G生成式AI移動芯片

聯發科旗艦芯片部署阿里云大模型

三星和聯發科7納米5G智能手機芯片

三星和聯發科7納米5G智能手機芯片

評論