改進設計時,如果 QoR 不升反降,那么您勢必將面臨如下選擇。

是繼續修復?還是重新尋找新的解決方案?您可能忽視了某些問題,或者可能工具在運行給定輪次時性能有所下降。能否快速準確解答這一問題恰恰是判斷 FPGA 工程師是否足夠出色的標準之一。

這里有一個好辦法- 解決方法問題即可簡化這一任務。在最近賽靈思內部調研中發現,29 種客戶設計的方法問題得到了解決。這些設計被歸到一起并與其原始版本進行比較。

隨后對這兩類設計稍作調整:

將關鍵時鐘的周期收緊 1ps 和 2ps

小幅更改網表

更改工具運行時使用的設置

結果毫無疑義地證明,采用經過清理的方法完成設計所產生的實現結果比未采用此類方法的設計的實現結果的一致性更高。

| 實驗 | QoR 離散值減少 |

| 網表更改 | -48% |

| 約束更改 | -10% |

Report Methodology 的檢查對象

report_methodology 將基于約 150 條規則進行檢查,這些規則與約束使用錯誤、欠優化時鐘設置、原語中缺少流水線寄存器問題等有關。

它是 (UG949) 中詳述的“UltraFast 設計方法”的補充工具。可用于自動執行諸多檢查

https://china.xilinx.com/support/documentation/sw_manuals/xilinx2019_2/c_ug949-vivado-design-methodology.pdf

Report Methodology 所在位置

您可在流程中任意階段運行 report_methodology。

通常只需在流程初期執行 opt_design 后運行此工具,布局或布線后將看到相同的結果。

您可通過以下方法找到 Report Methodology:

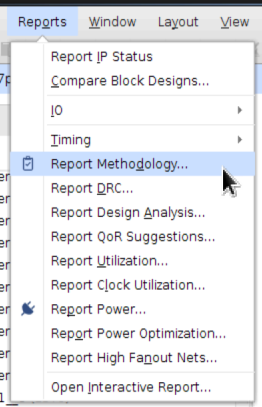

1.從 Vivado IDE 中的“Reports”->“Report Methodology”下拉菜單中

2.使用 Tcl 命令:report_methodology。

3.您還可在 Report QOR Assessment 中查看 Report Methodology 的精簡版本。RQA 報告將詳列影響 QoR 和工具變化的不合規的方法檢查。要獲取完整報告,請運行 report_methodology 命令。

解決方法問題意義非凡

總而言之,解決方法問題時,毋庸置疑,所付出的時間同樣有助于得到更為一致的實現結果,從而使您能夠作出更準確的決策。這也將使您能夠減少運行輪數,并比對結果,同時仍可確信 QoR 修復有效且工具正予以響應。

參考標簽:

qor

https://forums.xilinx.com/t5/tag/qor/tg-p/board-id/support_blog

report_methodology

https://forums.xilinx.com/t5/tag/report_methodology/tg-p/board-id/support_blog

report_qor_assessment

https://forums.xilinx.com/t5/tag/report_qor_assessment/tg-p/board-id/support_blog

-

FPGA

+關注

關注

1629文章

21748瀏覽量

603859 -

寄存器

+關注

關注

31文章

5355瀏覽量

120513

原文標題:開發者分享 | 解決方法論問題可提升實現的一致性

文章出處:【微信號:FPGA-EETrend,微信公眾號:FPGA開發圈】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

一致性測試系統的技術原理和也應用場景

電感值和直流電阻的一致性如何提高?

新品發布 | 同星智能正式推出CAN總線一致性測試系統

銅線鍵合焊接一致性:如何突破技術瓶頸?

為什么主機廠愈來愈重視CAN一致性測試?

鋰電池組裝及維修的關鍵:電芯一致性的重要性

QSFP一致性測試的專業測試設備

銅線鍵合焊接一致性:微電子封裝的新挑戰

企業數據備份體系化方法論的七大原則:深入理解數據備份的關鍵原則:應用一致性與崩潰一致性的區別

深入理解數據備份的關鍵原則:應用一致性與崩潰一致性的區別

解決方法論問題可提升實現的一致性

解決方法論問題可提升實現的一致性

評論