總結

一種新型自旋轉移轉矩磁阻存儲器(STT-MRAM) IP為高性能嵌入式應用提供了一個有吸引力的選擇。

介紹

如今,社會上廣泛的應用程序都迫切需要嵌入式非易失性內存IP。

embedded memory requirements

然而,嵌入式非易失性閃存IP的未來擴展在更高級的節點上是無效的。一些替代的存儲器技術已經被作為“閃存的替代品”來追求,例如相變存儲器(PCM)材料,電阻變化存儲器(RRAM),自旋轉移轉矩磁阻存儲器(STT-MRAM)。這些技術提供了密集的位單元(“1T1R”),并通過改變單元的靜態電阻來操作,這種電阻是通過材料的“Write1”和“Write0”脈沖電流和大小引起。當單元被訪問時,讀操作感知電阻大小,大大降低單元電流。理想情況下,兩個電阻之間的比率非常高,以加速讀取操作。

作為嵌入式閃存的替代品,這些技術的評估標準如下:

波動率量度,即操作溫度范圍、數據保留(非常依賴于溫度)

Bit密度

Bit單元電阻比

讀寫時間

數組寫粒度

低功率

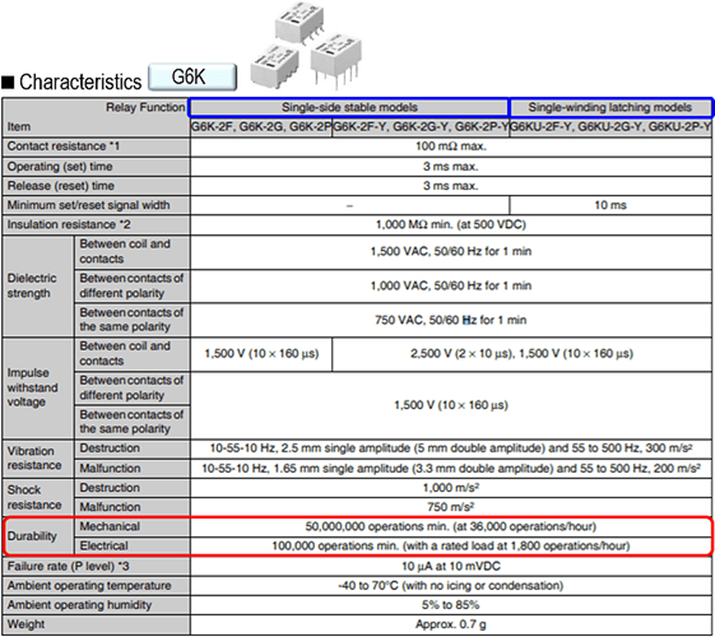

持久性(反映為超過誤碼率閾值之前的R/W周期數)

額外的制造復雜性(例如成本)

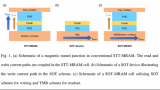

STT-MRAM是目前采用速度最快的嵌入式內存技術。位元的“磁隧道結”(MTJ)的截面如圖所示。電池由兩層鐵磁層組成,被一層薄薄的隧道氧化物隔開。“自由層”的磁極化隨寫入電流的方向和大小而改變。無論自由層的極化與參考層是“平行”還是“反平行”,通過這些層的電阻有很大的不同。

MTJ截面

用于STT-MRAM的磁隧道層和電子隧道層很容易制作和蝕刻。MTJ滿足典型的嵌入式flash需求,如第一個圖所示,它具有高粒度尋址能力的巨大優勢。

對于上面列出的高要求性能和持久性的嵌入式內存應用程序集,STT-MRAM技術特性將需要持續的研發投資。

STT-MRAM高性能和耐久性

在最近的VLSI 2020研討會上,來自GLOBALFOUNDRIES的一個團隊介紹了一種全新高性能STT-MRAM產品。他們開發了一種新的MTJ材料層堆棧,以優化讀訪問時間并同時顯著地延長持久周期的次數。

下表給出了這個新的STT-MRAM IP的總體規范:

requirements table

(高性能應用程序的持久性目標是使用10nsec寫入脈沖的比特錯誤率(BER)限制1E-06 (1 ppm)來定義的。)

與類似eflash的替換設計相比,這種高性能電池的保留性能在125攝氏度時降低到了10秒。(在125C時保持10秒相當于在85C時保持1周。)這將需要一個低開銷的刷新周期。

GLOBALFOUNDRIES團隊在陣列實現中添加了幾個奇特的工程優化:

MTJ陣列采用自適應工作電壓

讀出放大器Trim處于最佳性能

例如,Write1和Write0電流方向的電壓偏置適于響應內部溫度傳感器。所需的Vop在較低的溫度下更高,例如,與25℃相比,在-40℃時為+10%(在125C時為-16%)。這是由于在低溫下更高的“脅迫”磁場(coercive magnetic field),必須被克服來改變極化。

Vop versus T

下面的強調了GLOBALFOUNDRIES在研討會上提供的技術認證數據。

第一個顯示了具有不同寫入脈沖寬度的兩個不同MTJ材料堆的中BER,作為Vop的函數。堆棧“C”被優化為單寫脈沖10nsec。(注意,較長的電流脈沖和/或多個脈沖,可能包括一個中間的讀-驗證操作,提高了誤碼率。)

write cycle BER

下面的圖說明了在125C下的堆棧“C”的讀存取周期的誤碼率,并帶有檢測放大器的修整。

read cycle BER

STT-MRAM可靠性評估

進行可靠性評估,以確保沒有相鄰位元“干擾”失敗。

STT-MRAM陣列的耐久性規范要求開發一個MTJ壽命模型,使用加速電壓和溫度條件下的BER數據。(使用足夠的陣列數據所需的時間太長,因此必須采用其他破壞機制模型常用的加速應力技術。)GLOBALFOUNDRIES團隊指出,對于傳統器件柵氧化物的隨時間變化的介電擊穿(TDDB)有大量的模型參考,但迄今為止,對MTJ壽命擊穿機制的模型還很少。

耐久性數據(1ppm BER)的結果為如下所示的可靠性模型:

endurance model

該圖說明了模型外推到》1E12在-40C的耐久周期,使用10nsec的最積極的寫入周期脈沖。對于高于-40攝氏度的溫度(較低的Vop)和較大的寫入脈沖寬度,這種優化的MTJ堆棧的持久周期數將會大得多。

通過大量的研發工程,GLOBALFOUNDRIES團隊展示了一種新型MTJ材料堆棧,提供了STT-MRAM陣列的“高性能”變體。雖然該技術的初始IP提供了一個有吸引力的替代非易失性eFlash,這一新技術推動STT-MRAM進入一個極具競爭力的位置。

延伸閱讀——STT-MRAM存在的兩個弊端

隨著自旋轉移矩效應的發現以及材料和結構的優化,基于自旋轉移矩效應的STT-MRAM器件應運而生。自從自旋轉移矩效應被證實以來,一方面研究人員通過大量的努力嘗試降低磁化反轉的臨界電流,增加熱穩定性。

早期的磁隧道結采用面內磁各向異性(In-Plane Magnetic Anisotropy)。它存在如下兩個弊端:

1)隨著工藝減小,熱穩定性惡化。采用面內磁各向異性磁隧道結的存儲壽命取決于熱穩定性勢壘和磁各向異性場,面內磁各向異性的來源是薄膜平面較大的長寬比。

隨著工藝尺寸的微縮(<50nm),這種薄膜的邊際效應加劇,會產生顯著的磁渦旋態,難以保持較高的熱穩定性勢壘,甚至穩定的磁化也無法存在,這將限制MRAM的存儲密度;

其次面內磁各向異性的磁隧道結降低了自旋轉移矩的翻轉效率

因此,對于相同的熱穩定性勢壘,垂直磁各向異性能夠使磁隧道結的臨界翻轉電流比面內磁各向異性的更低,相應地,自旋轉移矩的翻轉效率更高。鑒于上述優勢,研究人員也一直致力于采用垂直磁各向異性的磁隧道結結構建高密度、低功耗的pSTT-MRAM。

垂直磁各向異性的磁隧道結;沿面內和垂直方向的磁化曲線,證明易磁化軸沿垂直方向。

責任編輯:pj

-

放大器

+關注

關注

143文章

13583瀏覽量

213368 -

存儲器

+關注

關注

38文章

7484瀏覽量

163765

發布評論請先 登錄

相關推薦

燃料電池測試負載如何進行負載測試?

耐久性測試:氙燈加速老化測試

控制器為什么要進行耐久試驗

LMS 耐久性測試解決方案

M8_4pin接口耐久性怎么樣

應用 Simcenter 試驗系統優化疲勞耐久試驗流程

MCU制程工藝邁進28nm時代,汽車行業的創新之路

MRAM HS4MANSQ1A-DS1在汽車電子中的應用

PSoC? 6 中嵌入式閃存的正確最低耐久性是多少?

瑞薩電子宣布已開發具有快速讀寫操作的測試芯片MRAM

臺積電引領新興存儲技術潮流,功耗僅為同類技術的1%

總結STT-MRAM高性能和耐久性

總結STT-MRAM高性能和耐久性

評論