1、引言

多數手機電視標準采用了OFDM 技術,但對于OFDM信號,載波頻偏將破壞信號子載波問的正交性,引入載波間干擾.一個小的頻偏就可能導致SNR的降低,所以,在OFDM的手機電視系統中,精確估汁并校正載波頻率偏差是非常重要的一部分。

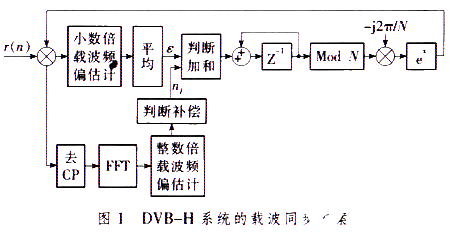

以DVB-H系統為例,整數倍頻偏采用連續導頻進行相關估計的算法,小數倍頻偏采用通過整數倍頻偏估汁修正與估汁值自平均相結合的算法,同時給出了硬件實現架構。

2、基于DVB-H的載波同步方案

系統的載波同步的算法一般都是基F信號幀結構中的已知信息。以DVB-H系統為例,其信號幀結構中的已知信息為時域上的循環前綴CP以及頻域上的按固定規律出現的連續導頻和離散導頻。因此通常在FFT前用循環前綴粗估計小數載波頻偏的值,而在FFT之后用連續導頻或離散導頻檢測整數倍載波頻偏值以及精細估計小數倍載波頻偏的值。但是這種傳統算法精細估汁小數倍載波頻偏計算復雜度高,硬件實現復雜。本文采用了一種用循環前綴估汁小數倍載波頻偏,FFT后用連續導頻估計整數倍頻偏,同時對小數倍頻偏進行修正的方案,簡化了汁算復雜度,易于硬件實現、本方案綜合考慮了估計精度和硬件的可實現性,如圖1所示。

在時域上基于CP對小數倍載波頻偏的快速捕獲,通過平均模塊對連續n幀得到的估計值ε進行平均,進一步減小隨機噪聲的影響。FFT之后,在頻域上利用相鄰兩個OFDM符號的連續導頻信號進行相關估出整數倍載波頻偏,并判斷小數倍載波頻偏是否在±0.5以內,對在時域上估計的小數倍頻偏進行修正。頻域估計得到的整數倍載波頻偏估汁值反饋到接收信號的時域端,與平均模塊后的小數倍載波頻偏估計值相加進行載波頻偏補償。

2.1小數倍載波頻偏估計算法

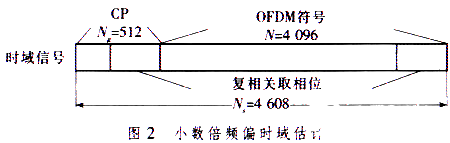

在發送端,循環前綴是每幀有效數據的最后一部分的復制,如圖2所示。循環前綴與每幀有效數據的最后一部分幅值相同,區別是有一個相位的旋轉,這個相位正比于載波頻偏,可根據這個相位旋轉估計得到小數倍載波頻偏。

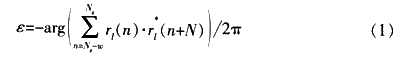

具體算法為利用循環前綴開窗與數據進行相關,為盡量減少其受上一幀數據污染的可能性,開窗的位置越靠后越好。相關值在開窗范圍內做平均取相位再除以-2π便可求得在多徑信道情況下估計得到的小數倍載波頻偏

式中:ω為開窗長度。

2.2整數倍載波頻偏估計算法

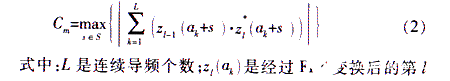

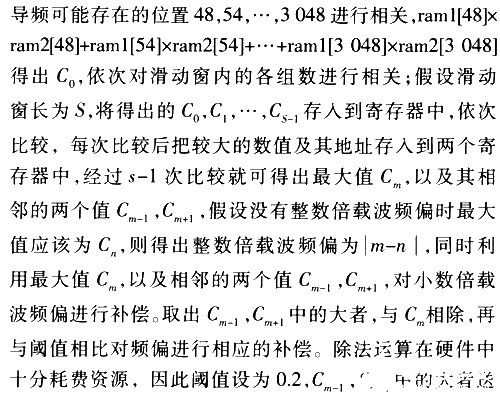

在小數倍頻偏進行估計和補償之后,載波頻偏在頻域上的一個主要影響表現在子載波的循環移位,可利用處于每幀OFDM符號中特定子載波位置上的連續導頻來進行載波頻偏的估計。由于連續導頻在每一幀中的固定位置上出現,自相關性好,對連續兩幀OFDM符號在連續導頻的位置進行復相關并求和,使用一個長為S的滑動窗作為頻域上子載波有可能的相對偏移范圍,這樣得到S個相關值,其中最大相關值所對應的s即為頻域上子載波的相對偏移,即整數倍載波頻偏的估計值

個符號的第κ個連續導頻位置上的復數值;S是整數倍頻偏的估計范圍;s是窗口移動值,s∈S;S路相關和的最大值Cm對應的s即為整數倍載波頻偏的估計值m。

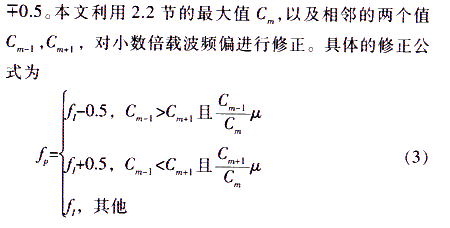

2.3小數倍載波頻偏修正算法

如果小數倍頻偏在±0.5以內時,僅用2.1節算法的估計值與實際值相比有可能出現跳變,即+0.5估計成

式中:μ為預先設定的閾值,一般設為0.2,經過整數倍頻偏估計對小數倍頻偏的補償處理,一般可使剩余的小數倍頻偏在-0.25~+0.25之間,這樣可避免小數倍載波頻偏在+0.5內估計出的ε存在跳變的可能,以提高估計的準確度。

3、DVB-H載波同步的硬件實現

3.1小數倍載波頻偏估計的硬件實現

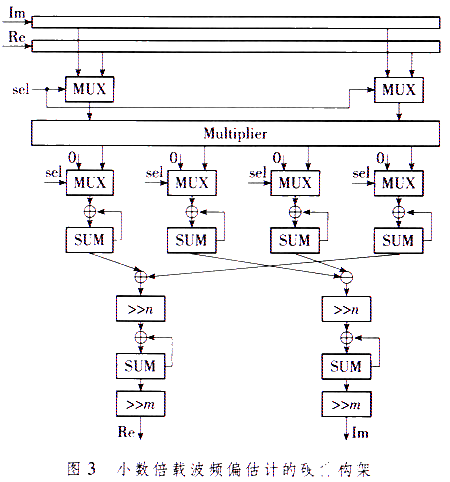

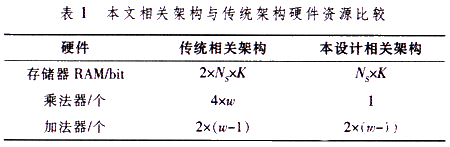

根據2.1所述的算法原理及公式(1),假設開窗長度為ω,OFDM符號長為Nc,每個有效數據為K bit,對于每個OFDM符號要進行4×w次乘法,2×(ω-1)次加法,同時要兩塊RAM,每塊容量為Ns×K bit,一塊存儲當前OFDM符號,另一塊為讀取上一個OFDM符號的內容進行相關運算。 圖3的硬件構架,考慮到每次估計之間的時間間隔為Ng個時鐘(循環前綴CP的長度),足夠進行相關運算,因此可對RAM進行復用。同時通過選擇控制信號對乘法器進行復用,僅要一個乘法器就可實現運算。

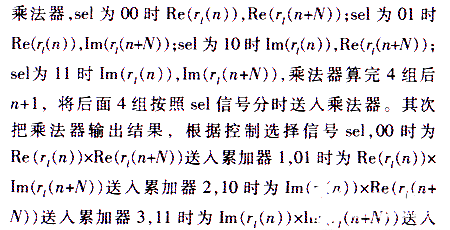

首先產生控制信號,選擇窗內數據的實部,虛部分別依次存入長為64的FIFO,此處窗長設為64。根據控制選擇信號sel,用流水方式將下面4組信號分時送入

累加器4進行累加。一幀估計完后,把累加器1與累加器4的值再送入加法器得出估計的實部,把累加器2與累加器3的值送入減法器得出估計的虛部。然后對估計值做平均,為了硬件實現方便,窗長選為64,因此將結果送入移位器右移6位,即可對累加結果做平均。最后對連續8幀的估計值,通過累加器移位器累加并右移3位做平均,進一步降低隨機噪聲的影響。表1比較了本設計與傳統相關架構的硬件資源。

由表1可見,本文架構在加法器數量不變情況下,存儲器容量節省一半,特別是對FPGA中十分稀缺的乘法器資源,節省了4w-1個,相關窗越長節省的數量越大。

3.2整數倍頻偏估計及小數倍頻偏修正的硬件實現

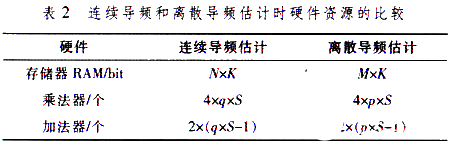

對于整數倍載波頻偏估計來說,輸入數據去掉循環前綴CP,再經過FFT得到頻域數據,可利用連續導頻或離散導頻估計載波頻偏,兩者均采用相關的方法。表2比較了連續導頻和離散導頻時所需硬件資源的情況。

表2中Ⅳ為一個OFDM符號中的子載波的個數;M為離散導頻循環一次所包含的子載波個數;K為每個子載波信號的比特數;q為一個OFDM符號中連續導頻的個數;p為離散導頻循環一次所包含的離散導頻的個數,S為滑動相關窗長。一般有M》N,p》q,因此離散導頻整數倍載波頻偏估計的算法比連續導頻的估計算法要用到更多的存儲器、乘法器和加法器資源。連續導頻的方法已能準確地估計出整數倍載波頻偏,不必再用離散導頻的算法來進行整數倍載波頻偏估計。

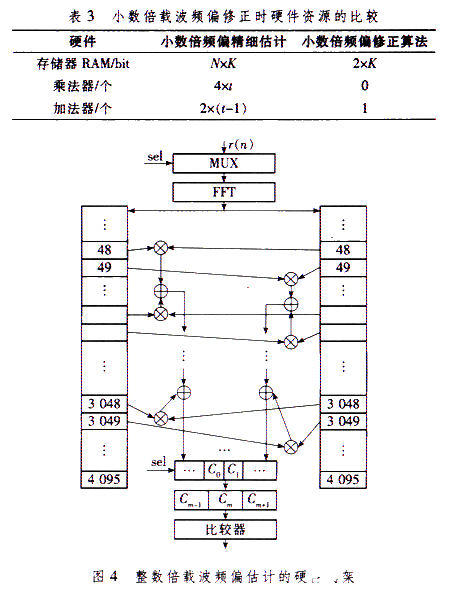

對于小數倍載波頻偏估計來說,如果小數倍頻偏在±0.5以內時,估計值和實際值相比有可能出現跳變,要想準確估計,通常需要許多個OFDM符號利用連續導頻或離散導頻進行精細估計。而本文對小數倍頻偏估計采用通過整數倍頻偏估計修正與估計值自平均相結合,由于利用了整數倍載波頻偏估計中的運算結果,并通過合理的設置參數,僅需用一個移位器,一個加法器和一個比較器就可在保持一定精度的前提下大大節省運算量。

表3中的Ⅳ為利用連續或離散導頻進行小數倍頻偏精細估計一次所利用的子載波個數;K為數據的比特數;t為進行一次估計所用的連續或離散導頻數。從表3可以看出利用連續導頻或離散導頻對小數倍載波頻偏進行精細估計,硬件實現計算復雜,十分耗費資源。而利用本文的通過整數倍頻偏估計修正算法可以大大節省硬件資源。 整數倍載波頻偏估計的硬件實現構架如圖4所示。首先對輸入的數據送入選擇器去除循環前綴CP,送人

FFT模塊;為了運算的速度和數據的連續性使用乒乓操作,在第一個緩沖周期,將連續兩幀數據緩存到數據緩沖模塊1,2,在第二個緩沖周期通過輸入數據選擇信號將其后的兩幀數據緩存人數據緩沖模塊3,4,同時把在第一個緩沖周期存入數據緩沖模塊l,2的數據送入數據運算模塊進行運算處理,如此循環進行。運算模塊的具體運算過程如下:將連續兩幀信號存入兩個深度為4 096的RAM中,依次讀出連續導頻在滑動相關窗內的數,并把這些數存入寄存器進行相關。例如圖4中對于一組連續入移位器左移5位,與C。送入減法器,比較符號位就可以得出頻偏補償的結果。

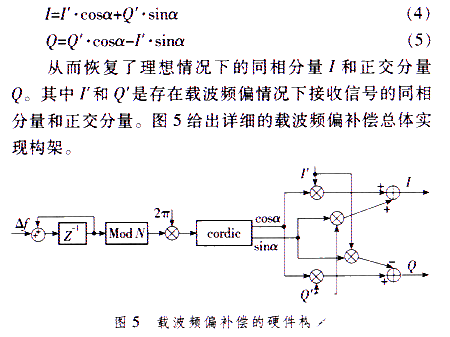

3.3載波頻偏補償的硬件實現

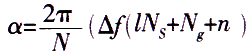

把頻域估計得到的整數倍載波頻偏估計值反饋到接收信號的時域端,與平均模塊后估計的小數倍載波頻偏估計值相加構成△f進行補償。時域上的相偏補償是乘以一個相反的相位α,可推導得到

首先,估計出的載波頻偏經過累加器、取模器、乘法器得到

,然后經過cordic模塊計算得到其正弦、余弦值,最后根據式(4),(5)進行補償,同相分量與余弦值送入乘法器得到的值送入寄存器1,同時正交分量與正弦值送入乘法器,得到的值送入寄存器2,寄存器1和寄存器2的值送入加法器得到無載波頻偏的同相分量;正交分量與余弦值送入乘法器得到的值送入寄存器3,同時同相分量與正弦值送入乘法器得到的值送入寄存器4,寄存器3與寄存器4的值送入減法器得到無載波頻偏的正交分量。

其中正弦和余弦值的計算采用cordic算法代替查找表,保證了一定的精度的條件下大大節約了存儲資源。圖6為cordic硬件實現構架。

4、 小結

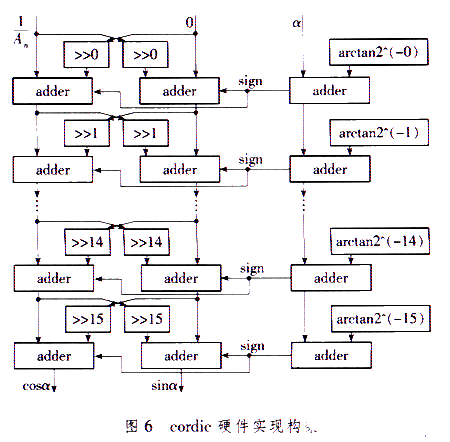

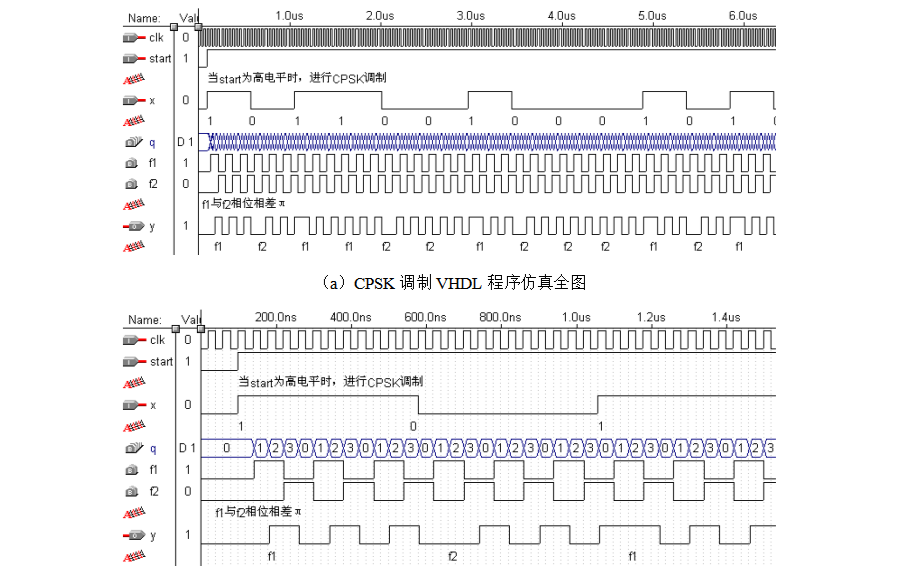

本文基于已有的算法,以DVB-H系統為例,對其載波同步提出了一種方案及硬件實現架構。對上述架構利用Verilog硬件描述語言進行了實現,用ModelSim SE5.7進行了仿真,同時用Quartus II 6.O進行了綜合,選用芯片EP2C70F672C8。整數倍載波頻偏估計模塊最高時鐘頻率可達87 MHz,所用的M4k為48個,LE約為3 800個,乘法器為12個;小數倍載波頻偏估計模塊最高時鐘頻率可達102 MHz,所用的M4k為2個,LE約為184個,乘法器為1個;載波頻偏補償模塊最高時鐘頻率可達73 MHz,所用的LE約為2 000個,乘法器為8個。本文提出的硬件實現架構,速度快,節省硬件資源。

責任編輯:gt

-

芯片

+關注

關注

459文章

52112瀏覽量

435543 -

仿真

+關注

關注

51文章

4230瀏覽量

135268 -

Verilog

+關注

關注

28文章

1365瀏覽量

111745

發布評論請先 登錄

評論