題目:數(shù)制轉換

R進制數(shù)轉換為十進制數(shù):按權展開,相加

十進制數(shù)轉化為R進制數(shù):整數(shù)部分,除R取余法,除到商為0為止。小數(shù)部分,乘R取整法,乘到積為0為止。

二進制數(shù)轉化八進制數(shù):三位一組,整數(shù)部分左邊補0,小數(shù)部分右邊補0。反之亦然。

二進制數(shù)轉化十六進制數(shù):四位一組,整數(shù)部分左邊補0,小數(shù)部分右邊補0。反之亦然。

題目:邏輯函數(shù)及其化簡

公式法

卡諾圖法

題目:什么是冒險和競爭,如何消除?

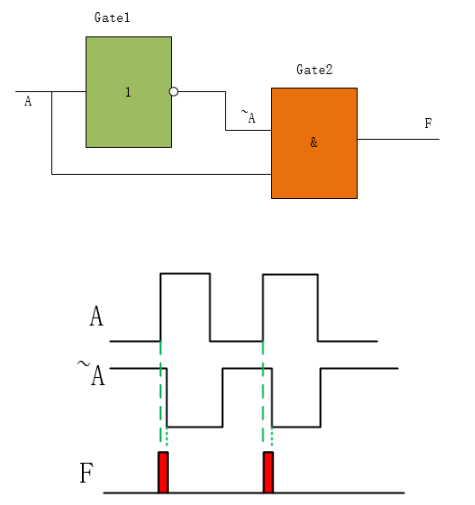

下面這個電路,使用了兩個邏輯門,一個非門和一個與門,本來在理想情況下F的輸出應該是一直穩(wěn)定的0輸出,但是實際上每個門電路從輸入到輸出是一定會有時間延遲的,這個時間通常叫做電路的開關延遲。而且制作工藝、門的種類甚至制造時微小的工藝偏差,都會引起這個開關延遲時間的變化。

實際上如果算上邏輯門的延遲的話,那么F最后就會產生毛刺。信號由于經(jīng)由不同路徑傳輸達到某一匯合點的時間有先有后的現(xiàn)象,就稱之為競爭,由于競爭現(xiàn)象所引起的電路輸出發(fā)生瞬間錯誤的現(xiàn)象,就稱之為冒險,FPGA設計中最簡單的避免方法是盡量使用時序邏輯同步輸入輸出。

加濾波電容,消除毛刺的影響

加選通信號,避開毛刺

增加冗余項,消除邏輯冒險。

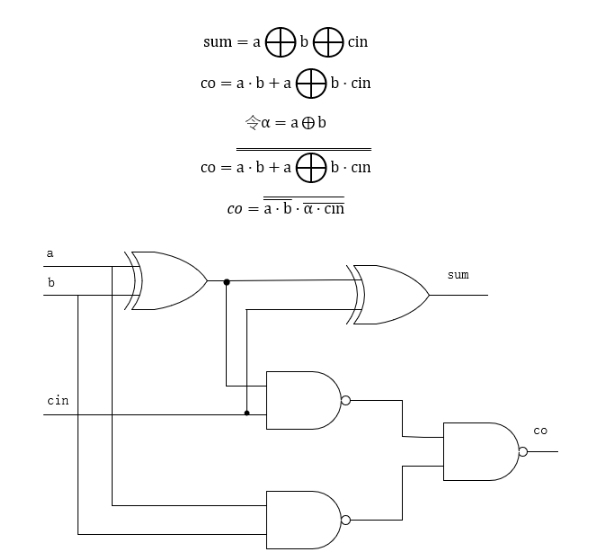

題目:用與非門等設計一個全加法器

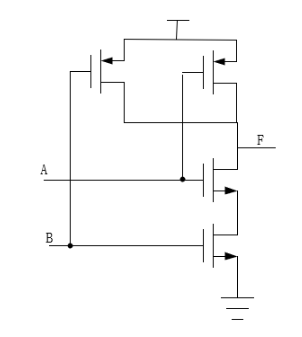

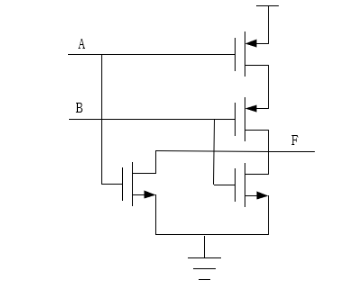

題目:MOS邏輯門

與非門:上并下串(上為PMOS,下為NMOS)

或非門:上串下并(上為PMOS,下為NMOS)

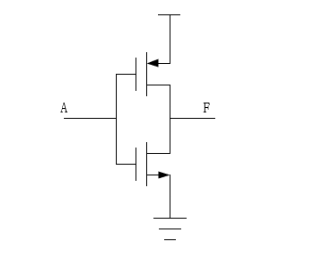

反相器(上為PMOS,下為NMOS)

練習:畫出Y = A·B + C的CMOS電路圖

Y = (A·B + C)” = ((A·B)’·C’)’,一個反相器,兩個而輸入與非門。

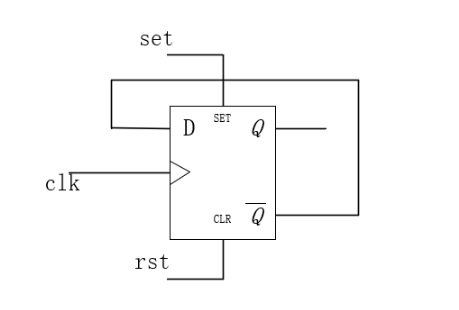

題目:用D觸發(fā)器帶同步高置數(shù)和異步高復位端的二分頻的電路,畫出邏輯電路,Verilog描述。

reg Q;

always @(posedge clk or posedge rst)begin

if(rst == 1‘b1)

Q 《= 1’b0;

else if(set == 1‘b1)

Q 《= 1’b1;

else

Q 《= ~Q;

end

題目:ASIC中低功耗的設計方法和思路(不適用于FPGA)

合理規(guī)劃芯片的工作模式,通過功耗管理模塊控制芯片各模塊的Clock,Reset起到控制功耗的目的。

門控時鐘(Clockgateing):有效降低動態(tài)功耗

多電壓供電:通過控制模塊的電壓來降低功耗

多閾值電壓

-

FPGA

+關注

關注

1646文章

22092瀏覽量

620486 -

反相器

+關注

關注

6文章

321瀏覽量

44398 -

加法器

+關注

關注

6文章

183瀏覽量

30872 -

非門

+關注

關注

1文章

33瀏覽量

34364 -

與門

+關注

關注

0文章

24瀏覽量

3775

發(fā)布評論請先 登錄

第九屆集創(chuàng)賽“法動杯”燃爆七大賽區(qū)

電機選型計算公式與知識點匯總

中國集成電路大全 接口集成電路

華邦電子安全閃存關鍵知識點

數(shù)字電路設計中:前端與后端的差異解析

數(shù)字電路有哪些特點和作用

數(shù)字電路與控制系統(tǒng)關系

數(shù)字電路編程語言介紹

數(shù)字電路與模擬電路的區(qū)別

模擬電路與數(shù)字電路的區(qū)別

Aigtek功率放大器應用:電感線圈的知識點分享

評論