軍隊靶場訓練基地用于跟蹤高速運動目標的主要手段是光電跟瞄設備。對于光電跟瞄系統而言,操作訓練需要外部目標環境的緊密配合,因此,訓練所需的目標環境構建成為對操作手訓練和對光電跟瞄設備仿真檢測的關鍵因素之一。如果通過現場飛行試驗來構造目標環境,則訓練成本過大,還受到天氣等環境因素的影響。因此,如何低成本而又高效率地完成操作訓練是目前困擾相關軍事單位的一個難題。

目前,在靶場訓練的項目中,通過研制目標模擬器來構造目標環境,并采用虛擬場景注入的方法來實現。該方法通過事先錄制好一段目標場景的圖像,操作手根據觀看播放的錄像,操縱光電跟瞄設備對錄像中的目標進行跟蹤捕獲訓練。但此方法沒有反饋,而且實時性較差。本文提出一種新的虛擬圖像注入方法。該方法實時獲得跟蹤設備及目標的運行參數,根據速度追蹤原理模擬生成目標及背景的圖像數據,從而達到跟蹤訓練的目的。該方法實現簡單方便、可操作性強,更加注重操作手對光電跟瞄設備操縱的性能。

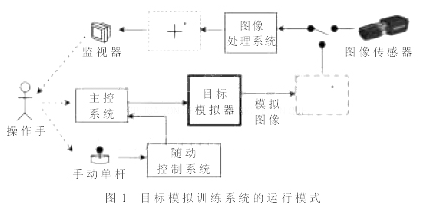

1 目標模擬訓練系統的運行模式

在工作過程中,首先由操作手根據訓練需要設定目標模擬的速度、機動特性等初始參數并送到主控系統;按照設定的目標運行特點在每幀待輸出圖像上設定、調整目標位置;目標模擬器通過主控計算機接收編碼器位置信息,并解算設備運行速度,根據速度追蹤原理輸出實時跟蹤的圖像數據;將圖像處理系統轉換到接收目標模擬器輸出圖像信息的模式;圖像處理器將疊加十字絲的視頻圖像傳送給操作手的監視器;操作手操作單桿控制伺服系統運轉,使回轉平臺運轉對目標進行模擬捕獲;最后,圖像處理器根據編碼器返回數據實時調整目標位置,完成對目標捕獲過程的模擬訓練。系統運行模式如圖1所示。

2 數學建模

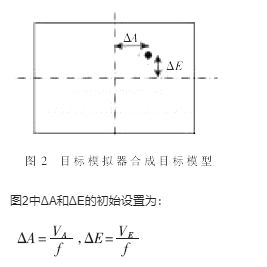

目標模擬器的數學模型基于速度追蹤原理:假設目標按照特定速度與設備視軸做等速運動,該速度在單幀合成圖片中體現為位置脫靶量,如圖2所示。

當操作手開始進行手動跟蹤時,目標仿真圖像的調整數學模型為:

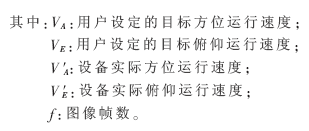

3 硬件設計

目標模擬器由串口轉換模塊、DSP模塊、FPGA模塊、Camera Link接口模塊組成,結構如圖3所示。

DSP采用TI公司的TMS320F2812芯片,它是目前用于控制領域的最高性能的處理器,具有控制精度高、速度快、使用靈活以及集成度高等優點,運行速率可達150 MIPS,指令采用流水線處理,使得數據處理的能力大大增強。設計中主要利用其串行通信(SCI)接口、外部中斷(XINTx)接口和外部擴展(XINTF)接口。通過與主控計算機進行通信,接收模擬目標和跟蹤設備的參數,并根據建立的數學模型解算出目標及設備的坐標,實時生成目標及背景的圖像數據,同時接收時統的同步中斷信號。

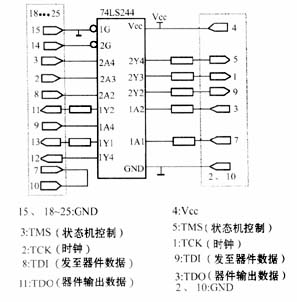

設計中選用MAXIM公司的MAX3070芯片進行RS-422到RS-232協議的轉換,利用DSP2812的SCI模塊實現與主控計算機的通信。把MAX3070的DI腳與DSP2812的SCITXD相連,RO與DSP2812的SCIRXD相連,同時為了保證順利地與主控計算機通信,允許接收RE#腳直接接地,允許發送DI腳直接接VCC。加上兩個電阻以及去耦電容實現了串行通信接口的硬件設計。DSP2812通過外部擴展接口(XINTF)與FPGA進行數據傳遞,將XWE#引腳作為寫使能信號與FPGA的I/O腳相連,將XCLKOUT引腳作為寫時鐘信號與FPGA的I/O腳相連,將16位數據線與FPGA的I/O腳相連,來傳送圖像數據信號。

FPGA以ALTERA公司的Cyclone II系列的EP2C8-Q208C8芯片作為目標模擬器的時序和邏輯控制核心。EP2C8Q208C8具有8 256個的邏輯單元(LE)、165 888 bit基于流行的M4K嵌入式存儲器塊,可以配置為廣泛的操作模式,包括ROM、單端口和雙端口RAM等。設計中用芯片內部的雙端口RAM構造異步FIFO控制圖像數據的時序,加上幀同步(FVAL)和行同步(LVAL)信號一起按照紅外圖像的設計時序要求將圖像數據發送到Camera Link接口模塊。

Camera Link接口采用DS90CR287作為驅動芯片,是專用的電平轉換器件,能將28位CMOS/TTL電平數據和1位像素時鐘信號分別轉換成4組LVDS數據流及一對LVDS時鐘信號進行傳輸。由于采用差分傳輸方式,提高了傳輸距離及信號精度。使用標準的MDR26作為Camera Link接口與圖像采集卡之間的連接接口。

4 軟件設計

目標模擬器的軟件設計主要由DSP程序和FPGA程序組成。

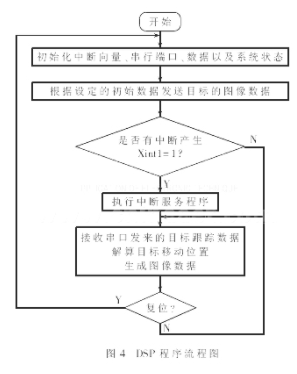

DSP程序流程圖如圖4所示。由于生成圖像數據要通過DSP芯片的外部接口XINTF發送,DSP2812有5個固定的存儲映像區域,設計中采用ZONE2區作為映像區域,所以首先要解決數據存儲映像的問題。本設計采用CCS提供的下面兩個指令實現數據映像。

#pragma CODE_SECTION 針對程序空間;

#pragma DATA_SECTION 針對數據空間;

具體程序實現如下:

#pragma DATA_SECTION(pRGB,″My_Sect″)

struct

{ Uint16 r;

Uint16 w;

}pRGB[320][240];

在.cmd文件中建立對應的section就可以使用了。

MEMORY

{PAGE1: ZONE2 :origin=0x080000,length=0x080000 }

SECTIONS

{My_Sect :》ZONE2, PAGE=1 }

建立映像后要設置XINTF的相應寄存器值,對于外部接口的訪問主要分為3個階段:(1)建立階段:被訪問區的片選信號變為低電平,地址被放置在地址總線上;(2)激活階段:對外部器件進行訪問。本設計主要是寫訪問,寫使能(XWE#)選通變低并將數據放置在數據總線上(XD);(3)跟蹤階段:跟蹤階段為一保持時間,其片選信號為低,而后讀和寫選通變為高[1]。

具體設置如下:

XintfRegs.XTIMING2.bit.XWRLEAD=1

XintfRegs.XTIMING2.bit.XWRACTIVE=1

XintfRegs.XTIMING2.bit.XWRTRAIL=1

建立、激活、跟蹤分別為1個時鐘周期。

DSP2812的串行通信(SCI)模塊使用16位的波特率選擇寄存器(SCIHBAUD和SCILBAUD)設置SCI的波特率,因此SCI可以采用64 K種不同的波特率進行通信,通過下面的公式計算出寫入寄存器的值:

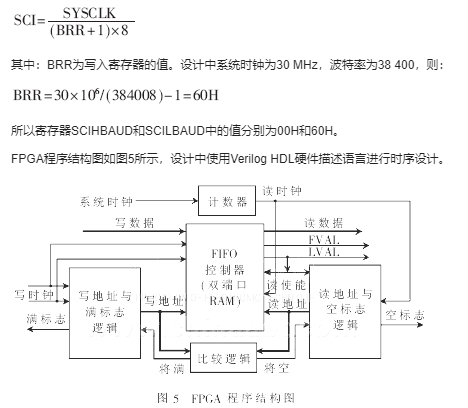

從圖5可以看出,采用模塊化的設計方法,圖像數據的寫操作和讀操作分別工作在兩個不同的時鐘域內,數據的寫入是連續的,數據的讀出是按照一定的幀頻和行頻進行的。本設計采用雙端口RAM構造異步FIFO的方法來實現。一方面要解決異步FIFO設計中存在的難點;另一方面要與Camera Link接口進行視頻數據的同步控制,生成場同步信號FAVAL和行同步信號LVAL。

整個程序可分為6個模塊。其中FIFO控制器模塊中包含一個雙端口RAM,用來存儲數據及控制讀寫操作;寫地址與滿標志邏輯生成寫地址并產生滿標志,寫地址和寫使能由DSP提供;讀地址與空標志邏輯生成讀地址并產生空標志,讀時鐘由系統時鐘通過計數分頻得到。因為讀操作要在LVAL信號的控制下完成,所以讀使能信號使用LVAL,其中空、滿狀態通過增加標志位和劃分地址空間來產生;比較邏輯用來異步比較讀、寫地址,并產生將滿、將空信號,其中讀、寫地址用格雷碼指針表示。該設計很好地解決了異步FIFO設計中存在的兩個關鍵問題,即降低了電路中亞穩態的出現概率,正確產生了空、滿狀態邏輯。FVAL和LVAL的計算方法如下所述。

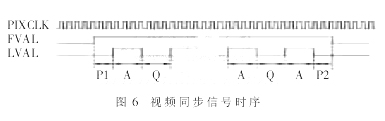

設計中像素時鐘信號PIXCLK的頻率為10 MHz。模擬的圖像數據的像素為320×240,幀頻為50 Hz,即每秒傳輸50幀圖像。行同步信號LVAL和幀同步信號FVAL均由像素時鐘信號進行計數產生,其時序如圖6所示。

圖6中,P1為35個PIXCLK時鐘周期;A為320個PIXCLK;即一行包含320個像素點;Q為47個PIXCLK;P2為13個PIXCLK,幀同步信號FVAL為低電平的時間是111 872個PIXCLK。一幀圖像包含240行有效數據,可計算出傳輸一幀圖像信號的時間為240×(A+Q)+P1+P2+111 872=200 000個PIXCLK時鐘周期,幀頻為10 MHz÷200 000=50 Hz。

5 實驗結果

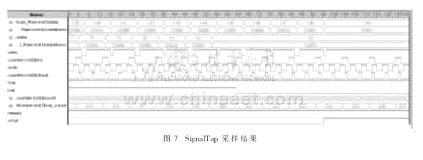

將DSP程序和FPGA程序下載到實驗板中,使用開發工具Quartus II6.0中自帶的邏輯分析儀SignalTap對試驗中的主要信號進行采樣監測,采樣結果如圖7所示。其中data為寫入數據,wraddress為寫地址,rdata為讀出數據,raddress為讀地址。當行有效信號lval為低時讀操作停止,當寫滿信號為高時數據停止寫入。結果表明信號時序準確,數據和地址沒有毛刺現象。最后將實驗板連接到圖像采集卡,模擬的圖像像素是320×240,頻率是50 Hz,通過觀看采集卡采集的圖像,表明圖像時序穩定,能夠達到設計要求。

設計中采用新的虛擬圖像注入方法的目標模擬器為訓練系統提供目標的圖像數據,該方法實現簡單。基于Camera Link接口協議的圖像信號采用LVDS方式傳輸,增加了傳輸距離,提高了傳輸過程中的信號精度。經過試驗測定圖像數據信號穩定、可靠,各項指標與目前光電跟瞄設備采用的紅外熱像儀輸出圖像格式吻合,實時性滿足要求,能夠很好地完成操作手對光電跟瞄設備的跟蹤訓練和日常維護的任務。

責任編輯:gt

-

處理器

+關注

關注

68文章

19259瀏覽量

229653 -

編碼器

+關注

關注

45文章

3638瀏覽量

134427 -

計算機

+關注

關注

19文章

7488瀏覽量

87852

發布評論請先 登錄

相關推薦

基于智能語音交互芯片的模擬訓練器示教與回放系統設計

簡述電子對抗綜合模擬訓練平臺

某型導彈模擬訓練器發控系統設計

仿實裝的多功能模擬訓練系統設計

消防模擬訓練環境控制系統硬件電路設計

EPM7128S在雷達電子干擾模擬訓練器中的應用

某型航空偵察平臺模擬訓練系統的研制

Flash實現雷達模擬訓練軟件

軟件復用技術在雷達模擬訓練中的應用

空管模擬訓練中指令的語音識別與合成技術研究

某大型機電設備模擬訓練系統總體設計

基于STM32F407和MAX7349的超短波電臺模擬訓練系統設計與實現

基于速度追蹤原理實現目標模擬訓練系統的設計

基于速度追蹤原理實現目標模擬訓練系統的設計

評論