引 言

雷達(dá)作為一種特殊的無(wú)線電裝備,也必然遵循從模擬到數(shù)字再到軟件化這樣的發(fā)展道路。數(shù)字波束形成技術(shù)被視為新一代雷達(dá)所必須采用的技術(shù),它保留了天線陣列單元信號(hào)的全部信息,并可采用先進(jìn)的數(shù)字信號(hào)處理技術(shù)對(duì)陣列信號(hào)進(jìn)行處理,可以獲得優(yōu)良的波束性能,方便地得到超分辨和低副瓣的性能,實(shí)現(xiàn)波束掃描、自校準(zhǔn)和自適應(yīng)波束形成等。正是由于以上特點(diǎn),DBF技術(shù)的成功應(yīng)用必將對(duì)現(xiàn)代雷達(dá)技術(shù)的發(fā)展產(chǎn)生重大的影響。

在數(shù)字波束形成技術(shù)的工程化過(guò)程中,也遇到了一些問(wèn)題。主要包括:數(shù)據(jù)傳輸量太大,尤其當(dāng)陣元數(shù)較多時(shí),這樣就限制了通道的增加;來(lái)波方向估計(jì)和權(quán)值更新計(jì)算量太大,使得權(quán)值更新速度比較慢,無(wú)法在一些高速運(yùn)動(dòng)的載體上使用;當(dāng)陣列數(shù)較多時(shí),高速實(shí)時(shí)波束形成器的復(fù)乘運(yùn)算耗費(fèi)較多的資源,尤其是需要形成多個(gè)波束的情況下。原來(lái)的DBF系統(tǒng)就遇到數(shù)據(jù)傳輸瓶頸問(wèn)題,采樣數(shù)據(jù)只能通過(guò)PCI總線進(jìn)行傳輸,無(wú)法保證所有通道的數(shù)據(jù)都實(shí)時(shí)傳輸,因而只能做需求數(shù)據(jù)較少的測(cè)向工作,并不能做實(shí)時(shí)波束形成。為了克服這些困難,這里將測(cè)向數(shù)據(jù)和波束形成數(shù)據(jù)分開進(jìn)行傳輸,采用LVDS技術(shù)解決多通道高速數(shù)據(jù)傳輸,選擇內(nèi)置高性能DSP內(nèi)核的高密度FPGA并行實(shí)現(xiàn)波束形成中的大量復(fù)乘運(yùn)算。

1 DBF系統(tǒng)組成

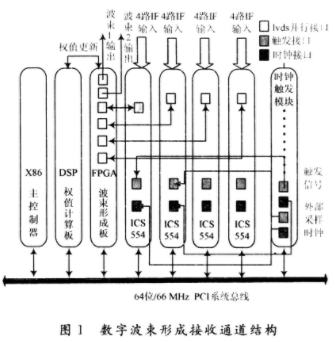

DBF系統(tǒng)包括陣列接收天線、多通道接收機(jī)、多通道數(shù)據(jù)采集板、FPGA波束形成板、DSP權(quán)值計(jì)算板、外部時(shí)鐘觸發(fā)模塊、工控機(jī)等單元,如圖1所示。接收機(jī)一般采用超外差方式,實(shí)現(xiàn)陣列接收信號(hào)的下變頻、濾波,并將信號(hào)放大至A/D變換所需的水平。DBF系統(tǒng)最主要的功能就是實(shí)現(xiàn)來(lái)波方向估計(jì)(測(cè)向)和波束形成,DSP權(quán)值計(jì)算板承擔(dān)來(lái)波方向估計(jì)和權(quán)值計(jì)算任務(wù),權(quán)值計(jì)算要根據(jù)測(cè)向結(jié)果和波束掃描,以及對(duì)抗干擾的要求綜合考慮得到,F(xiàn)PGA波束形成板承擔(dān)全陣波束形成任務(wù)。波束形成器根據(jù)權(quán)值計(jì)算結(jié)果,通過(guò)對(duì)數(shù)字化的陣列單元接收信號(hào)進(jìn)行復(fù)加權(quán)運(yùn)算,形成所需的接收數(shù)字波束。

該系統(tǒng)中,由4塊四通道采集板ICS554實(shí)現(xiàn)16陣元中頻信號(hào)的模/數(shù)轉(zhuǎn)換和數(shù)字下變頻。為了實(shí)現(xiàn)所有通道的同步,采集板均工作在外部信號(hào)觸發(fā)模式,外部采樣時(shí)鐘完全同步;來(lái)波方向估計(jì)和權(quán)值更新計(jì)算由DSP權(quán)值計(jì)算板完成,運(yùn)算需要的每個(gè)通道數(shù)據(jù)量通常并不大,ICS554將測(cè)向所需數(shù)據(jù)通過(guò)PCI總線傳送給DSP權(quán)值計(jì)算板;FPGA波束形成板要實(shí)現(xiàn)全陣的波束形成,就要對(duì)每個(gè)通道的數(shù)據(jù)復(fù)加權(quán)求和,得到最終所需的波束,因而需要傳輸數(shù)據(jù)量很大,4塊ICS554通過(guò)LVDS將高速數(shù)據(jù)傳輸?shù)紽PGA波束形成板;權(quán)值由DSP權(quán)值計(jì)算板計(jì)算完成后,通過(guò)自定義的串口通信發(fā)送到FPGA波束形成板。

2 實(shí)時(shí)數(shù)字波束形成器設(shè)計(jì)

2.1 高速數(shù)據(jù)采集與傳輸

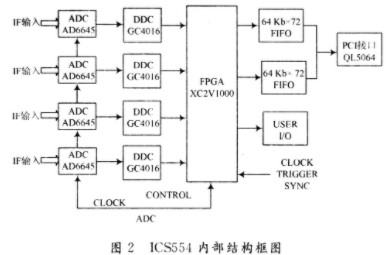

該系統(tǒng)中,由于信號(hào)帶寬比較寬,選擇ICS公司四通道的采集板ICS554實(shí)現(xiàn)數(shù)據(jù)采集任務(wù),ICS554是ADC和數(shù)字下變頻(DDC)集成化的產(chǎn)品。ADC決定了系統(tǒng)的動(dòng)態(tài)范圍,依據(jù)ADC的位數(shù)K,以每位6 dB增加,并隨著以dB表示的并行接收通道數(shù)目N增加。ICS554的組成如圖2所示,它主要包括4個(gè)獨(dú)立的14 b/105 MHz模/數(shù)變換器AD6645,4個(gè)正交下變頻器(QDDC)GC4016,1個(gè)100萬(wàn)門的用戶可編程FPGA(Xilinx XC2V1000),2個(gè)512 KB的FIFO和1個(gè)PCI接口芯片QC5064。其中,AD6645的輸入信號(hào)帶寬可達(dá)50kHz~200 MHz,最大無(wú)虛假動(dòng)態(tài)范圍(SFDR)為92 dB(10 MHz±50 kHz),每個(gè)GC4016內(nèi)部包括4個(gè)獨(dú)立的DDC通道,每個(gè)通道都可獨(dú)立控制其本振頻率和初始相位,頻率分辨優(yōu)于24 MHz,全頻段的覆蓋使得每個(gè)GC4016共享共同的射頻前端與A/D轉(zhuǎn)換器,大容量的FIFO用于緩沖輸出數(shù)據(jù),F(xiàn)PGA則可用于對(duì)輸出信號(hào)進(jìn)行初步處理。ICS554具有較高的穩(wěn)定性,優(yōu)異的非線性以及正交等系統(tǒng)特性,靈活性比較強(qiáng)。ICS554的可編程控制參數(shù)通過(guò)配置不同的寄存器來(lái)完成。

該系統(tǒng)共16個(gè)天線單元,A/D采樣頻率105 MHz,經(jīng)過(guò)數(shù)字下變頻后形成30 MHz的I,Q兩路24 b數(shù)據(jù)流,如果將所有數(shù)據(jù)傳輸?shù)胶蠖薋PGA波束形成板進(jìn)行處理,那么每塊ICS554采集板每秒需要傳輸?shù)臄?shù)據(jù)量為:

4×2×24×30 Mb/s=5.625 Gb/s

考慮到采集板ICS554并未提供更高性能的數(shù)據(jù)傳輸總線,要實(shí)現(xiàn)5.625 Gb/s流量的數(shù)據(jù)傳輸很困難,因此利用板上預(yù)留給用戶的FPGA資源,先在采集板中做一次子陣的波束合成,將同一采集板4通道的I,Q兩路數(shù)據(jù)進(jìn)行加權(quán)求和,得到合成的I,Q數(shù)據(jù),數(shù)據(jù)流量降低為1 440 Mb/s。

采集板ICS554與FPGA波束形成板之間的連接采用LVDS技術(shù),低電壓差分信號(hào)(Low Voltage Dif-ferential Signaling,LVDS)是一種用低擺幅的差分電壓串行傳輸信號(hào)的技術(shù)。這種信號(hào)能在差分PCB導(dǎo)線對(duì)或平衡電纜上以幾百M(fèi)b/s,甚至上Gh/s的速率傳輸,具有低電壓、低輻射、低功耗、低成本、強(qiáng)抗干擾能力和可內(nèi)含時(shí)鐘等優(yōu)點(diǎn),尤其適用于對(duì)傳輸距離有要求設(shè)備間的高速數(shù)據(jù)傳輸。但是,LVDS只定義了信號(hào)電氣規(guī)范,作為一個(gè)完整的數(shù)據(jù)通信規(guī)范還需要相應(yīng)的數(shù)據(jù)傳輸控制。為了提高效率,使用不含幀結(jié)構(gòu)的數(shù)據(jù)直接傳輸,同時(shí)為了盡量增加數(shù)據(jù)傳輸?shù)耐ǖ溃∠l(fā)送端和接收端之間的控制信號(hào),使用不連續(xù)的發(fā)送端時(shí)鐘.僅在發(fā)送端數(shù)據(jù)有效時(shí),給出發(fā)送時(shí)鐘。這種情況下,接收端可以使用一個(gè)高于發(fā)送時(shí)鐘的連續(xù)時(shí)鐘對(duì)發(fā)送時(shí)鐘進(jìn)行采樣來(lái)確定數(shù)據(jù)是否有效。

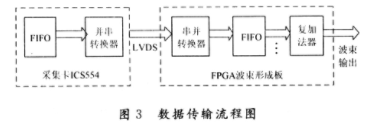

采集板ICS554本身給用戶預(yù)留有64個(gè)通用I/O口,可以將其配置為L(zhǎng)VDS的I/O口,這樣可以提高數(shù)據(jù)傳輸能力和抗干擾性能。數(shù)據(jù)傳輸流程如圖3所示,ICS554內(nèi)部FPGA先將24 b的I,Q數(shù)據(jù)流并/串轉(zhuǎn)換。VHDL語(yǔ)言的狀態(tài)機(jī)實(shí)現(xiàn)并/串轉(zhuǎn)換很容易,然后由LVDS發(fā)送模塊將LVTTL信號(hào)轉(zhuǎn)換成LVDS信號(hào)進(jìn)行發(fā)送,接收端FPGA波束形成板首先將接收到的LVDS信號(hào)轉(zhuǎn)換成LVTTL信號(hào),然后進(jìn)行數(shù)據(jù)同步,再經(jīng)過(guò)串/并轉(zhuǎn)換,將串碼恢復(fù)成24 b的I,Q數(shù)據(jù)。由于利用ICS554提供給用戶的通用I/O口配置為L(zhǎng)VDS差分對(duì),差分對(duì)的相位、互耦等都沒(méi)有很好的考慮,而且不能采用專用的平衡電纜連接,因而必須降低傳輸速率,以減小傳輸誤碼率,增強(qiáng)可靠性,同時(shí)考慮配置9位的LVDS口,8位并行傳輸數(shù)據(jù),1位發(fā)送時(shí)鐘信號(hào),LVDS傳輸速率為:

30×2×24/8=180 Mb/s

實(shí)際測(cè)試也表明,180 Mb/s的傳輸速度LVDS差分對(duì)能夠可靠的工作,F(xiàn)PGA波束形成板正確地接收到采集板ICS554的數(shù)據(jù)。

2.2 實(shí)時(shí)波束形成計(jì)算

如前所述,整個(gè)實(shí)時(shí)波束形成分為兩次,首先在采集板ICS554中完成子陣波束形成,然后再到FPGA波束形成板中實(shí)現(xiàn)全陣的波束形成,如何保證整個(gè)計(jì)算的實(shí)時(shí)性是關(guān)鍵。

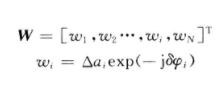

波束的形成,其實(shí)就是對(duì)A/D變換后數(shù)字信號(hào)進(jìn)行幅度和相位加權(quán),波束的特性如波束指向、副瓣電平、主瓣寬度等完全由權(quán)值決定。權(quán)值計(jì)算主要考慮兩方面的因素,首先要對(duì)各通道進(jìn)行幅相校準(zhǔn),克服各通道不一致和互耦的影響,然后實(shí)現(xiàn)空域?yàn)V波,完成希望的波束指向。首先幅相校準(zhǔn),對(duì)于第i單元:

式中:δφi,△ai分別為第i通道與標(biāo)準(zhǔn)通道的相位差和幅度比值。若要實(shí)現(xiàn)空域?yàn)V波則需要在此基礎(chǔ)上增加陣因子對(duì)幅度和相位加權(quán)。

![]()

式中:φi為第i通道相位加權(quán)值;αi為幅度加權(quán)值,可以根據(jù)不同的波束性能要求(主瓣寬度、旁瓣電平、零陷位置)靈活選擇不同的幅度加權(quán)形式,得到不同的αi,權(quán)值矩陣W也會(huì)有所不同。權(quán)值更新計(jì)算由DSP處理板完成。

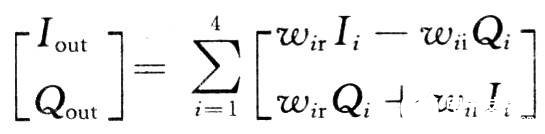

最初的子陣波束形成需實(shí)現(xiàn)四通道單元的波束形成,即對(duì)4路中頻數(shù)字I,Q兩路信號(hào)復(fù)加權(quán)求和:

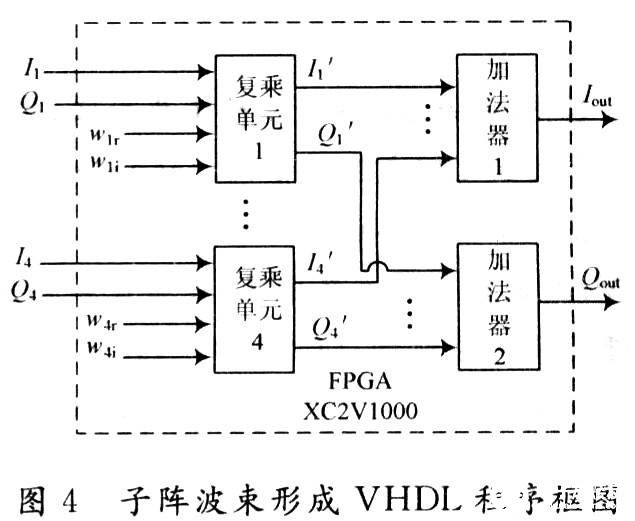

式中:Iout,Qout為4通道波束形成后I,Q兩路輸出結(jié)果;ωir,ωii分別為第i單元權(quán)值的實(shí)部、虛部。由于ICS554采樣頻率比較高,而FPGA片內(nèi)剩余可利用的資源比較多,在這里采用并行復(fù)乘運(yùn)算,運(yùn)用ISE軟件IP核設(shè)計(jì)映射出4個(gè)獨(dú)立的復(fù)乘運(yùn)算單元,片內(nèi)VHDL程序設(shè)計(jì)如圖4所示。

用4塊采集板ICS554獨(dú)立進(jìn)行子陣波束形成,然后將結(jié)果Iout,Qout輸出給FPGA波束形成板進(jìn)行復(fù)求和,最終得到16個(gè)天線單元的全陣合成波束。考慮FPGA運(yùn)算的復(fù)雜性,選用內(nèi)含DSP內(nèi)核的Xilinx公司的XC3SD3400A芯片,該芯片性價(jià)比非常高,內(nèi)含的DSP內(nèi)核XtremeDSP DSP48A運(yùn)算速度可以達(dá)到250 MHz,差分I/O傳輸速率可達(dá)到622 Mb/s。要保證整個(gè)波束形成運(yùn)算的實(shí)時(shí)性,主要從采集板子陣波束形成運(yùn)算、數(shù)據(jù)傳輸、FPGA板全陣波束形成運(yùn)算三個(gè)方面測(cè)試分析。全陣波束形成運(yùn)算主要是在XC3SD3400A內(nèi)做復(fù)數(shù)加法運(yùn)算,加法運(yùn)算最高可以到250 MHz,遠(yuǎn)遠(yuǎn)高于數(shù)字下變頻后數(shù)據(jù)流速度。子陣波束形成運(yùn)算則是在XC2V1000內(nèi)做四通道并行復(fù)乘運(yùn)算和復(fù)加運(yùn)算,片內(nèi)復(fù)乘流水線、復(fù)加運(yùn)算時(shí)鐘頻率可達(dá)420 MHz。實(shí)際上,子陣和全陣波束形成的運(yùn)算能力都是足夠的,整個(gè)系統(tǒng)的主要瓶頸還是數(shù)據(jù)傳輸,數(shù)據(jù)傳輸流量大,數(shù)據(jù)傳輸I/O口位寬達(dá)8位,在數(shù)據(jù)傳輸環(huán)節(jié),將低速多位并行數(shù)據(jù)用倍頻時(shí)鐘轉(zhuǎn)換成250 MHz高速串行數(shù)據(jù);在接收端,使用移位寄存器實(shí)現(xiàn)串/并轉(zhuǎn)換就可以得到低速并行數(shù)據(jù)。仿真和實(shí)際測(cè)試也表明,能夠保證整個(gè)系統(tǒng)波束形成運(yùn)算的實(shí)時(shí)性。

3 結(jié) 語(yǔ)

這里設(shè)計(jì)的高速實(shí)時(shí)波束形成器,改善了原DBF系統(tǒng),不僅可完成測(cè)向工作,同時(shí)實(shí)現(xiàn)了高速數(shù)據(jù)傳輸和全陣的實(shí)時(shí)數(shù)字波束形成。系統(tǒng)是基于采集板ICS554搭建的,ICS554雖然是一款高性能的4通道采集板,但是它成本高,而且只提供PCI接口,沒(méi)有提供其他高性能的數(shù)據(jù)傳輸接口,當(dāng)陣元數(shù)更多時(shí)其可擴(kuò)展性并不強(qiáng)。為了達(dá)到數(shù)據(jù)傳輸能力的要求,采用了多組LVDS差分對(duì)數(shù)據(jù)進(jìn)行傳輸,雖然實(shí)現(xiàn)了要求的速度,但是連接電纜太多,互耦影響大、傳輸距離短。因而,后續(xù)的系統(tǒng)設(shè)計(jì)中,利用FPGA集成速度更快的高速串行差分RocketIO通道、光纖傳輸?shù)燃夹g(shù)來(lái)改善性能,提高系統(tǒng)可擴(kuò)展性。

責(zé)任編輯:gt

-

dsp

+關(guān)注

關(guān)注

553文章

7987瀏覽量

348745 -

FPGA

+關(guān)注

關(guān)注

1629文章

21729瀏覽量

602993 -

接收機(jī)

+關(guān)注

關(guān)注

8文章

1180瀏覽量

53455

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

數(shù)字波束形成相控陣中射頻電子的物理尺寸分配

怎么設(shè)計(jì)基于FPGA多波束成像的聲納系統(tǒng)?

基于FPGA器件和LVDS技術(shù)設(shè)計(jì)的高速實(shí)時(shí)波束形成器

請(qǐng)問(wèn)怎么采用FPGA和集成器件來(lái)實(shí)現(xiàn)IJF編碼?

如何去設(shè)計(jì)高速實(shí)時(shí)波束形成器系統(tǒng)?

相控陣?yán)走_(dá)數(shù)字波束形成的實(shí)現(xiàn)

基于LVDS技術(shù)的實(shí)時(shí)圖像測(cè)試裝置的設(shè)計(jì)

一種高速實(shí)時(shí)數(shù)字波束形成器的設(shè)計(jì)

基于FPGA的數(shù)字波束形成技術(shù)的工程實(shí)現(xiàn)

一種用時(shí)變FIR濾波器實(shí)現(xiàn)寬帶恒定束寬波束形成器的方法

(Xilinx)FPGA中LVDS差分高速傳輸?shù)?b class='flag-5'>實(shí)現(xiàn)

成像聲納中多波束形成的FPGA工程實(shí)現(xiàn)

專用集成電路實(shí)現(xiàn)寬帶射頻相控陣波束形成

基于FPGA的B超全數(shù)字波束形成技術(shù)

采用FPGA器件和LVDS技術(shù)實(shí)現(xiàn)高速實(shí)時(shí)波束形成器的設(shè)計(jì)

采用FPGA器件和LVDS技術(shù)實(shí)現(xiàn)高速實(shí)時(shí)波束形成器的設(shè)計(jì)

評(píng)論