從1998年三星生產出最早的商用DDR SDRAM芯片到現在差不多已經過去20多年了,DRAM市場一直在發展,從DDR到DDR2,DDR3,DDR4,然后是即將進入市場的DDR5。今天我們來聊一下DDR的JEDEC規范。

什么是JEDEC?

JEDEC全稱:JointElectron Device Engineering Council JEDEC是一個全球性的固態技術協會組織,理論上不隸屬于任何一個國家或者政府實體,為半導體產業制定標準。包括很多方面,今天我們只關注DDR的相關規范。 DDR的開發是從1996年開始,對應JEDEC的規范 JESD79于2000年發布。JEDEC規范由兩部分組成,一個是針對memory chip,另外一個是memory module。當然,隨著RDIMM,LRDIMM的興起,JEDEC相對應的制定出了RCD和Data Buffer的規范。我們今天主要聊JEDEC的SDRAM規范,也就是JESD79系列, 這里大家需要注意的是這個規范是針對DRAM芯片的,而不是內存條。有興趣的同學可以去JEDEC網站上去下載相對應的規范,規范最后面的字母代表版本,比如JESD79-4C的C就代表目前針對DDR4 SDRAM的規范的版本是C。而JESD79后面的數字就代表了是DDR第幾代。目前JEDEC網站上針對DDR5 SDRAM的規范還在制定當中,如果繼續按照這個命名規律的話,應該是JESD79-5。

| Name | Doc |

| Double Date Rate (DDR) SDRAM | JESD79F |

| DDR2 SDRAM Specification | JESD79-2F |

| DDR3 SDRAM Standard | JESD79-3F |

| DDR4 SDRAM | JESD79-4C |

| DDR5: JEDEC DDR5 standard in currently in development | NA |

JEDEC的網站:www.jedec.org

下面這個表列舉了JEDEC 規范從DDR到DDR5的主要變化,我們可以看到,為了配合整體行業對于性能,容量和省電的不斷追求,規范的工作電壓越來越低,芯片容量越來越大, IO的速率也越來越高。雖然目前DDR5的JEDEC規范還沒有正式出臺,但是我們可以從這個趨勢以及現有網上的資料得到相同的結論。

|

Feature /Option |

DDR | DDR2 | DDR3 | DDR4 | DDR5* |

|

Voltage (VDDQ) |

2.5V | 1.8V | 1.5V | 1.2V | 1.1V |

|

Device Width |

x4, x8, x16 |

x4,x8, x16 |

x4, x8, x16 |

x4,x8, x16 |

x4, x8, x16 |

|

Die Density |

64Mb~ 1Gb |

128Mb~ 4Gb |

512Mb~ 8Gb |

2Gb~ 16Gb |

8Gb~ 64Gb |

|

Data Rates |

200~ 400MT/s |

400~ 800MT/s |

800~ 1600MT/s |

1600~ 3200MT/s |

3200~ 6400MT/s |

| Prefetch | 2n | 4n | 8n | 8n | 16n |

| Bank | 4 | up to 8 | 8 |

4banks pergroup |

2 or 4 banks per group |

|

Bank Group |

NA | NA | NA |

4 for x4/X8; 2 for x16; |

8 for x4/x8; 4 forx16; |

|

Burst Length |

2, 4 or 8 | 4 or 8 | 8 | 8 | 16 |

表 (一)

聲明:目前DDR5的JEDEC標準還沒有正式發布,因此這里所有的DDR5相關的數據來自于網上公開的數據,后續以JEDEC發布為準。同時,從DDR5開始,每根內存上有兩個獨立的通道。

從上面的表里面我們還可以看到,除了電壓,容量和IO的速率變化之外,還列出了Bank,Bank Group,Prefetch和Burst Length的演進,bank數越來越多,到DDR4出現bank group,prefetch也從2n增加到4n,8n。那么這些變化之間有什么聯系嗎?DDR5又會有什么樣的變化?要了解這些,我們需要回顧一下SDRAM的基本讀寫操作,以及DRAM的核心頻率和IO頻率。

Prefetch和burst length

雖然我們說現在DDR4的最大速率是3200MT/s, 但是這是指的DDR4的IO頻率,即DDR4和memroy controller之間的接口數據傳輸速率。那么DRAM是怎么實現用比較低的核心傳輸頻率來滿足日益高漲的高速IO傳輸速率的需求呢?這就是靠prefetch來實現的。

| Prefetch |

Core Frequency |

IO CLK Frequency |

IO Data Rate |

|

| SDRAM | NA |

100-150 MHz |

100-150 MHz |

100-150 Mbps |

| DDR | 2 |

100-200 MHz |

100-200 MHz |

200-400 Mbps |

| DDR2 | 4 |

100-200 MHz |

200-400 MHz |

400-800 Mbps |

| DDR3 | 8 |

100-266 MHz |

400-1066 MHz |

800-2133 Mbps |

| DDR4 | 8 |

100-266 MHz |

800-1600 MHz |

1600-3200 Mbps |

| DDR5* | 16 |

100-266 MHz |

1600-3200 MHz |

3200-6400 Mbps |

表 (二)

從DDR開始到DDR3很好理解,Prefetch相當于DRAM core同時修了多條高速公路連到外面的IO口,來解決IO速率比內部核心速率快的問題,IO數據速率跟核心頻率的倍數關系就是prefetch。那么這么一路增加prefetch,到了DDR4為什么不繼續增加prefetch了呢?因為prefetch的增加對應的就是burst length的有可能相應增加。怎么理解prefetch和burst length之間的關系呢?Prefetch跟DRAM核心頻率和IO頻率之間的比例相關,而burst length的長度跟CPU的cache line大小有關。Burst length的長度有可能大于或者等于prefetch。但是如果prefetch的長度大于burst length的長度,就有可能造成數據浪費,因為CPU一次用不了那么多。所以從DDR3到DDR4,如果在保持DDR4內存data lane還是64的前提下,繼續采用增加prefetch的方式來提高IO速率的話,一次prefetch取到的數據就會大于一個cache line的大小 (512bits),對于目前的CPU系統,反而會帶來性能問題。那么DDR4是怎么解決的呢?

Bank Group

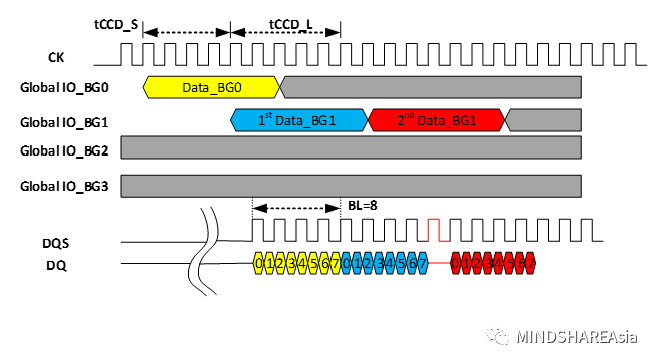

我們注意到在表一里面,到了DDR4出現了Bank Group,這就是DDR4在不改變prefetch的情況下,能繼續提升IO速率的秘密武器。DDR4利用Bank group的interleave,實現IO速率在DDR3基礎上進一步提升。

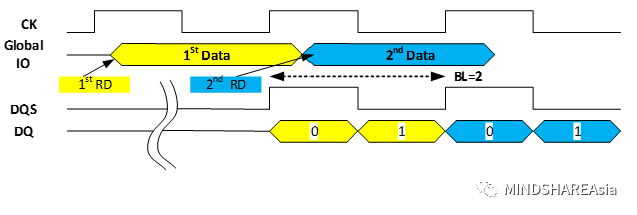

圖一:DDR1

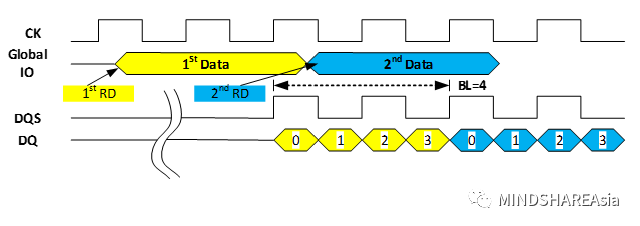

圖二:DDR2

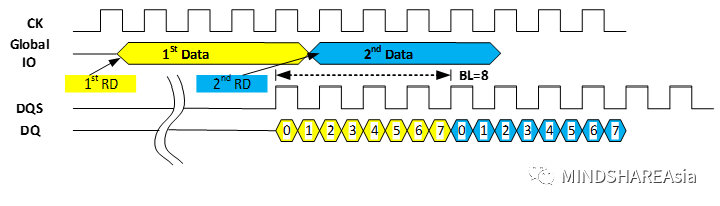

圖三:DDR3

圖四:DDR4

從上面的圖四中可以看到,每個bank group有自己的global IO,這樣就可以利用bank group的interleave來進一步解決內部速度和外部速度不匹配的問題。相當于在DDR3的基礎上繼續修了并行的相對比較慢的高速公路搭到外面的超高速單行道。 到了DDR5,我們還能繼續利用Bank Group的interleave來實現提升IO速率的目的嗎?如果繼續這樣做的話,對于速率提升的效果就很有限,所以到了DDR5還是走到了增加prefetch的方向。DDR5的prefetch是16,那么怎么解決我們前面提到的cache line大小的問題呢?DDR5采取的方式是減少DIMM data lane的數量,從64個data lane降低到32個data lane,從而繼續保持64 Byte的cache line大小。 從以上JEDEC DDR到DDR4的發展歷史,我們可以看到,DRAM的演進就是在為CPU系統架構服務的基礎上,圍繞著成本、降低電源消耗、加大容量、提高IO速率來不斷演進。基于DRAM操作的原理,最大化的提高DRAM的使用率。因此,我們也可以看到DDR5提供了更多的bank數量和更加細化的refresh粒度等等,這些都是為了物盡其用,提高系統性能。我們在后續的文章中,會繼續介紹DRAM的基本性能以及DDR5的新功能。

最后留給大家的問題:對于DDR4,bank group與group之間是tCCD_L還是tCCD_S?為什么?

-

半導體

+關注

關注

334文章

27290瀏覽量

218090 -

DDR

+關注

關注

11文章

712瀏覽量

65318 -

內存

+關注

關注

8文章

3019瀏覽量

74005

原文標題:來啦!DDR內存的前世、今生和未來!

文章出處:【微信號:SSDFans,微信公眾號:SSDFans】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

DDR內存的工作原理 DDR內存的常見故障及解決辦法

DDR內存與SDRAM的區別 DDR4內存與DDR3內存哪個好

DDR5內存的工作原理詳解 DDR5和DDR4的主要區別

深入了解Java泛型——從前世今生到PECS原則

DDR內存與數據傳輸速度的關系

DDR內存故障排查方法

DDR內存的工作原理與結構

如何檢測DDR內存性能

DDR內存超頻技巧與注意事項

如何選擇DDR內存條 DDR3與DDR4內存區別

一文讀懂DDR內存基礎知識

DDR內存的前世、今生和未來!

DDR內存的前世、今生和未來!

評論