(轉(zhuǎn)載自嗶哩嗶哩專欄翻滾吧工程師 在此特別鳴謝!)PCB上存在類似的情況,其中不同導(dǎo)線上的多個信號可能相互干擾。當(dāng)信號傳輸?shù)狡叫袑?dǎo)線時產(chǎn)生相應(yīng)的電磁能時,就被稱為耦合。導(dǎo)體之間的耦合可以是好的也可以是壞的,可以表示為0和1(或0%和100%)之間的比率。例如,可以使用捆綁導(dǎo)體或雙絞線電纜來實現(xiàn)支持良好信號傳輸?shù)慕跬昝赖鸟詈媳取2涣捡詈匣虼當(dāng)_通常是指由于另一導(dǎo)體對相鄰導(dǎo)體的信號產(chǎn)生扭曲或降低信號質(zhì)量這類不良信號干擾。

讓我們來看看串?dāng)_的原因,然后看看Altium Designer如何幫助您最大限度地減少串?dāng)_對電路板的影響。

什么原因?qū)е麓當(dāng)_?

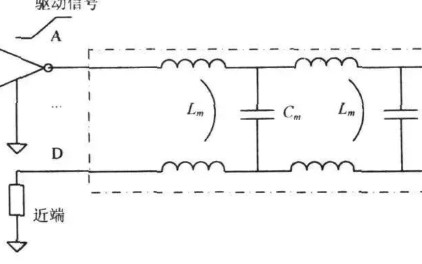

串?dāng)_是PCB設(shè)計人員必須應(yīng)對的信號完整性問題之一。通常,當(dāng)兩個不同的信號傳播路徑彼此太靠近并且其各自的EM電磁場延伸超出分隔導(dǎo)體的空間時,發(fā)生串?dāng)_。串?dāng)_可能是數(shù)據(jù)進(jìn)行高速傳輸中最重要的一個影響因素了。

它是一個信號對另外一個信號耦合所產(chǎn)生的一種不受歡迎的能量。根據(jù)麥克斯韋定律,只要有電流的存在,就會有磁場存在,磁場之間的干擾就是串?dāng)_的來源。這個感應(yīng)信號可能會導(dǎo)致數(shù)據(jù)傳輸?shù)膩G失和傳輸錯誤。所以串?dāng)_對于綜合布線來說,無疑是個最厲害的天敵。由于這種干擾是不希望的,因此可將其歸類為噪聲并且會導(dǎo)致信號失真或降低信號純度。

1)元件問題

隨著電子產(chǎn)品變得越來越小,它們所包含的PCB也必須更小。然而,這些尺寸減小通常與對更大功能的需求相匹配。為了實現(xiàn)這些可能看起來彼此矛盾的目標(biāo),元件封裝變得更小但具有更大量的網(wǎng)絡(luò)連接或引腳數(shù)。顯然,這會導(dǎo)致引腳間的間距變得更緊,從而促使電容耦合。引腳之間的耦合可能發(fā)生在沿著電路板表面從元件延伸的連接或從元件下方延伸,以便信號流過通孔。

2)布線問題

隨著布線在電路板上占據(jù)更多空間,可能會出現(xiàn)更多可能發(fā)生串?dāng)_的區(qū)域。這包括在焊盤或布線路徑的起點和終點,以及同一層以及層與層之間的相鄰路徑。焊盤上的串?dāng)_類似于元件引腳之間的串?dāng)_。在沿著導(dǎo)線路徑上,干擾通常是由于相似長度的信號路徑在相同角度處的分離不充分或具有銳角彎曲的單根導(dǎo)線。當(dāng)疊層中的信號層未被電介質(zhì)充分隔離時,也可能在不同層上的布線之間發(fā)生串?dāng)_。

Altium Designer 中的串?dāng)_消除技術(shù)

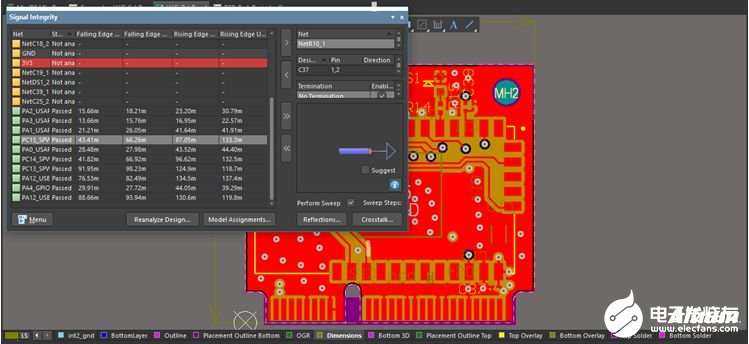

看起來串?dāng)_對于PCB設(shè)計的良好信號完整性來說是一個不可逾越的障礙,特別是對于小而密集的復(fù)雜電路板。當(dāng)然,這是一個重大的設(shè)計挑戰(zhàn),但有一些技術(shù)可以用來減少串?dāng)_對電路工作的影響。為了充分利用這些技術(shù),我們首先需要能夠分析我們的電路板信號,以確定是否需要消除串?dāng)_。Altium Designer提供了執(zhí)行信號完整性分析的工具,如下圖所示。

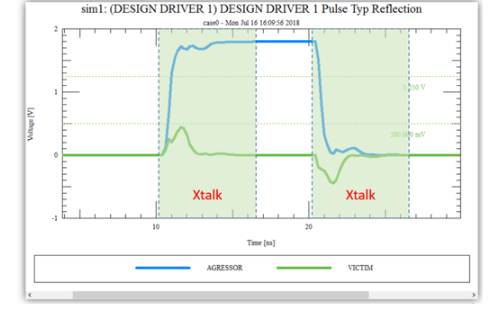

信號完整性分析案例

Altium中的信號完整性分析包括檢查信號上升時間,下降時間,提供終端方案和進(jìn)行串?dāng)_分析的能力。您還可以定義模型并設(shè)置規(guī)則和約束以及信號完整性分析相關(guān)的其它設(shè)置。一旦確認(rèn)了串?dāng)_問題,就可以根據(jù)需要修改相同層或相鄰層的布線路徑,如下所述。

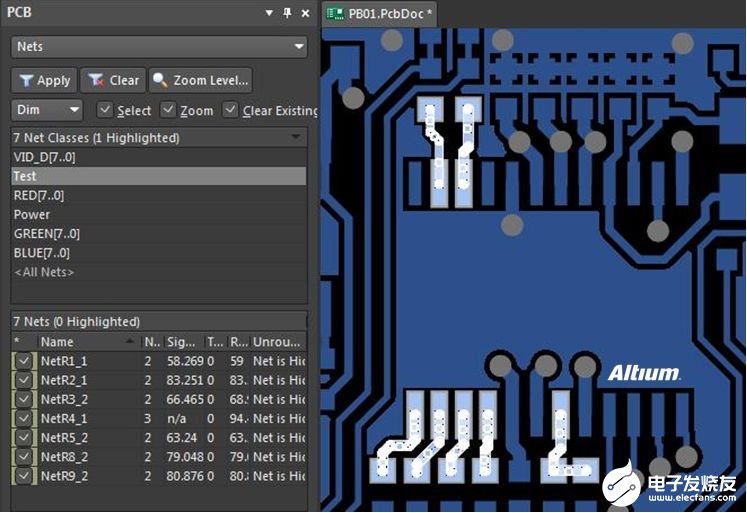

1)確保布線之間有足夠的距離

在大多數(shù)情況下,串?dāng)_的原因是有耦合關(guān)系的導(dǎo)體之間的間距不足。因此,減少串?dāng)_的最佳解決方案或技術(shù)是增加兩個不同網(wǎng)絡(luò)布線之間的間距。在Altium Designer中,通過使用高亮顯示可以非常輕松地完成此操作,這可以讓您一次移動單個元素和路徑或類。在更改布線時,請務(wù)必遵循良好的PCB布局布線技巧。

使用網(wǎng)絡(luò)類來設(shè)置布線間距

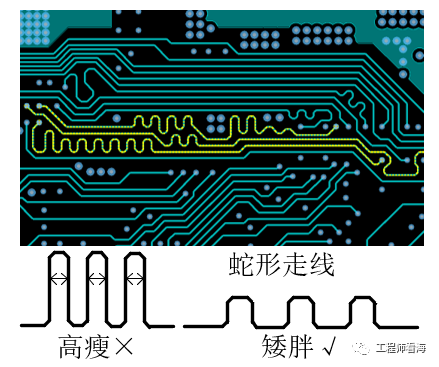

2)最小化并行走線的長度

有時,比如對于差分對,需要很好地匹配信號路徑。在這些情況下,確保兩個信號的銅重量,走線寬度和長度相同是重要設(shè)計目標(biāo)。相反,當(dāng)并行走線用于不同信號時,其重要設(shè)計目標(biāo)則是最小化它們的相互作用或耦合。如果不能選擇足夠的間距,則可以將其中一條走線拉長,使得兩條走線的并行長度盡量縮短;或者使一條走線垂直于另一條走線以減少串?dāng)_。

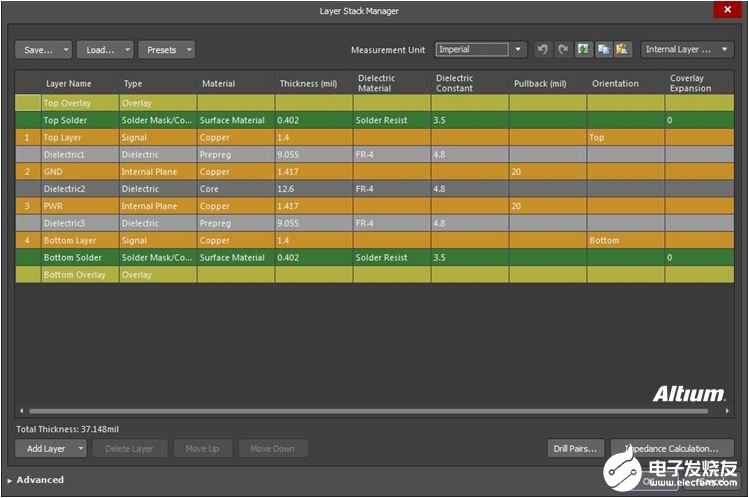

3)使用地平面隔離信號層

雖然相對于在同一層上產(chǎn)生的串?dāng)_來說,疊層之間的串?dāng)_并不常見,但確實會發(fā)生PCB疊層中相鄰層之間的干擾。這種耦合的主要原因是由于層之間的絕緣不足而導(dǎo)致信號沒有充分隔離。相鄰層之間的絕緣部分是在其上蝕刻銅層的介電材料。在Altium Designer中,使用“層堆棧管理器”對話框設(shè)計堆棧是一項簡單的任務(wù)。如下圖所示,您可以在其中選擇材料類型,設(shè)置板厚度并定義介電常數(shù)。

使用層堆棧管理器定義PCB堆棧

作為使用不同材料進(jìn)行疊層的替代方案,可以在信號層之間插入接地平面。這有助于提高隔離度,有助于為您的設(shè)計提供更短的接地路徑。

串?dāng)_是一種信號完整性問題,幾乎可以在兩個導(dǎo)體彼此靠近的任何位置影響PCB功能。最好的串?dāng)_消除技術(shù)是插入空間或障礙以減少耦合的技術(shù)。在應(yīng)用任何這些之前,必須首先識別串?dāng)_。Altium Designer提供了一個多功能信號分析工具,可用于診斷電路板的信號并確定要應(yīng)用的最佳消除技術(shù)。

-

PCB設(shè)計

+關(guān)注

關(guān)注

396文章

4759瀏覽量

88840 -

信號完整性

+關(guān)注

關(guān)注

68文章

1429瀏覽量

96313 -

PCB打樣

+關(guān)注

關(guān)注

17文章

2971瀏覽量

22293 -

Altium Designer

+關(guān)注

關(guān)注

49文章

402瀏覽量

45383 -

可制造性設(shè)計

+關(guān)注

關(guān)注

10文章

2065瀏覽量

15958 -

麥克斯韋

+關(guān)注

關(guān)注

0文章

19瀏覽量

5808 -

華秋DFM

+關(guān)注

關(guān)注

20文章

3498瀏覽量

5184 -

PCB線路板打樣

+關(guān)注

關(guān)注

9文章

619瀏覽量

6029 -

可制造性設(shè)計分析

+關(guān)注

關(guān)注

4文章

866瀏覽量

5926

發(fā)布評論請先 登錄

信號串擾消除方案之PCB設(shè)計IDA Crosstalk分析功能

評論