重點

●高質(zhì)量DesignWare DDR PHY IP核為NVIDIA提供無與倫比的性能、延遲和電源效率

●DDR PHY支持DDR5/4的每個通道多個DIMM,滿足NVIDIA的網(wǎng)絡數(shù)據(jù)速率和內(nèi)存容量要求

●基于固件的現(xiàn)場可升級訓練可提高通道的穩(wěn)定性和可靠性,并且有助于算法更新,從而降低采用新內(nèi)存協(xié)議的風險

新思科技(Synopsys)近日宣布,NVIDIA的網(wǎng)絡業(yè)務部門Mellanox將采用經(jīng)驗證的DesignWare DDR5/4 PHY IP核,以滿足其針對高性能計算和人工智能應用的InfiniBand網(wǎng)絡芯片不斷變化的內(nèi)存需求。NVIDIA正在高性能和云計算領(lǐng)域增加投入,憑借高達80位數(shù)據(jù)路徑和對每個通道多個DIMM的支持,DesignWare DDR5/4 IP核可滿足NVIDIA基本數(shù)據(jù)速率和內(nèi)存容量的要求。作為新思科技廣泛的內(nèi)存接口IP核組合的一部分,DesignWare DDR5/4 PHY IP核由控制器、PHY和各種工藝的驗證IP核組成,支持所有必備功能,有助于Mellanox將這些IP核整合到其ASIC和芯片中,降低相關(guān)風險。

DesignWare DDR5/4 PHY IP核提供基于固件的訓練,無需更改硬件即可進行現(xiàn)場升級,從而幫助客戶降低采用新協(xié)議的風險。基于固件的訓練也有助于使用復雜的訓練模式,在系統(tǒng)層面上支持最高裕度和通道可靠性。就功率效率而言,DDR5/4 PHY IP核提供多個低功率狀態(tài)、具有較短的退出延遲、多個預訓練狀態(tài)和可實現(xiàn)動態(tài)頻率調(diào)整功能。

“用于數(shù)據(jù)密集型網(wǎng)絡和人工智能應用的高性能ASIC和芯片,需要可有效降低性能瓶頸的高帶寬片外存儲器技術(shù)。DesignWare DDR5/4 PHY IP核以最高數(shù)據(jù)速率運行,具有基于固件的訓練等差異化功能,使NVIDIA等公司能夠以更低的風險在其設(shè)計中部署最新功能。”

——John Koeter

解決方案事業(yè)部營銷高級副總裁 新思科技

“長期以來,我們一直將新思科技的高質(zhì)量IP核集成到我們的芯片中,因此我們選擇將DesignWare IP核整合到我們具有網(wǎng)絡計算功能的最新InfiniBand解決方案中。新思科技的DDR PHY IP核是市面上的最佳解決方案,既能滿足我們嚴格的內(nèi)存需求,也能為我們提供實現(xiàn)差異化產(chǎn)品所需的質(zhì)量、容量和性能。”

——Shlomit Weiss

Mellanox業(yè)務工程部高級副總裁 NVIDIA

-

NVIDIA

+關(guān)注

關(guān)注

14文章

4978瀏覽量

102994 -

人工智能

+關(guān)注

關(guān)注

1791文章

47188瀏覽量

238268 -

網(wǎng)絡芯片

+關(guān)注

關(guān)注

0文章

30瀏覽量

12092

原文標題:NVIDIA采用DesignWare DDR IP核,支持高性能云計算網(wǎng)絡芯片

文章出處:【微信號:Synopsys_CN,微信公眾號:新思科技】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

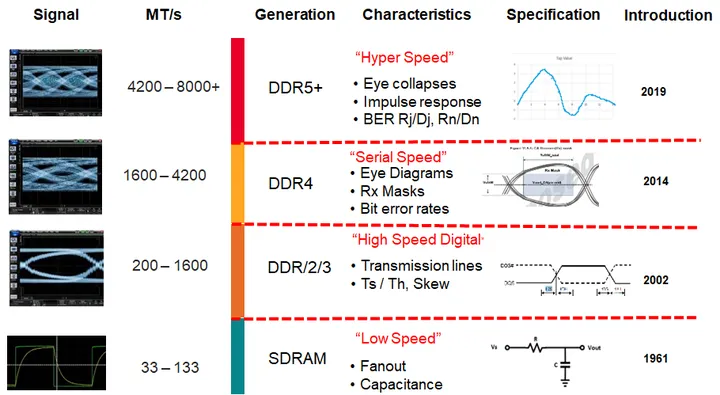

DDR3、DDR4、DDR5的性能對比

DDR5內(nèi)存與DDR4內(nèi)存性能差異

DDR5內(nèi)存的工作原理詳解 DDR5和DDR4的主要區(qū)別

Introspect DDR5/LPDDR5總線協(xié)議分析儀

DDR5內(nèi)存條上的時鐘走線

0706線下活動 I DDR4/DDR5內(nèi)存技術(shù)高速信號專題設(shè)計技術(shù)交流活動

談談DDR5技術(shù)規(guī)格的那些事

DDR5測試技術(shù)更新漫談

DDR5內(nèi)存接口芯片組如何利用DDR5 for DIMM的優(yōu)勢?

瀾起科技:DDR5第三子代RCD芯片將隨新一代CPU平臺規(guī)模出貨

DDR6和DDR5內(nèi)存的區(qū)別有多大?怎么選擇更好?

芯耀輝DDR PHY訓練技術(shù)簡介

NVIDIA的Mellanox將采用經(jīng)驗證的DesignWare DDR5/4 PHY IP核

NVIDIA的Mellanox將采用經(jīng)驗證的DesignWare DDR5/4 PHY IP核

評論