摘要:為實現894.6 nm低閾值、高穩定性、單模激光輸出,設計了具有不同臺面刻蝕結構的垂直腔面發射激光器(VCSEL)器件,研究了臺面直徑和氧化孔結構對器件激射性能的影響。研究結果表明:VCSEL臺面直徑越大,閾值電流越大;氧化孔徑越偏向圓形,邊模抑制比越高。制備了氧化孔為圓形、直徑為4.4 μm的VCSEL器件,該器件在70~90 ℃工作溫度及0.6 mA驅動電流下實現了894.6 nm單模激光輸出,邊模抑制比高于35 dB。

1引言

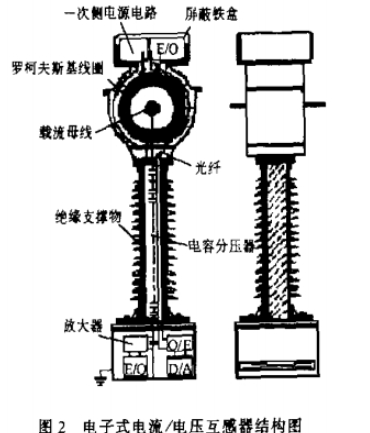

垂直腔面發射激光器(VCSEL)具有體積小、光斑為圓形、響應頻帶寬、易于實現二維陣列集成等優越的性能,在光纖通信系統、陀螺儀、原子鐘等領域具有重要應用。現階段,由于激光器材料質量及器件制備工藝的限制,VCSEL器件實現低閾值電流、波長穩定輸出較為困難,且VCSEL器件的多模現象較為嚴重。應用于芯片原子鐘的VCSEL器件,需要實現高溫環境下低閾值、單模激光的穩定輸出減小臺面可以達到降低閾值電流的目的,利用水汽氧化可以提高VCSEL的邊模抑制比。隨著水汽氧化工藝在VCSEL器件制備中的應用,VCSEL的性能得到了很大改善。

氧化限制層可以起到光電限制的作用,使VCSEL器件實現低閾值的單模激光輸出。為提高VCSEL的邊模抑制比,研究人員研究了氧化限制層對VCSEL激射性能的影響:Geib等以及Ku等對影響VCSEL的氧化因素進行了分析,得到了氧化深度與時間、溫度之間的關系;2002年,Hawkins等分析了VCSEL氧化孔的大小對器件可靠性的影響,得出了具有較大氧化孔的器件具有較高可靠性的結論;2006年,Chang等利用多個氧化層來減小VCSEL寄生效應的方法,通過將多個氧化層融合到器件中,實現了效率和調制速率高的VCSEL器件;2008年,Almuneau等對VCSEL的氧化深度進行研究,實現了對氧化深度的實時觀測;2012年,劉迪等對不同氧化孔直徑的單管器件的熱特性進行研究后發現,氧化孔直徑越小,器件的熱阻越大,可通過加大氧化孔直徑來降低熱阻;2017年,馮源等采用CRosslight軟件對VCSEL的反射譜和增益譜進行模擬,并對器件結構進行優化,得到了室溫下光譜中心波長在850 nm左右的VCSEL器件;2017年,Marigo-Lombart等對制備低閾值、高邊模抑制比VCSEL器件的方法進行研究,找到了工藝步驟簡單、器件工作效率較高的制備方法。

為實現高邊模抑制比、低閾值的VCSEL器件,本文設計了補償型和圓形臺面刻蝕結構的VCSEL器件,利用水汽氧化工藝制備出氧化孔形狀及大小不同的一系列VCSEL器件;然后對器件的閾值電流、溫漂、邊模抑制比等進行測試分析;此外,研究了VCSEL氧化孔形狀及大小對器件邊模抑制比、閾值電流的影響,根據研究結果制備出具有補償型臺面結構的VCSEL器件,該器件在0.6 mA驅動電流及70~90 ℃工作溫度下,實現了邊模抑制比高于35 dB的894.6 nm激光輸出。

2實驗及理論分析

2.1 VCSEL器件的理論分析及結構設計

面發射激光器的閾值電流Ith的表達式為

式中:e為電子電荷;Beff為等價復合系數;Va為有源區的體積;Nth為滿足振蕩條件時產生光增益所必須的有源區的電子密度;ηi為注入效率;ηspon為自發輻射效率。

圓形臺面結構通過水汽氧化工藝可以得到橢圓形的氧化孔形狀,這是由于[0`11]晶向的鍵能較高,具有較低的表面反應速率,使得[0`11]晶向的氧化速率小于[011]晶向的氧化速率。橢圓形氧化孔在長和寬方向上的折射率可分別表示為

式中:a為橢圓的長軸;b為短軸;n0為氧化層的折射率;g為與溫度相關的擬合參數;δn為折射率梯度;x和y分別為氧化層中折射率為n時測試點的橫縱坐標。橢圓形氧化孔引起了不均勻的折射率分布,故波長差Δλ與不同方向上折射率差Δn之間的關系可以表示為

式中:λ0為中心波長。從(4)式中可以看出,當兩個方向的折射率差Δn不為0時,必然會產生一個相應的波長差。可見,波長差Δλ的大小受氧化孔形狀的影響。

根據VCSEL理論進行器件的結構設計,采用金屬有機化合物化學氣相沉淀(MOCVD)技術制備VCSEL外延片,然后基于外延片制備VCSEL器件,并對VCSEL器件的激射特性進行測試分析。所設計的VCSEL器件結構如圖1所示,其中:N型布拉格反射鏡(DBR)由Al0.9Ga0.1As / Al0.12Ga0.88As緩變膜層組成;有源區由光學厚度為λ0 / 2的兩對InyGa(1-y)As / AlxGa(1-x)As量子阱以及緩變組分的AlxGa(1-x)As間隔層組成;氧化層Al0.98Ga0.02As的厚度為30 nm,利用側向氧化產生Al2O3層,形成絕緣性良好的氧化限制層;氧化層上方是由Al0.9Ga0.1As / Al0.12Ga0.88As緩變膜層構成的P型DBR,每對DBR的光學厚度均為λ0 / 2;N與P分別表示此器件結構的背面與正面。

圖1 VCSEL示意圖

2.2實驗

氧化限制型VCSEL器件的制備過程如下:采用電感耦合等離子刻蝕設備(ICP 180)對外延生長制備得到的VCSEL外延片進行臺面刻蝕,刻蝕深度為4.4 μm(設計了補償型臺面刻蝕結構和圓形臺面刻蝕結構兩種器件);刻蝕完成后對其進行水汽氧化,首先打開N2管道和水浴蒸汽管道,將管式氧化爐升溫至400 ℃,N2流量為7 L/min,水浴蒸汽管道中的N2流量為0.3 L/min,水浴溫度為75 ℃,溫度穩定后,保持40 min,隨后將Wafer放入氧化爐中進行水汽氧化(水汽氧化完成后將樣品取出冷卻至室溫,用光學顯微鏡對氧化孔的形狀及大小進行觀察);然后采用等離子體增強化學氣相沉積(PECVD)技術對氧化后的Wafer進行鈍化,并用聚酰亞胺(PI)膠填充間隔槽,獲得平坦的臺面結構;接著采用磁控濺射工藝制備器件的P面電極,將N面減薄拋光至芯片厚度為150 μm,并制備N面金屬電極;最后進行退火處理,使N面電極和P面電極形成良好的歐姆接觸,獲得VCSEL芯片,將VCSEL芯片進行封裝即可獲得VCSEL器件。

利用Avaspec ULS2048L-2-USB2光譜儀(步長為0.25 nm)及測試軟件AvaS0ft8進行光譜測試,測試過程中采用相干布居囚禁(CPT)物理測試系統(溫度精確度為0.01 ℃,電流精確度為0.001 mA)控制溫度和電流,得到穩定溫度下VCSEL器件的閾值電流及激射譜。

3結果與討論

采用水汽氧化工藝制備得到的兩種VCSEL臺面結構如圖2所示,由圖2(f)可知,兩種臺面分別為圓形和補償型刻蝕結構。圖2(a)~(c)所示器件A、B、C的臺面直徑分別為27,23,21 μm,臺面刻蝕結構為補償型,氧化孔為偏圓形,氧化孔的長短軸值較為接近(可近似看作是圓形);器件A、B的氧化孔直徑分別為4.8 μm、4.4 μm,器件C的氧化孔為偏圓形,長軸約為3.8 μm,短軸約為3.5 μm,橢率較小(可近似看作是圓形)。圖2(d)所示器件D的臺面直徑為27 μm,臺面刻蝕結構為圓形,氧化孔為橢圓形,長軸約為6.1 μm,短軸約為5.5 μm。圖2(e)所示器件E的臺面直徑為23 μm,臺面刻蝕結構為圓形,氧化孔為橢圓形,長軸約為5.7 μm,短軸約為4.1 μm。

通過對比分析測試結果可知,在相同的氧化條件下,臺面刻蝕結構不同時,氧化孔形狀會有所差異。如圖2(d)、(e)所示,圓形氧化臺面經水汽氧化后,氧化孔為非圓形,這表明氧化反應不是完全各向同性的,即反應速率沿特定的晶向是不同的。如圖2(a)~(c)所示,將圓形與矩形相結合形成的補償型臺面結構可以對具有較快反應速率的[011]晶向進行補償,調控水汽氧化過程中[011]晶向與[0`11]晶向的氧化深度差值,彌補氧化過程中因不同晶向的反應速率不同而引起的氧化孔形狀不規則的問題,并最終得到圓形氧化孔。如圖2所示,補償型刻蝕臺面的氧化效果較好,氧化孔形狀接近圓形。對不同直徑臺面的氧化效果進行對比可知,臺面直徑越大,氧化孔越趨于圓形,這是因為隨著氧化孔徑增大,氧化孔氧化速率的各向異性程度減弱,故而趨于圓形。因此,可通過采用補償型臺面刻蝕結構或增大臺面直徑的方式來獲得圓形氧化孔。

圖2 器件臺面結構氧化后的俯視顯微圖與臺面結構類型示意圖。(a)直徑為27 μm的補償型臺面結構,氧化孔為圓形;(b)直徑為23 μm的補償型臺面結構,氧化孔為圓形;(c)直徑為21 μm的補償型臺面結構,氧化孔為圓形;(d)直徑為27 μm的圓形臺面結構,氧化孔為橢圓形;(e)直徑為23 μm的圓形臺面結構,氧化孔為橢圓形;(f)補償型與圓形臺面結構示意圖

3.1 VCSEL臺面直徑和氧化孔結構對器件閾值電流及溫漂的影響

對器件進行變溫閾值電流測試,研究VCSEL氧化孔形狀及大小對器件閾值電流溫漂的影響,具有不同氧化孔形狀和不同臺面結構的VCSEL器件的閾值電流隨溫度變化的測試結果如圖3所示。可見,器件的閾值電流均隨著溫度的升高而增加。在圖3(a)中可進一步觀察到:當臺面直徑相同時,圓形和橢圓形氧化孔器件在相同溫度下的閾值電流相差較小,表明氧化孔形狀不是影響器件閾值電流的最主要因素;臺面直徑大的器件,相應的閾值電流較大。圖3(b)為臺面直徑不同但氧化孔均為圓形的VCSEL器件的閾值電流對比結果,從對比結果可知,相同溫度下,臺面直徑越大,器件的閾值電流越大,80 ℃時器件A、B、C的閾值電流分別為1.1,0.48,0.28 mA,這表明臺面直徑是影響VCSEL器件閾值電流的主要因素。由(1)式可知,通過減小半導體激光器有源區的體積可以降低器件的閾值電流,因此,減小VCSEL器件的臺面直徑是獲得低閾值電流器件的有效途徑。

圖3 不同VCSEL器件的變溫閾值電流曲線。(a)不同氧化孔形狀;(b)不同臺面直徑

圖4所示為器件B在不同溫度下的激射光譜測試結果,25 ℃時器件的激射峰位為891.5 nm,30 ℃時激射峰位為891.8 nm,70℃時激射峰位為894.2 nm,75 ℃時激射峰位為894.6 nm,器件的激射峰位隨溫度升高呈線性關系,波長的溫度漂移系數為0.062 nm/℃。VCSEL器件的高溫工作性能是由增益—腔模特性決定的,光譜發生紅移的根本原因是其溫度升高導致了增益的變化,腔模增益譜、量子阱增益光譜均發生了紅移。量子阱的增益峰并不能決定VCSEL器件的激射波長,VCSEL的激射波長是由腔模決定的,隨著溫度升高,器件有源區及DBR光學厚度均會增加,因而其對應的光學波長會增大。

圖4 器件B的峰值波長隨溫度的變化

3.2 VCSEL臺面直徑和氧化孔結構對器件邊模抑制比的影響

VCSEL的諧振腔非常短,其縱模間距非常大,所以多模輸出主要是多橫模激射引起的,氧化孔的形狀及大小對VCSEL的近場模式特性有很大影響,會使高階橫模近場模式分布不同,從而改變激光器的激射特性,這一現象可以在激光器的近場圖像上觀測到。由于氧化限制層的折射率比該VCSEL器件結構中量子阱材料的折射率低,光可在氧化限制層與量子阱層之間形成全反射,起到橫向折射率波導的作用。為分析氧化孔形狀及大小對器件邊模抑制比的影響,對氧化孔形狀不同的兩組器件進行對比分析,結果如圖5所示。

圖5 氧化孔形狀不同而臺面直徑相同的VCSEL的邊模抑制比

在圖5中,器件B、E的臺面直徑為23 μm,邊模抑制比分別為38 dB和10 dB,器件A、D的臺面直徑為27 μm,邊模抑制比分別為36 dB和25 dB。從測試結果可知,器件氧化孔形狀接近圓形時,邊模抑制比較高。器件A、B的氧化孔為橢圓形,橢圓形氧化孔在長軸和短軸方向上的折射率不均勻,會造成多個模式的輸出,邊模抑制比降低。

圖6所示為氧化孔均為圓形,臺面結構直徑分別為27,23,21 μm的3個VCSEL器件邊模抑制比的測試結果,器件激射波長為894.6 nm。器件A、B、C的邊模抑制比分別為37 dB、38 dB、30 dB,器件A、B的氧化孔為圓形,且邊模抑制比相差較小。器件C雖為補償型刻蝕結構,但由于氧化時間稍長,導致氧化孔尺寸過小,氧化的各項異性較為明顯,因此邊模抑制比稍低。隨著氧化孔直經增大,器件激射模式分布的各向異性變小,各個模式波長更接近中心波長,相鄰模式之間的距離隨之變小,激射模式表現為單模激射。從測試結果分析可知,VCSEL器件臺面直徑對器件邊模抑制比的影響較小,而氧化孔的形狀及大小對VCSEL器件邊模抑制比的影響較大。當氧化孔接近圓形時,邊模抑制比較高,這說明氧化孔的不規則化會引起激射波長模式的選擇相似度降低,使多個模式同時激射,導致邊模抑制比降低,這為制備高邊模抑制比VCSEL器件提供了實驗基礎。

圖6 氧化孔均為圓形但臺面直徑不同的VCSEL的邊模抑制比

4.結論

通過理論及實驗研究了臺面直徑及氧化結構對VCSEL器件激射性能的影響,研究結果表明:臺面直徑對器件的閾值電流有較大影響,氧化孔的形狀對VCSEL邊模抑制比的影響較大,圓形氧化孔器件的邊模抑制比較高。根據研究結果,利用臺面氧化補償方法制備出了具有補償型臺面結構且圓形氧化孔直徑為4.4 μm的VCSEL器件,該器件在0.6 mA驅動電流及70~90 ℃溫度下,實現了邊模抑制比高于35 dB的894.6 nm激光輸出。

-

激光器

+關注

關注

17文章

2514瀏覽量

60332 -

電荷

+關注

關注

1文章

628瀏覽量

36134 -

VCSEL

+關注

關注

17文章

264瀏覽量

30007

原文標題:垂直腔面發射激光器氧化孔結構對器件激射性能的影響

文章出處:【微信號:MEMSensor,微信公眾號:MEMS】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

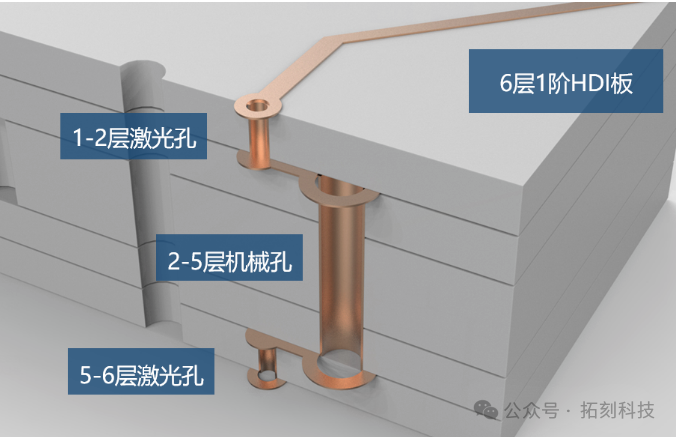

HDI的疊層結構設計

永磁發電機的主要結構設計是什么?

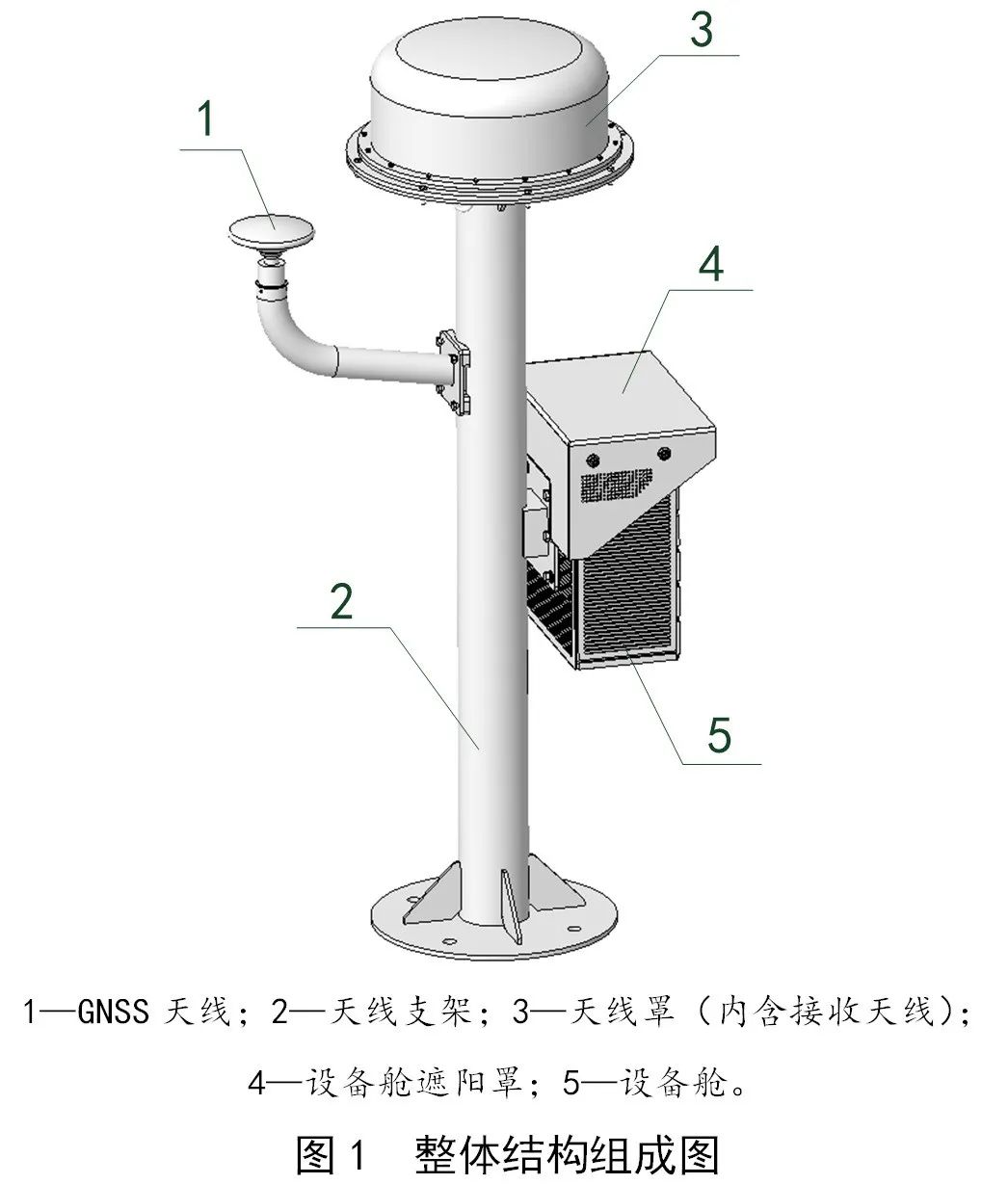

一種天線支架的結構設計及有限元分析

5針M16接口結構設計

3針M5插座結構設計

FPGA設計中,對SPI進行參數化結構設計

7芯M9插頭需采用彈性結構設計嗎

FPGA設計中,對SPI進行參數化結構設計

倒裝焊器件封裝結構設計

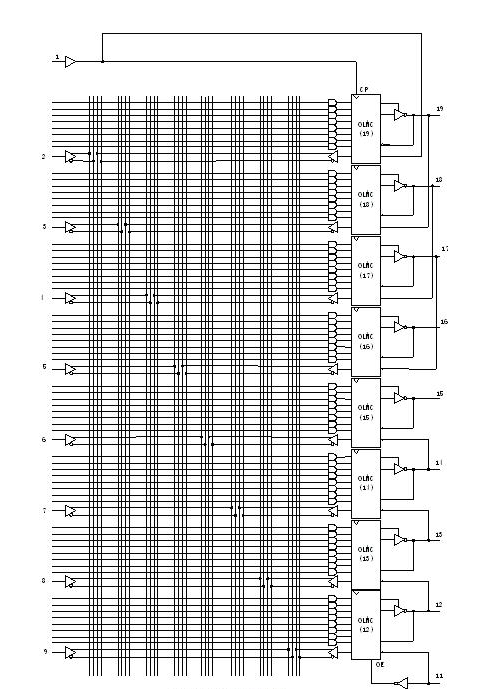

通用陣列邏輯(GAL)電路結構設計分析

LLC拓撲結構設計要點

VCSEL器件的理論分析及結構設計

VCSEL器件的理論分析及結構設計

評論