1.前言

前幾天我看到知乎上的一篇文章《時代的眼淚:繁華落盡的SPARC處理器》,大致上講述了一下Sun公司的UltraSPARC處理器,那時左批HP,右打IBM,儼然一副高高在上的氣勢。我覺得關于SPARC如何一步一步從繁榮走向平淡,又是如何在歷史長河中發揮出濃墨重彩的一筆,我就不贅述了。這篇文章主要想講一些sparc體系相關的問題。目前,sparc出現在我們視野中并不多見,其實利用sparc處理器一直是航天上面在使用,由于其特殊的架構以及目前美國對中國的態勢,sparc架構在航天、飛機、雷達領域的利用也是越來越重要了。目前北京微電子技術研究所出來幾款SPARC V8架構的芯片。其中BM3803是基于SPARC V8體系結構的32位精簡指令集的國產嵌入式芯片,其特點是功能強、可靠性高、低功耗等等。下面從系統啟動、窗口寄存器、中斷處理這三部分看一看sparc v8處理器的特點。

2.sparc 芯片啟動

一般我們做嵌入式開發都是用C語言編寫實現,但是實際情況是在系統上電的之后,一般往往會執行一段初始化的匯編代碼,可以理解為系統的BIOS。對于sparc v8架構的bm3803處理器來說,地址分配的空間如下:

一般芯片啟動后,執行的代碼都是在0地址處,所以固話的代碼放在PROM的0地址空間。

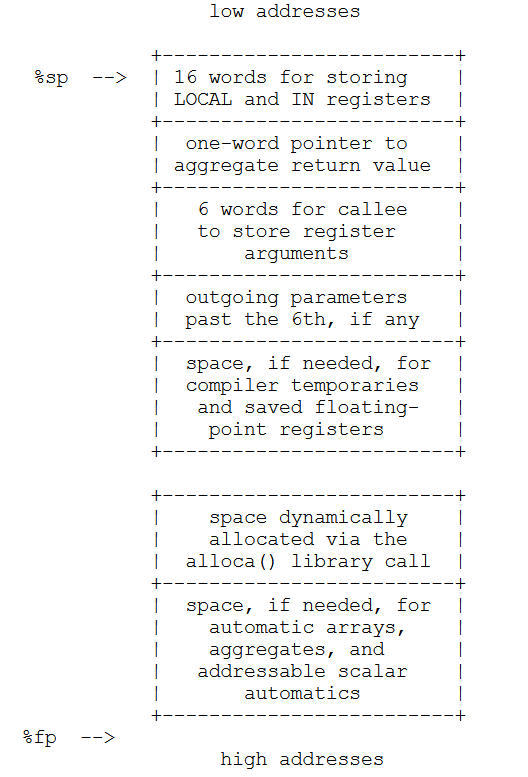

需要設置C語言可以執行的棧空間以及清除bss段。其中棧的布局可以參考如下:

3.寄存器

3.1 窗口寄存器

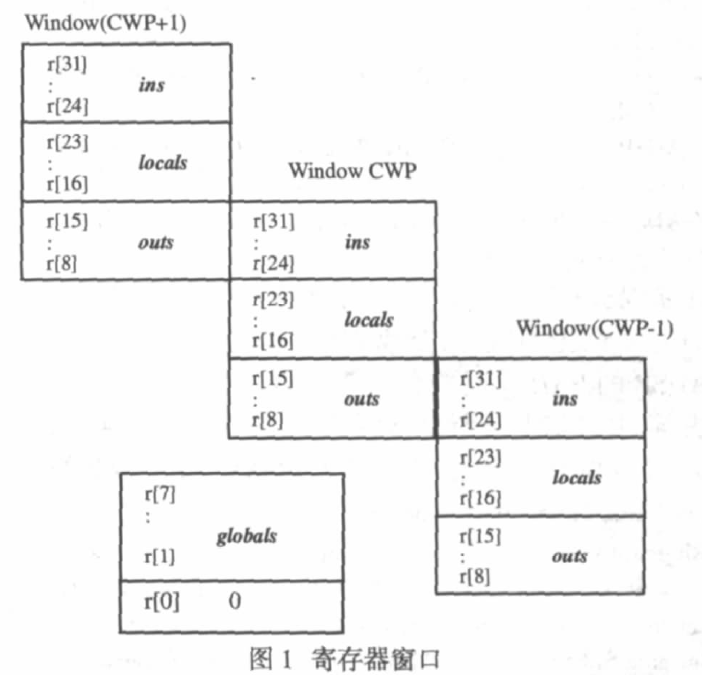

由于sparc架構集成伯克利RISC結構,所以窗口寄存器是一個非常重要的特性。也就是說,一個窗口寄存器組只對當前的程序可見。而一個寄存器窗口又包括32個無浮點的寄存器。

其中SPARC結構規定了一共可以有N個寄存器的窗口,N=2^n(1=

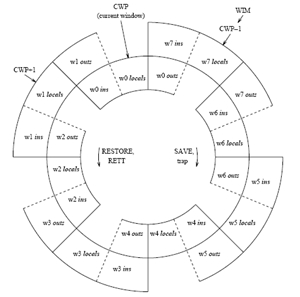

當執行SAVE指令的時候,會分配一個全新的串口CWP-1。當RESTORE指令的時候,則CWP+1。其中比較有特點是,兩個窗口是有8個寄存器公用的,也就是上一個窗口的out為下個窗口的in。這樣可以提高程序的執行效率,不用每次都處理所有的寄存器。

3.2 特殊寄存器

一般來說,sparc上的特殊寄存器需要注意的是處理器狀態寄存器(Processor State Register),名稱為%PSR。以及無效窗口標識(Widows Invalid Register),名稱為%WIM。

其中PSR主要控制CWP窗口操作、中斷處理開關、以及Trap的處理。

WIM是無效窗口,BIT0~BIT7分別對應窗口0~7,在CPU的8個寄存器窗口中只能存在一個窗口為無效窗口。

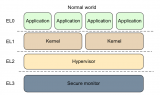

4.中斷處理

在sparc處理中斷和陷阱的時候,也是首先需要一個trap的地址。一般進入中斷后,會進入另外的一個模式,也就是說會開辟一個新的窗口,比如我們做任務切換的時候。sparc是由軟中斷(TA指令)實現。SPARC架構是不支持直接對PC指針進行操作的,而是CPU在發生中斷的時候會將當前的PC、NPC寫到寄存器%l1,%l2寄存器中。在中斷結束返回的時候,CPU自動將%l1,%l2內容寫到PC、NPC。這樣就實現了一個任務的切換過程。

當發生中斷的嵌套的時候,也是需要通過中斷棧來實現當前現場的保存。

5.總結

上述簡單的介紹了一下sparc處理器的一些特點,熟悉處理器架構的朋友可以看一下和arm、mips、risc-v體系架構的設計的異同。通過學習和理解不同處理器架構的設計思想,從而更好的掌握程序設計的最佳思路。

-

處理器

+關注

關注

68文章

19299瀏覽量

230011 -

SPARC

+關注

關注

0文章

16瀏覽量

9896

原文標題:sparc處理器淺析

文章出處:【微信號:Embeded_IoT,微信公眾號:嵌入式IoT】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

歐空局為何從SPARC換成了RISC-V

怎么通過sparc了解intel homologos處理器

抗輻射SPARC處理器在航天應用中有什么優勢?

ARM處理器的三大特點

ARM處理器的特點有哪些

ARM微處理器的特點及其架構解析

REMS操作系統在SPARC-V8處理器上的應用

SPARC微處理器綜合介紹

SPARC V8結構嵌入式微處理器的軟件集成開發環境總體設計

關于SPARC微處理器綜述

sparc處理器的特點和系統架構

sparc處理器的特點和系統架構

評論