隨著數(shù)字技術(shù)的飛速發(fā)展,電子工程師在設(shè)計(jì)中越來越多地采用FPGA來實(shí)現(xiàn)復(fù)雜的數(shù)字功能,不僅僅是簡單的時(shí)序邏輯,更多的是諸如數(shù)字濾波器、信號處理算法的實(shí)現(xiàn)等。這樣我們就必須要對FPGA設(shè)計(jì)進(jìn)行全面的性能分析,而不僅僅是時(shí)序的驗(yàn)證,這就對FPGA設(shè)計(jì)軟件的仿真功能提出了更高的要求。而現(xiàn)有的一些流行的FPGA設(shè)計(jì)工具并不能滿足這一要求。

MAX+PLUS II是ALTERA公司為自己的系列EPLD、FPGA提供的功能強(qiáng)大的設(shè)計(jì)及仿真軟件。在該軟件中,提供了從多種方法輸入、編譯一直到仿真的一系列配套功能,對于那些不是很復(fù)雜的時(shí)序邏輯設(shè)計(jì)來說,可以在一個(gè)軟件內(nèi)方便地完成所有的設(shè)計(jì)及仿真工作。而對于那些復(fù)雜的設(shè)計(jì)則顯得力不從心了。

舉一個(gè)例子:對一個(gè)基于FPGA設(shè)計(jì)的雷達(dá)信號處理機(jī),我們關(guān)心其在給定發(fā)現(xiàn)概率和虛警率的前提下的最小可檢測信噪比,或者在某一給定信噪比條件下其Pd、Pf是否能滿足要求。雖然在設(shè)計(jì)之前肯定已經(jīng)做了諸如可行性分析、性能分析等一系列的工作,但是由于數(shù)字實(shí)現(xiàn)必須考慮的一些問題,如字長效應(yīng)、算法簡化等,有可能使具體實(shí)現(xiàn)的性能比之理論分析有所下降,這個(gè)下降到底有多大?另外,采用的信號處理算法還有哪些沒有發(fā)現(xiàn)的缺陷?對設(shè)計(jì)者來說,能夠完全在軟件環(huán)境中通過仿真來解決這些問題遠(yuǎn)比在不成熟的硬件環(huán)境中反復(fù)地調(diào)試、修改來的有效率,且有更大的彈性,更容易進(jìn)行。

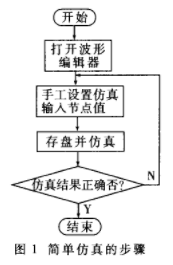

然而,當(dāng)我們想通過MAX+PLUSII軟件自帶的仿真工具對復(fù)雜設(shè)計(jì)的性能作一個(gè)評估時(shí),就會碰到許多困難。一般來說簡單仿真的步驟如圖1所示。其中,手工設(shè)置仿真輸入節(jié)點(diǎn)值只適用于輸入信號比較簡單的情況,而對于復(fù)雜的輸入信號就無能為力了。如上述雷達(dá)信號處理機(jī)的輸入信號,應(yīng)該是許多個(gè)周期的雷達(dá)同步信號、雷達(dá)回波信號加上取決于接收信道的帶限噪聲構(gòu)成的(后兩者應(yīng)有給定的信噪比關(guān)系)。這類輸入信號不僅必須經(jīng)嚴(yán)格計(jì)算得到,而且數(shù)量巨大,很難由手工輸入。

另外,一般我們對仿真結(jié)果的分析也僅限于直接觀察,只能對相對較簡單的結(jié)果作出判斷。而雷達(dá)信號處理機(jī)則必須做蒙特卡洛實(shí)驗(yàn)(海量實(shí)驗(yàn))來統(tǒng)計(jì)其性能(如統(tǒng)計(jì)給定信噪比下的Pd、Pf),或?qū)μ幚斫Y(jié)果進(jìn)行各種分析(如時(shí)頻分析)來判斷處理器是否最佳等。這樣,對仿真結(jié)果的分析也不能簡單地判斷,必須經(jīng)專門的數(shù)學(xué)計(jì)算才能給出結(jié)論。

由此看來,MAX+PLUSII的仿真功能已經(jīng)不能滿足對復(fù)雜設(shè)計(jì)進(jìn)行仿真的要求,我們必須另找方法。當(dāng)然,如果有像COSSAP這樣的軟件的話,就不存在上述問題了。但對于大多數(shù)設(shè)計(jì)者來說,他們一般很難有機(jī)會接觸到這些工作站上的大型軟件,更普及的是像MAX+PLUS II、MATLAB這樣的通用工具軟件。

我們知道,MATLAB是MathWorks公司推出的一種面向科學(xué)與工程計(jì)算的高級(語言)軟件,它集科學(xué)計(jì)算、自動控制、信號處理、神經(jīng)網(wǎng)絡(luò)、圖像處理等于一體,具有極高的編程效率。它可以極方便地產(chǎn)生各種信號,進(jìn)行各種變換、統(tǒng)計(jì),另外它的繪圖功能也極為強(qiáng)大。它的這些特點(diǎn)正好可以彌補(bǔ)MAX+PLUSII在仿真功能上的缺陷。因此,本人在這里介紹一種利用MATLAB來產(chǎn)生復(fù)雜的仿真輸入信號,并對仿真輸出信號進(jìn)行分析的方法。

1 聯(lián)合仿真方法介紹

1.1 聯(lián)合仿真流程

我們先介紹MATLAB與MAX+PLUSII聯(lián)合仿真的流程,以使大家心中有一個(gè)概念。然后再分別介紹各部分的實(shí)現(xiàn)。聯(lián)合仿真流程為:

(1)先在MATLAB中產(chǎn)生原始信號,并轉(zhuǎn)換為2/16進(jìn)制序列;

(2)利用自己編寫的MATLAB函數(shù)按一定格式生成向量文件(*.vec,純文本文件);

(3)在MAX+PLUS II中,打開你要仿真的FPGA源文件,設(shè)置為“當(dāng)前工程”并作編譯;

(4)打開simulator,選“FileInputs/Outputs”,輸入在MATLAB中生成的向量文件名,按:“確定”按鈕生成*.scf文件;

(5)進(jìn)行仿真;

(6)選菜單“FileCreate Table Files”,生成相應(yīng)的*.tbl文件(純文本文件);

(7)回到MATLAB下,運(yùn)行自己編寫的函數(shù),自動從Table文件提取需要的輸出數(shù)據(jù)、進(jìn)制轉(zhuǎn)換(變?yōu)槭M(jìn)制),生成仿真結(jié)果序列;

(8)對結(jié)果序列進(jìn)行進(jìn)一步分析、處理。

1.2 仿真輸入文件

在MAX+PLUS II的仿真輸入文件中有一種文本形式的向量文件(VectorFile),其后綴名為“*.vec。這種文件是用一定格式的文本來描述仿真信號的。我們可以很方便地使用任何純文本編輯器來書寫文件,定義仿真時(shí)間長度,以相對/絕對時(shí)間單位來定義周期重復(fù)的輸入信號(如時(shí)鐘)和其它復(fù)雜輸入信號。下面給出一個(gè)該文件的簡單例子:

%時(shí)間單位缺省為以%

START 0; %定義仿真開始、結(jié)束時(shí)間%

STOP1000;

INTERVAL 100; %定義時(shí)間步長:100ns%

INPUTS CLOCK;

PATTERN

01; %相對向量值定義:CLOCK %

%每100ns翻轉(zhuǎn)一次%

INPUTS DATAINX DATAINY;

PATTERN %定義兩個(gè)輸入信號%

%DATAINX和DATAINY%

0> 00

220> 10

320> 11 %絕對時(shí)間描述%

570> 01 %大于號前為絕對時(shí)間值%

720> 11 %大于號后為兩個(gè)輸入值%

;

INPUTS CLEAR;

PATTERN

0> 1 %產(chǎn)生寬度100ns的清零信號%

100> 0 %100ns后CLEAR信號保持高電平%

在這個(gè)例子中,定義了一個(gè)周期為200ns的時(shí)鐘信號、一個(gè)100ns以前起作用的清零信號(高電平有效)以及兩個(gè)輸入信號DATAINX、DATAINY。在實(shí)際使用時(shí),我們可以用同樣的方法方便地產(chǎn)生時(shí)鐘、復(fù)位等常用信號。而對于復(fù)雜的輸入信號,可以先用MATLAB來產(chǎn)生,然后以相對時(shí)間的方式寫入向量文件。

在產(chǎn)生復(fù)雜輸入信號之前,必須注意以下幾點(diǎn):

第一,MATLAB產(chǎn)生的是浮點(diǎn)或整數(shù)信號,而數(shù)字模塊的輸入為N位二進(jìn)制數(shù),這之間有一個(gè)進(jìn)制轉(zhuǎn)換的問題。因此,我們先要根據(jù)要采用的A/D位數(shù)對原始信號進(jìn)行量化。

第二,在MAX+PLUS II的仿真器中,數(shù)據(jù)可以采用2/8/10/16進(jìn)制顯示格式,但其十進(jìn)制顯示用的是無符號數(shù)的方式,在表示那些補(bǔ)碼形式的2/8/16進(jìn)制數(shù)時(shí)會發(fā)生錯誤,因此必須把輸入信號轉(zhuǎn)換為2/16進(jìn)制數(shù)。

第三,進(jìn)制轉(zhuǎn)換程序必須自己編制。因?yàn)镸ATLAB是用字符串來表示2/8/16進(jìn)制數(shù)的,雖然有一些進(jìn)制變換的函數(shù)(如HEX2DEC、DEC2HEX等),但尚不能滿足需要,必須在此基礎(chǔ)上自己編制新的函數(shù)。

1.3 仿真輸出文件

向量文件產(chǎn)生后,就可以進(jìn)行仿真了,仿真結(jié)果轉(zhuǎn)換成Table文件輸出。Table 文件示例如下。

INPUTS clk reset din;

OUTPUTS y;

UNIT ns; %定義時(shí)間單位%

RADIX HEX; %定義顯示進(jìn)制%

PATTERN

% r %

% e %

% csd %

% lei %

% ktn y %

0.0>X 0 0000=0000

40.0>X 1 0000=0000

50.0>0 1 0000=0000

……

1475.0>1 1 0000=0000

1500.0>X X XXXX=XXXX

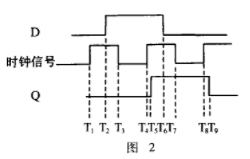

Table文件的構(gòu)成與向量文件大致相同。它的開始部分是注釋(同樣是以%…%標(biāo)注的文字),接著是對輸入/輸出信號、時(shí)間單位、顯示采用進(jìn)制的定義,第三部分就是對輸入/輸出信號在仿真后的列表。其中,“>”號以前的是時(shí)間值,“=”號后面則是我們關(guān)心的仿真輸出結(jié)果了。根據(jù)Table文件的這些特點(diǎn),我們可以編制MATLAB函數(shù)將關(guān)心的東西(如時(shí)間值、某輸出結(jié)果)提取出來形成數(shù)據(jù)序列,以便后續(xù)處理。在這里要注意一個(gè)問題,就是Table文件中會對每一個(gè)信號的變化時(shí)刻都進(jìn)行記錄,我們用圖2的一個(gè)簡單的D觸發(fā)器的部分仿真時(shí)序來作說明,圖中示出了D觸發(fā)器的輸入信號D、時(shí)鐘,以及其輸出信號Q,在這一段仿真中,Table文件會記錄從T1~T9的9個(gè)信號變化的時(shí)刻,這使得輸出信號的每一個(gè)值被記錄了多次。如果我們對此不加甄別就照單全收的話,就會對此后的分析工作帶來麻煩。因此,對于同步數(shù)字系統(tǒng),我們只應(yīng)提取那些我們關(guān)心的時(shí)鐘上沿/下沿時(shí)刻的輸出值。

2 應(yīng)用實(shí)例

本人在自己的設(shè)計(jì)工作中使用了以上介紹的這種方法。我設(shè)計(jì)的是一個(gè)單脈沖雷達(dá)回波信號處理機(jī),基本原理是信號的能量積累后檢測,其中采用了較復(fù)雜的信號處理算法,在原理驗(yàn)證階段采用的是固定門限檢測。在用MAX+PLUSII設(shè)計(jì)完該信號處理機(jī)后,現(xiàn)實(shí)的問題就是要在給定Pd、Pf的條件下,根據(jù)具體的算法確定檢測門限。我們先在接收機(jī)上對接收機(jī)噪聲用示波器進(jìn)行了測量并存儲了大量數(shù)據(jù),然后將測量結(jié)果讀入MATLAB,形成一維數(shù)組。然后按以上介紹的方法對噪聲數(shù)據(jù)進(jìn)行兩種處理:一是產(chǎn)生模擬回波信號(或采用真實(shí)回波信號采樣序列)、信號噪聲按一定信噪比混合、加上同步脈沖后形成多個(gè)周期的“有信號回波”,二是完全是噪聲的“無信號回波”;再結(jié)合其它必要的輸入信號(如時(shí)鐘信號、復(fù)位信號等)生成向量文件,在MAX+PLUSII中仿真后,分別提取仿真結(jié)果中的“有/無信號”的兩種能量積累結(jié)果進(jìn)行分析,初步確定檢測門限,并由此結(jié)合理論分析對其檢測性能進(jìn)行評估。

當(dāng)然,這種完全在軟件環(huán)境中進(jìn)行性能分析的方法并不是萬能的,它只能也只應(yīng)起到輔助的作用,我們采用它的目的是為了使我們的設(shè)計(jì)變得更經(jīng)濟(jì)、更省時(shí)、更可靠。畢竟,一個(gè)設(shè)計(jì)最終是要形成硬件,并在實(shí)際應(yīng)用中去真正檢驗(yàn)它的品質(zhì)的。

總之,由于FPGA方便靈活的特點(diǎn),使得這種器件在數(shù)字設(shè)計(jì)領(lǐng)域的應(yīng)用越來越廣泛。而作為一個(gè)設(shè)計(jì)者,必須利用FPGA設(shè)計(jì)軟件的開放性,充分利用其它各種手段來保證我們的設(shè)計(jì)的可靠性,提高設(shè)計(jì)的品質(zhì)。

責(zé)任編輯:gt

-

FPGA

+關(guān)注

關(guān)注

1643文章

21939瀏覽量

613264 -

matlab

+關(guān)注

關(guān)注

188文章

2994瀏覽量

233054 -

仿真

+關(guān)注

關(guān)注

51文章

4229瀏覽量

135225 -

PCB設(shè)計(jì)

+關(guān)注

關(guān)注

396文章

4765瀏覽量

88938 -

可制造性設(shè)計(jì)

+關(guān)注

關(guān)注

10文章

2065瀏覽量

15963 -

華秋DFM

+關(guān)注

關(guān)注

20文章

3498瀏覽量

5202

發(fā)布評論請先 登錄

基于MAX+plusⅡ開發(fā)平臺的EDA設(shè)計(jì)方法

基于MAX+plusⅡ開發(fā)平臺的EDA設(shè)計(jì)方法

MAX+Plus II應(yīng)用介紹及系統(tǒng)特點(diǎn)

Max+plusⅡ設(shè)計(jì)步驟

MAX PLUS II軟件的學(xué)習(xí)

max+plus問題

MAX+Plus ii 軟件

Max+Plus II簡易用戶使用入門指南

Altera MAX+plus II 介紹

MAX+PLUSⅡ的設(shè)計(jì)處理

MAX+PLUSⅡ的層次設(shè)計(jì)

利用MATLAB增強(qiáng)MAX+PLUS II的仿真功能

評論