場對更高帶寬和更高數據速率的需求日益增加,系統頻率和調制速率要求不斷提高。隨著應用進入消費市場,低功耗變得至關重要。在滿足這些要求的同時,還需要保證:不會犧牲電氣性能或功能。為了滿足這些要求,除了改善進信噪比(SNR)、誤碼率(BER)和用戶熟悉的優質服務外,還必須改善本地振蕩器(LO)的相位噪聲。

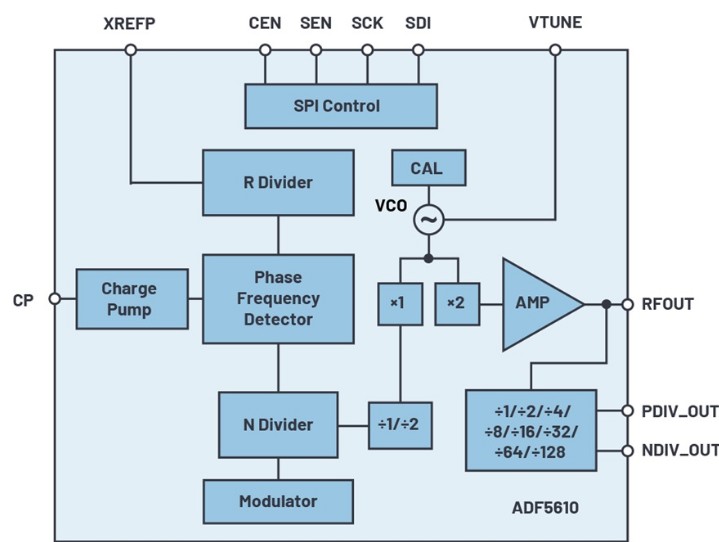

ADF5610 是一款集成式鎖相環(PLL)和壓控振蕩器(VCO),充分體現了 ADI 致力于解決這些問題最終取得的成果。

頻率覆蓋范圍

ADF5610 總共覆蓋 8 個倍頻,VCO 基波頻率范圍為 3.65 GHz 至 7.3 GHz,此頻率可反饋給 PLL,以最小化相位噪聲。單端輸出(RFOUT)使基波頻率翻倍,可提供 7.3 Ghz 至 14.6 GHz 頻率,而差分輸出通過使用 1/2/4/8/16/32/64/128 分頻設置,同時支持 57 MHz 至 14.6 GHz 全頻率范圍。

圖 1. ADF5610 的功能框圖。

ADF5610 的 VCO 架構可實現出色的寬帶頻率合成器性能,同時保持行業領先的相位噪聲性能,在 10 GHz 、100 kHz 偏置時,標稱開環相位噪聲為–114 dBc/Hz。在僅使用一個無源環路濾波器的情況下,內部狀態機就可以使頻率建立時間低于 40 μs;除非需要更快的建立時間,否則無需使用額外的電路或查找表(LUT)。

雖然 ADF5610 內部的鎖相環(PLL)具有中等品質因數(FOM) –229 dBc/Hz(高電流模式下為–232 dBc/Hz),但考慮到 1/f 噪聲(–129 dBc/Hz)和出色的 VCO 相位噪聲特性,則可以實現低于 38 fs(1 kHz 至 100 MHz 集成限值)的 rms 抖動。因此,ADF5610 非常適合要求嚴苛的轉換器時鐘應用。環路濾波器電阻值應保持最小,以在高頻率(100 MHz)范圍內實現較低的熱噪聲。為了達到這個性能水平,必須使用超低噪聲基準電壓源。

圖 2. RMS 抖動:8.0 GHz。

圖 3. RMS 抖動:14.4 GHz。

除了很寬的頻率覆蓋范圍、行業領先的相位噪聲和極快的鎖定時間之外,ADF5610 還具有其他特性,因此非常適合無線和儀器儀表應用。在這些應用中,ADF5610 一般作為本地振蕩器使用。

24 位小數分辨率相當不錯,與 ADF5610 的精確頻率模式功能配合使用時,有可能實現零(0 Hz)誤差頻率生成。將 ADF5610 用作本地振蕩器時,因為標稱輸出功率為 5 dBm,所以可以直接通過 RFOUT

端口驅動有源混頻器,這樣無需額外的放大電路,可以節省寶貴的電路板空間。采用單端方式使用時,差分分頻器(PDIVOUT/NDIVOUT)的標稱輸出功率為 2 dBm,但是,在窄帶應用中,可以通過低損耗巴倫或混合耦合器將差分進行組合,以實現 1~2dB 輸出功率的增加。

如今低功耗非常重要,ADF5610 在低電流模式、禁用輸出分頻器時,只消耗低于 700 mW 的功率,即使在最壞情況(高性能模式,輸出分頻器設為 128 分頻)下,其功耗稍高于 1 W。即使在低電流模式下,ADF5610 的相位噪聲性能在同類產品中也處于領先水平,僅增加 2 dBc/Hz。

ADF5610 還具有出色的雜散性能,PFD 雜散低至 -105 dBc,帶內未濾波的整數邊界雜散標稱值為 -45 dBc。

小尺寸

ADF5610 PLL/VCO 采用 7 mm × 7 mm、48 引腳基板柵格陣列(LGA)封裝。工作時只需極少的外部去耦,因此可以使用小型解決方案實現出色性能。為實現最佳性能,建議使用優質低壓降(LDO)穩壓器,例如 ADM7150, LT3045/LT3042 或 HMC1060。VCO 需要 5 V 電源,其余的電路則使用 3.3 V 電軌供電。ADF5610 可以使用 ADI simPLL?進行仿真,以幫助用戶設計實現完整的 PLL 頻率合成器所需的適當外部元件電路。

結論

ADF5610 具備行業領先的頻率覆蓋范圍、出色的相位噪聲性能、高輸出功率、低功耗和小尺寸,因此能夠滿足新通信和儀器儀表系統的嚴苛要求。

責任編輯:pj

-

頻率合成器

+關注

關注

5文章

220瀏覽量

32363 -

分頻器

+關注

關注

43文章

447瀏覽量

49956 -

混頻器

+關注

關注

10文章

680瀏覽量

45707

發布評論請先 登錄

相關推薦

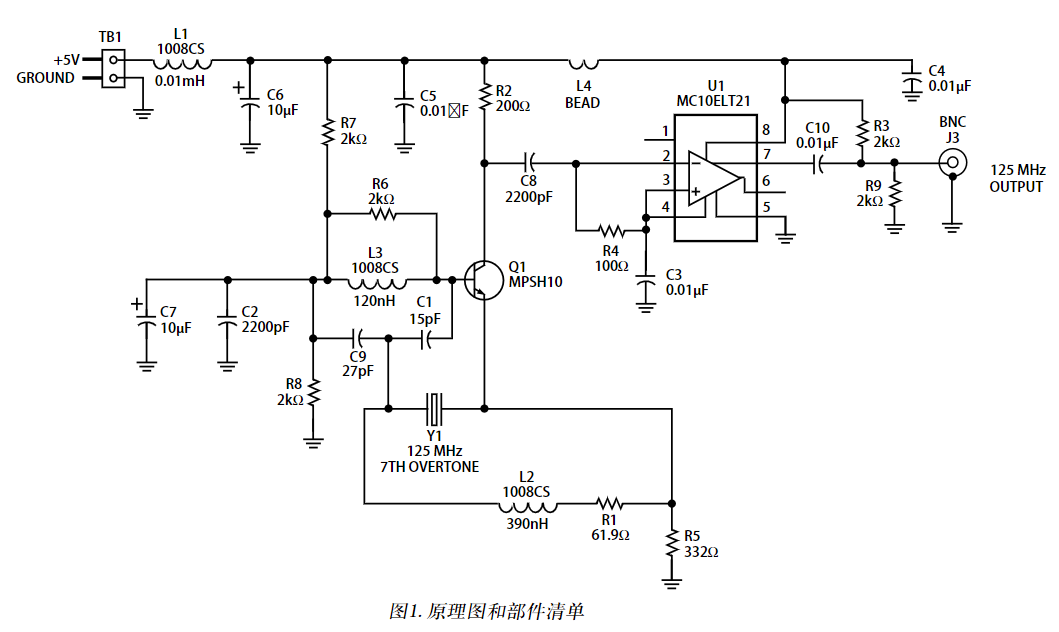

完整的直接數字頻率合成器 AD9850 的分立、低相位噪聲、125MHz 晶振解決方案

鎖相環PLL與頻率合成器的區別

CDCEx937-Q1可編程3-PLL VCXO時鐘頻率合成器數據表

環路濾波器電阻值實現完整的 PLL 頻率合成器所需的外部元件電路

環路濾波器電阻值實現完整的 PLL 頻率合成器所需的外部元件電路

評論