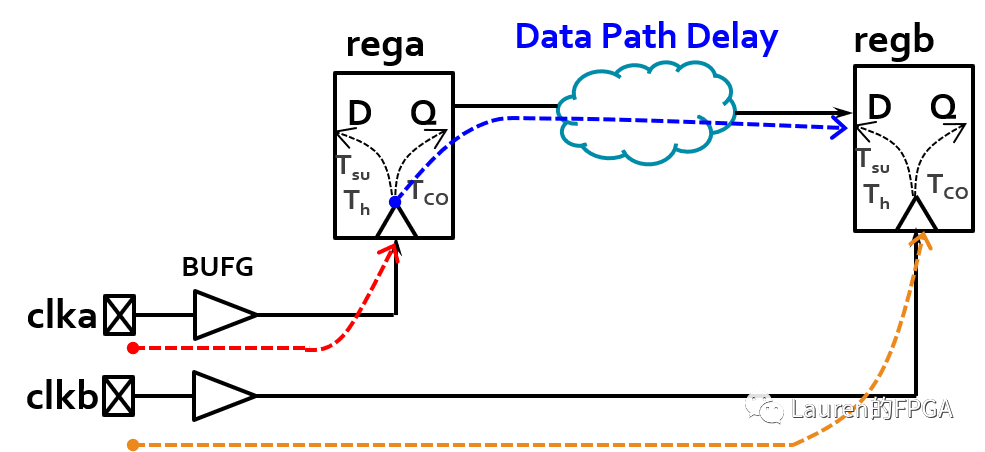

更為具體的時序報告信息如何從中獲取,或者如何根據時序報告發現導致時序違例的潛在原因呢? 首先,我們要了解時序路徑的構成,如下圖所示。不難看出,對于一條典型的觸發器+組合邏輯+觸發器的時序路徑,它由三部分組成:源時鐘路徑(發送時鐘路徑)、數據路徑和目的時鐘路徑(接收時鐘路徑)。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

時序

+關注

關注

5文章

387瀏覽量

37331

原文標題:如何閱讀時序報告

文章出處:【微信號:Lauren_FPGA,微信公眾號:FPGA技術驛站】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

一文詳解信號的回流路徑

最近在看JT大佬出的一本高速PCB設計書籍,看到回流路徑這里,讓我想到最近兩個群里都提到關于這個知識點的問題。書籍很好,但是也會有一些疑問,帶著這些疑問我也查找了相關資料,我想著盡可能的結合書中知識以及自己的理解,把這個問題能給

干貨滿滿!一文了解AGV軟件系統的構成

AGV系統由調度、車載控制、導航導引三部分構成,實現物流自動化智能化。調度系統分配任務,車載系統控制導航裝卸,導航導引確保精確行駛。AGV采用雙控系統,提高適應性,用戶可實時查看運行狀態。

時序邏輯電路中如何判斷有效狀態和無效狀態

在時序邏輯電路中,有效狀態和無效狀態的判斷是電路分析和設計的重要環節。有效狀態是指電路在實際工作過程中被利用到的狀態,它們構成了電路的有效循環;而無效狀態則是指那些沒有被利用到,或者雖然存在但不影響電路正常工作的狀態。以下是對如何判斷時

電源時序器的原理及使用方法是什么

電源時序器是一種用于控制多個電源設備按照一定順序開啟或關閉的電子設備。它廣泛應用于音響、舞臺燈光、電視廣播、工業自動化等領域。本文將介紹電源時序器的原理及使用方法。

FPGA 高級設計:時序分析和收斂

結果當然是要求系統時序滿足設計者提出的要求。

下面舉一個最簡單的例子來說明時序分析的基本概念。

假設信號需要從輸入到輸出在FPGA 內部經過一些邏輯延時和

發表于 06-17 17:07

TDK最新xEV解決方案,一文全知道!

TDK最新xEV解決方案,一文全知道! TDK致力于為各類xEV提供廣泛的產品組合,進而推動未來汽車的發展。 TDK在汽車行業中發揮著至關重要的作用,尤其是在電動汽車時代,從先進的電力電子器件

求助,求大神幫忙解答下AN65974同步Slave FIFO的讀時序

你好,在AN65974文檔中,我看不懂同步Slave FIFO的讀時序,你可以給我解讀一下么? 下圖中有我標注的我不懂的問題。非常感謝你!......

發表于 05-31 06:27

Xilinx FPGA編程技巧之常用時序約束詳解

Register-to-Register Constraint

寄存器到寄存器約束往往指的是周期約束,周期約束的覆蓋范圍包括:

覆蓋了時鐘域的時序要求

覆蓋了同步數據在內部寄存器之間的傳輸

分析一個單獨的時鐘域內的路徑

分

發表于 05-06 15:51

FPGA工程的時序約束實踐案例

詳細的原時鐘時序、數據路徑時序、目標時鐘時序的各延遲數據如下圖所示。值得注意的是數據路徑信息,其中包括Tco延遲和布線延遲,各級累加之后得到

發表于 04-29 10:39

?770次閱讀

Xilinx FPGA編程技巧之常用時序約束詳解

寄存器到寄存器約束往往指的是周期約束,周期約束的覆蓋范圍包括:

覆蓋了時鐘域的時序要求

覆蓋了同步數據在內部寄存器之間的傳輸

分析一個單獨的時鐘域內的路徑

分析相關時鐘域間的所有路徑

發表于 04-12 17:39

時序邏輯電路輸出與什么有關 時序邏輯電路由哪兩部分組成

組成:組合邏輯電路和時鐘電路。組合邏輯電路是一種基本的邏輯電路,其輸出僅僅取決于當前的輸入信號,與時間無關。組合邏輯電路由門電路(如與門、或門、非門等)組成,通過門的組合和連接構成了復雜的邏輯功能。時序邏輯電路將

時序電路的分類 時序電路的基本單元電路有哪些

時序電路是一種能夠按照特定的順序進行操作的電路。它以時鐘信號為基準,根據輸入信號的狀態和過去的狀態來確定輸出信號的狀態。時序電路廣泛應用于計算機、通信系統、數字信號處理等領域。根據不同的分類標準

FPGA設計的常用基本時序路徑分析

該條路徑包括了觸發器內部clock-to-Q的延遲,觸發器之間的由組合邏輯造成的路徑延遲以及目標觸發器的建立時間,其延時是數據從源觸發器開始,在下一個時鐘沿來到之前通過組合邏輯和布線的最大時間

一文知道時序路徑的構成

一文知道時序路徑的構成

評論