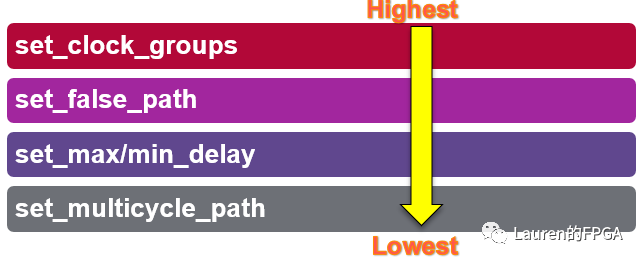

約束的優先級

XDC描述的時序約束是有優先級的,尤其是涉及到時序例外的約束,如set_clock_groups、set_false_path、set_max_delay和set_multicycle_path。如果這些約束施加到同一條路徑上,那么其優先級如下圖所示。

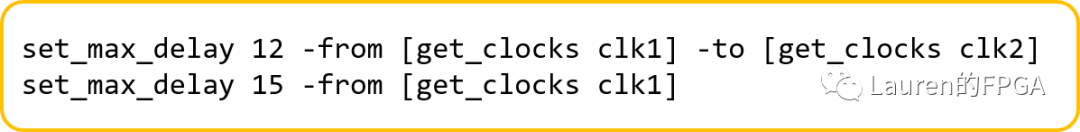

對于同類型的約束,遵循的原則則是越具體的優先級越高。如下圖所示,都是set_max_delay約束,且都使用了-from和-to,顯然第一條約束比第二條約束更具體,因此,第一條約束優先級高于第二條約束,第二條約束將被部分覆蓋。這里部分覆蓋的含義是凡是從clk1到clk2的路徑,都遵守最大延遲為12ns的要求,但如果設計中存在從clk1到clk3的路徑,則仍然按15ns進行約束。

-

Delay

+關注

關注

0文章

10瀏覽量

11040 -

xdc

+關注

關注

1文章

24瀏覽量

6019 -

華秋DFM

+關注

關注

20文章

3501瀏覽量

5216

原文標題:如何使set_max_delay不被覆蓋

文章出處:【微信號:Lauren_FPGA,微信公眾號:FPGA技術驛站】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

GPS北斗定位模塊問題及解決辦法

蜂鳥板上Openharmony系統跑QT程序

Profinet IO通信故障原因及解決辦法

地震前后植被覆蓋變化與地震烈度關系探究

常見墊圈故障及解決辦法 防漏墊圈的設計與應用

雷達探測器常見故障及解決辦法

PCBA板常見故障及解決辦法

溫控器常見故障及解決辦法

常見MCU故障及解決辦法

常見元器件故障及解決辦法

海外大帶寬服務器連接失敗解決辦法

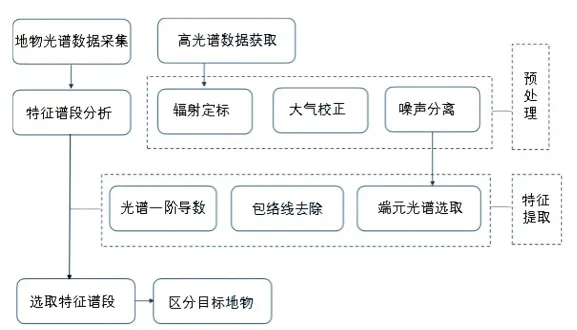

高光譜遙感技術在高植被覆蓋區域地質調查中的應用

評論