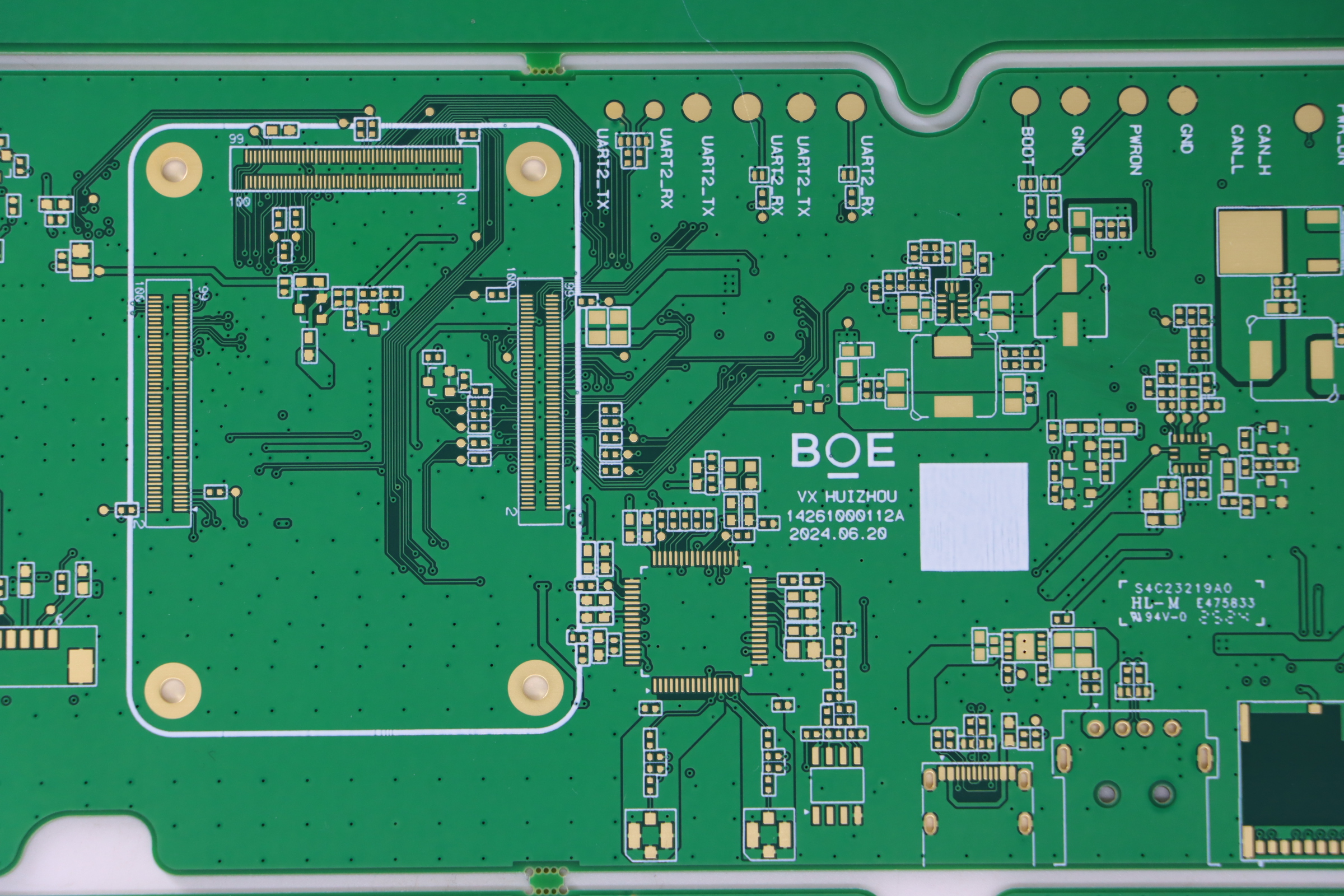

從電視到筆記本電腦,我們最喜歡的許多消費類電子產品實際上都是多板系統。打開筆記本電腦或臺式機,您會發現一個功能豐富的多板系統,該系統帶有電纜和板載連接器,這些電纜和板載連接器可將主板和系統中的外圍設備連接起來。隨著計算機外圍設備運行速度的提高,多板設計中的正確接地和保持干凈的高速信號對于保持低誤碼率(BER)值并通過EMC測試至關重要。

每塊板上的高速設計

多板系統中的各個板應始終設計為確保高速系統中的信號完整性。電路板上的高速信號應進行布線,以防止由于傳輸線效應而引起的串擾和振鈴,并具有適當的,不間斷的返回路徑以保持信號完整性。接地也是單個板上的重要問題,但是當作為多板系統的一部分在板之間發送高速信號時,接地就變得尤為重要。

許多新手設計師都錯過了高速設計的重點是:數據傳輸速率并不能確定一塊板是否屬于高速。取而代之的是,將開和關狀態之間的切換速度歸類為高速。

現代數字IC的體積越來越小,從而減少了其柵極電容和切換時間。即使您正在使用數據速率較低的通信協議(例如串行外圍設備接口(SPI)總線),較新的數字IC也會以足夠快的速度切換,以使您的設備可以歸類為高速設備。

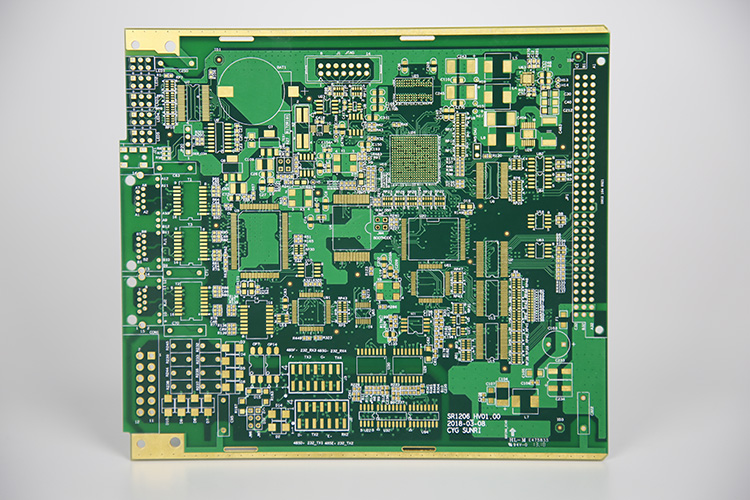

請牢記這一點,在設計電路板時,需要根據電路中的切換時間檢查互連長度。如果25%的信號上升時間(10%至90%)小于沿走線的傳播延遲,則走線將充當傳輸線,您需要將走線與源和負載進行阻抗匹配,在電源或負載處增加端接,或使用阻抗控制設計以確保走線阻抗與電源和負載相匹配。這將防止反射導致數字信號振鈴。

在路由具有并行數據的信號網時,您需要確保網絡內的信號是同步的,以防止時序偏斜。應當在單個板內部以及板之間補償時序偏斜,以免信號不同步導致BER值較高。這需要信號網絡內的長度匹配跡線,包括差分對之間的長度匹配。小心差分對,并在可能的情況下嘗試在布線和長度匹配方案中強制對稱。

多板設計中的接地和高速信號

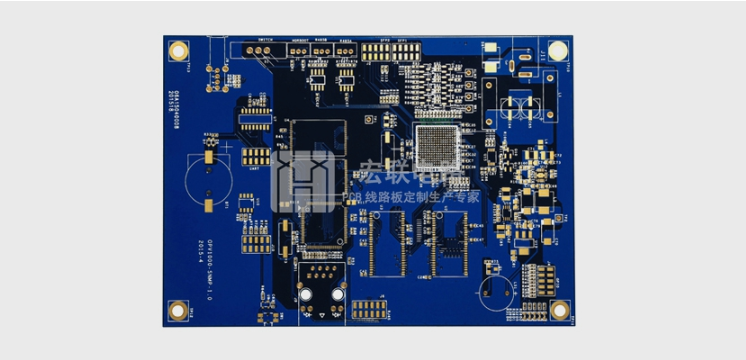

在多板系統中的板之間路由高速信號時,需要設計連接方式,以便信號具有可靠的接地返回路徑。如果您忽略了這一點,那么您的返回信號將被迫沿著長途路線經過目標板上的接地連接,再經過電源或機箱,再進入源板。本質上,您剛剛創建了一個巨大的環形天線,并且您的系統可能不會通過EMC檢查。

最簡單的方法是在兩塊板之間發送信號時使用差分信號。但是,這要求電路板兩端的組件都支持差分信號傳輸,而這并非總是可能的。這不能容納所有通信協議(例如I2C)。

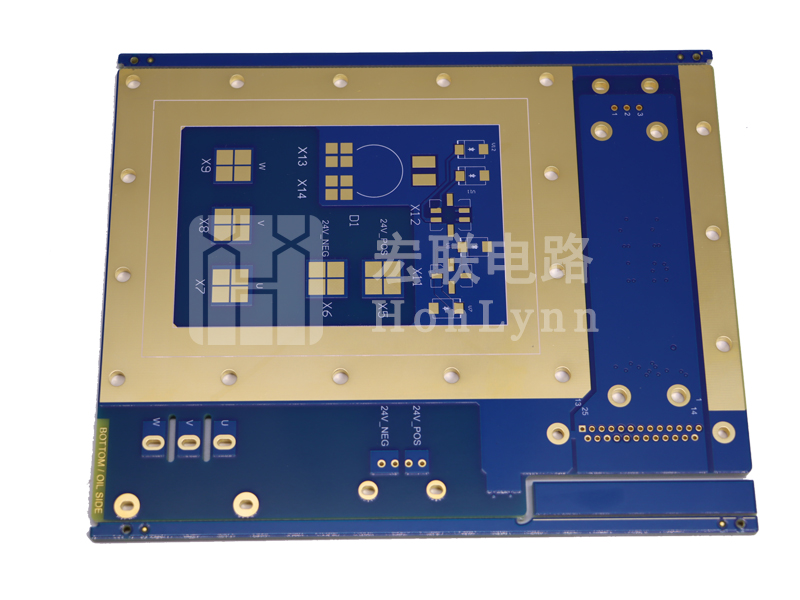

在不可能進行差分信號傳輸的地方,您將需要利用源和目標板上的接地層來為電路板之間路由的信號提供返回路徑。例如,考慮連接到電源的兩個板。源板使用FPGA或其他組件提供某些處理,目標板包含一些需要接收一些數據的外圍組件。

為了為在這些板之間路由的信號提供一個短的返回路徑,您將需要包括一條貫穿您的連接的接地連接。您可以將源板上連接器上的一個引腳連接到源板上的接地層。然后,您需要對目標板上的連接器執行相同的操作。

本質上,現在您的連接電纜中有一個接地連接,該接地連接與信號所在的平面相同。這種參考選擇極為重要:您必須將此接地連接參考到與您的信號相同的參考平面,否則可能會產生接地環路。如果您有備用的引腳,則最好在板之間的連接中(最好是在相鄰信號之間)放置多個接地,因為這會減少高速切換期間的接地反彈。

實際上,在設計并行數據的標準協議時要考慮到這種接地方案。如果查看DDR4或PCIe 等標準協議的規范,則會發現這些多板接口的引腳布局經過專門設計,在接口上具有多條接地線,以便為信號輸入提供多個返回路徑。連接。

-

PCB線路板

+關注

關注

10文章

434瀏覽量

19902 -

PCB打樣

+關注

關注

17文章

2968瀏覽量

21726 -

電路板打樣

+關注

關注

3文章

375瀏覽量

4718 -

華秋DFM

+關注

關注

20文章

3494瀏覽量

4568

發布評論請先 登錄

相關推薦

HDI線路板和多層線路板的五大區別

生產HDI線路板需要解決的主要問題

hdi線路板生產工藝流程

HDI線路板和高多層板的區別

多線路板設計中的接地連接和高速信號

多線路板設計中的接地連接和高速信號

評論