MDC/MDIO接口是為MII總線接口定義的,在802.3協議clause 22中有詳細的介紹,MII用于連接MAC和PHY,包含兩種信號:

1.數據接口,用于MAC和PHY之間接收和發送以太網數據

2.一個PHY管理接口,即MDIO接口,用于讀寫PHY的控制寄存器和狀態寄存器。

本文主要描述PHY的管理接口,MDIO/MDC.

MDIO總線只支持 MAC作為主設備,PHY作為從設備。MIDO支持兩種時序,分別為Clause 22和Clause 45.

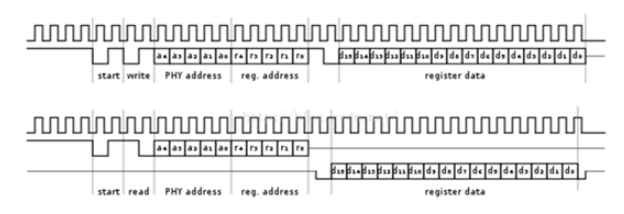

MDIO clause 22 是 MDIO 使用的一種信號時序,在這個信號時序模式,MAC 先向 MDIO 信號線上拍 32 個周期,接著傳輸 16 bit 的控制位。16 個信號位包含了兩個開始位, 2 個訪問控制位,5 bits 的 PHY 地址,5 bits 的寄存器地址,以及 2 bits 的翻轉位。 當進行寫操作的時候,MAC 在接下來的周期中提供地址和數據;當進行讀操作的時候, PHY 會翻轉 MDIO 之后向 MDIO 信號線上發送數據。

MDIO也支持 Clause 45時序,其是 Clause 22的拓展協議。與 Clause 22不同的是, 16位中的起始位:Clause 22是 00, 而 Clause 45是 01.

MDC (Management Data Clock), MDC是由MAC管理實體輸出給PHY,作為管理數據MDIO的參考時鐘信號,在上升沿觸發MDIO的讀寫。MDC是一個非周期性的信號,最小時鐘周期為400ns,與MII中的TX_CLK和RX_CLK無關。

MDIO(Management Data Input Output),MDIO是一個雙向信號線,用來傳輸PHY的控制和狀態信息。控制信息由MAC驅動,狀態信息有PHY驅動。MDIO信號線初始為三態,由MAC或者PHY來驅動信號。

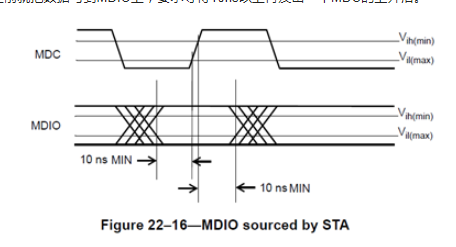

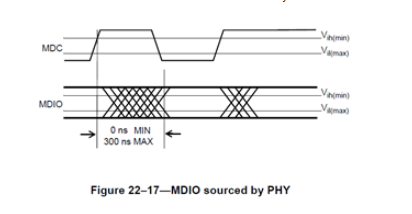

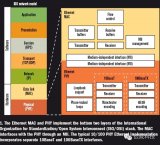

MDC/MDIO時序圖

當MDIO由MAC驅動的時候,MAC芯片提供最小10ns的建立時間和最小10ns的保持時間。

需要注意的是,為了保證PHY能準確采樣,當MAC向MDIO寫數據的時候,需要在MDC的上升沿之前就把數據寫到MDIO上,要求等待10ns以上再發出一個MDC的上升沿。

當MDIO由PHY芯片驅動時候,由MAC芯片在MDC的上升沿進行采樣。而為了保證MAC能準確采樣,當PHY向MDIO寫數據時,這個clock-to-data的delay時間范圍可以是0-300ns(小于上面提到的400ns)。

Preamble+Start:32bits的前導碼以及2bit的開始位。

OP Code:2bits的操作碼,10表示讀,01表示寫

PHYAD:5bits的PHY地址,一般PHY地址從0開始順序編號,例如6口switch中PHY地址為0-5。

REGAD:5bits的寄存器地址,即要讀或寫的寄存器。

Turn Around:2bits的TA,在讀命令中,MDIO在此時由MAC驅動改為PHY驅動,并等待一個時鐘周期準備發送數據。在寫命令中,不需要MDIO方向發生變化,則只是等待兩個時鐘周期準備寫入數據。

Data:16bits數據,在讀命令中,PHY芯片將讀到的對應PHYAD的REGAD寄存器的數據寫到Data中,在寫命令中,MAC將要寫入對應PHYAD的REGAD寄存器的值寫入Data中。

Idle:空閑狀態,此時MDIO無源驅動,處高阻狀態,但一般用上拉電阻使其處在高電平。

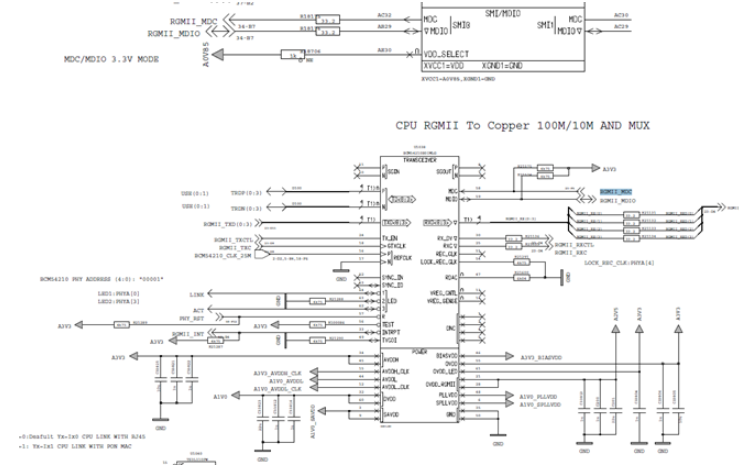

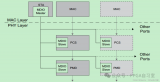

Marvel CN71XX的SMI電路圖

CN71XX的CPU有兩個SMI的管理接口,其中SMI0連接到了BCM54210的PHY芯片。

-

以太網

+關注

關注

40文章

5436瀏覽量

171934 -

Mac

+關注

關注

0文章

1107瀏覽量

51536 -

時鐘信號

+關注

關注

4文章

449瀏覽量

28583

發布評論請先 登錄

相關推薦

使用DP83822IRHBR和AM4376進行RGMII通訊時,無法建立通訊怎么解決?

使用ethernetLan8720進行以太網,運行兩天報內存問題為什么?

IDF4.4.6中esp_eth_mac_new_esp32函數能用什么替代?

如何快速理解PHY芯片

以太網中MDIO協議工作原理與應用

【ElfBoard】網口硬件分享

一文詳解以太網MAC芯片與PHY芯片

PHY的管理接口MDIO/MDC時序圖解析

PHY的管理接口MDIO/MDC時序圖解析

評論