設計說明:

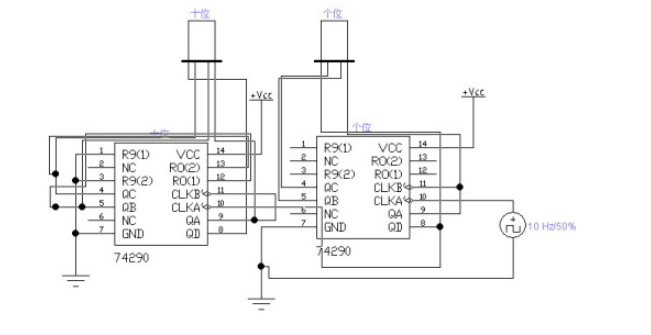

1. 秒鐘與分鐘顯示電路:

分秒顯示為60進1,利用兩片74290組成的60進制計數器如下圖所示,輸入計數脈沖CP加在CLKA’端,把QA與與CPLB’從外部連接起來,電路將對CP按照8421BCD碼進行異步加法計數。通過反饋端,控制清零端清零,其中個位接成十進制形式,十位接成六進制形式

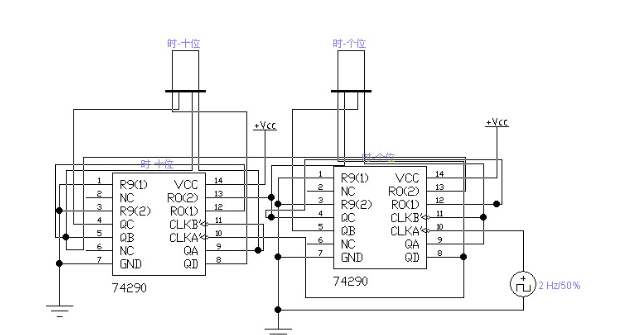

2. 時鐘顯示電路:

本設計采用24小時進制,用兩片74290連接成24進制計數器,計數信號由分鐘顯示電路提供,即當分鐘為60時小時計數加一。個位同樣接成十進制形式,十位也接成十進制形式,當十位為2個位為4時通過反饋電端,控制個位和十位同時清零,這樣就可以按23翻0規律記數了。電路圖如下所示:

連接成總電路時,輸入方波信號由分鐘計數器提供。

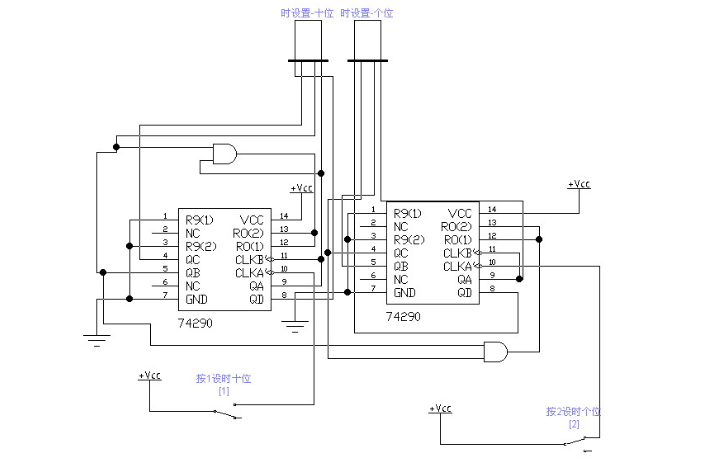

3. 調時調分電路:

本設計的調時與調分操作可以直接在時間的顯示器中直觀操作,用二個高電位分別與小時的個位計數信號與分鐘的個位計數信號或運算后作為計數信號輸入。高電位的輸入用二個開關控制,每開關閉全又斷開一次則相應地給計數器一個高電位的干擾信號,些時相應的計數器計數加一,從而實現調時和調分功能,設定按A為小時設置,按B為分鐘設置。具體電路看總電路圖。

4. 整點報時電路:

當分鐘為59,秒鐘也為59時,表明整點將要來到,這里將分鐘計數器與鈔鐘計數器的輸出端中為1的端引出,用一7421門進行與運算后變為二個輸出端,然后輸入到一個與門進行與運算,最后將輸出端輸出到整點報時器,這里用一個發光二極管表示,只有當分鐘為59同時秒鐘也為59時,這時引出的8個輸出端才會同時為1,經過二次與運算后還是為1,即給整點報時器一個高電位信號,從而讓報時器報時。當時間為任何其它的數字時,最后輸出端都不是1,即都不會報時。具體電路看總電路。

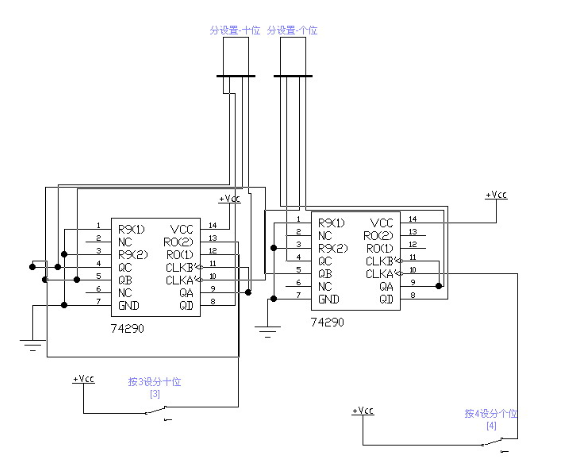

5.定時鬧鐘電路:

本設計小時的十位與個位,分的十位與個位分別用一個開關控制設置,各個開關對應打開關閉一次時,對應的計數器對應計數加一,分別用“1”“2“3”“4”設置,時鐘的定時電路如下所示:

個位為十進制,十位為三進制,當十位為2時,通過反饋控制端,個位不能大于等于4,即小時十位為2時,個位加到4時十位和個位馬上全部置0,從而讓小時的設置只能最大設為23,這樣就不會設錯。當十位不是2時,個位則加到9時再加一位則置0。其中,分定時設置如下所示:

當然原理與定時時設置相同,只是十位為6進制,個位為10進制,到59翻0。鬧鐘部分時,將小時顯示計數器、分鐘顯示計數器的8個輸出端,鬧鐘時設置、鬧鐘分設置的8個輸出端引出,用4個4077門進行比較,然后將4個4077門的8個輸出端用2個7421進行與運算,將2個7421的輸入輸出端用3個與門進行與運算后輸出到鬧鐘發聲器。就完成了鬧鐘功能。當與時間顯示計數器相連的顯示器與與時間設置計數器相連的顯示器顯示的數字相同時,即相達鬧鐘條件,這時4個4077門的所有輸入端都為1,經過二次與運算后輸入到發聲器的信號也為1,即鬧鐘開始,否則輸入到發聲器的信號為0,鬧鐘不響。鬧鐘會一直響,直到兩個地方的時間不一樣為止,也就是響一分鐘。具體電路請看總電路。

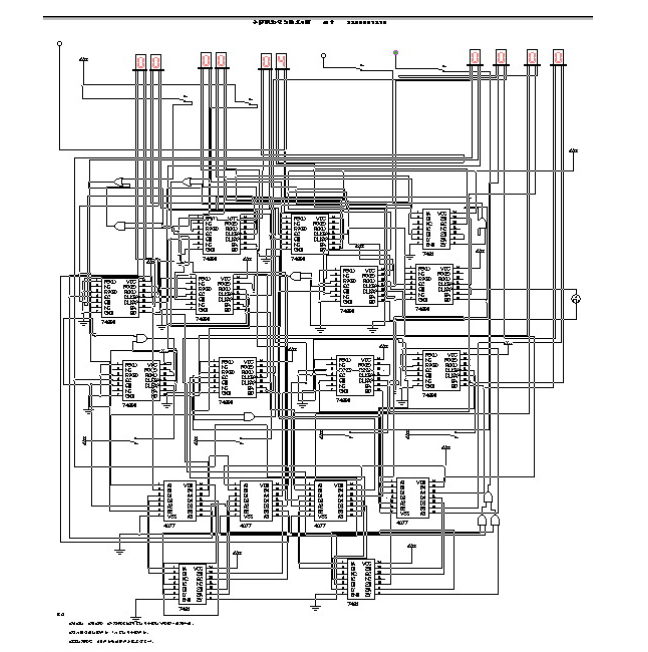

6.總電路圖:

效果分析:分按下測試按鈕開關后,時間顯示部分從00:00:00開始計數,每一秒秒鐘顯示加一,每60秒分鐘顯示加一,每60分時鐘顯示加一,每時鐘到達23時下一個態為0。鬧鐘設置顯示部分開始為00:00:00,按“1”時,時的十位加一,加到23時下一個態為0;按“2”時,時的個位加一,加到9時下一個態為0;按“3”時,分的十位加一,加到5時下一個態為0;按“4”時,分的個位加一,加到9時下一個態為0;按“S”打開和關閉整點報時功能,當整點時,整點報時信號燈亮一下。按“T”打開和關閉鬧鐘功能,當實際時間達到鬧鐘設置時間時,鬧鐘信號燈亮,一分鐘后熄滅;按“A”時間顯示部分的時加一,按“B”時間示示的分加一,如些循環可以把時間調整為準確時間。多次測試說明,本次設計的電路完全符合設計要求。

-

計數器

+關注

關注

32文章

2259瀏覽量

94825 -

時鐘

+關注

關注

11文章

1742瀏覽量

131647 -

顯示電路

+關注

關注

6文章

97瀏覽量

33237

發布評論請先 登錄

相關推薦

數字地和模擬地如何處理

ISO7841標準數字隔離器在現代電子系統中的作用

數字電子設計的多功能數字鐘實現方案

數字電子設計的多功能數字鐘實現方案

評論