作者:Olivier Tremois(AI 引擎工具市場營銷部門)和 Florent Werbrouck(賽靈思技術支持產品應用工程師)

Versal ACAP 簡介

Versal 自適應計算加速平臺 (ACAP) 是基于 TSMC 7nm FinFET 工藝技術構建的最新一代賽靈思器件。它利用高帶寬片上網絡 (NoC) 將代表處理器系統 (PS) 的標量引擎、代表可編程邏輯 (PL) 的自適應引擎與智能引擎有機結合在一起。

本文將著重介紹智能引擎中所包含的 AI 引擎。

賽靈思 AI 引擎簡介

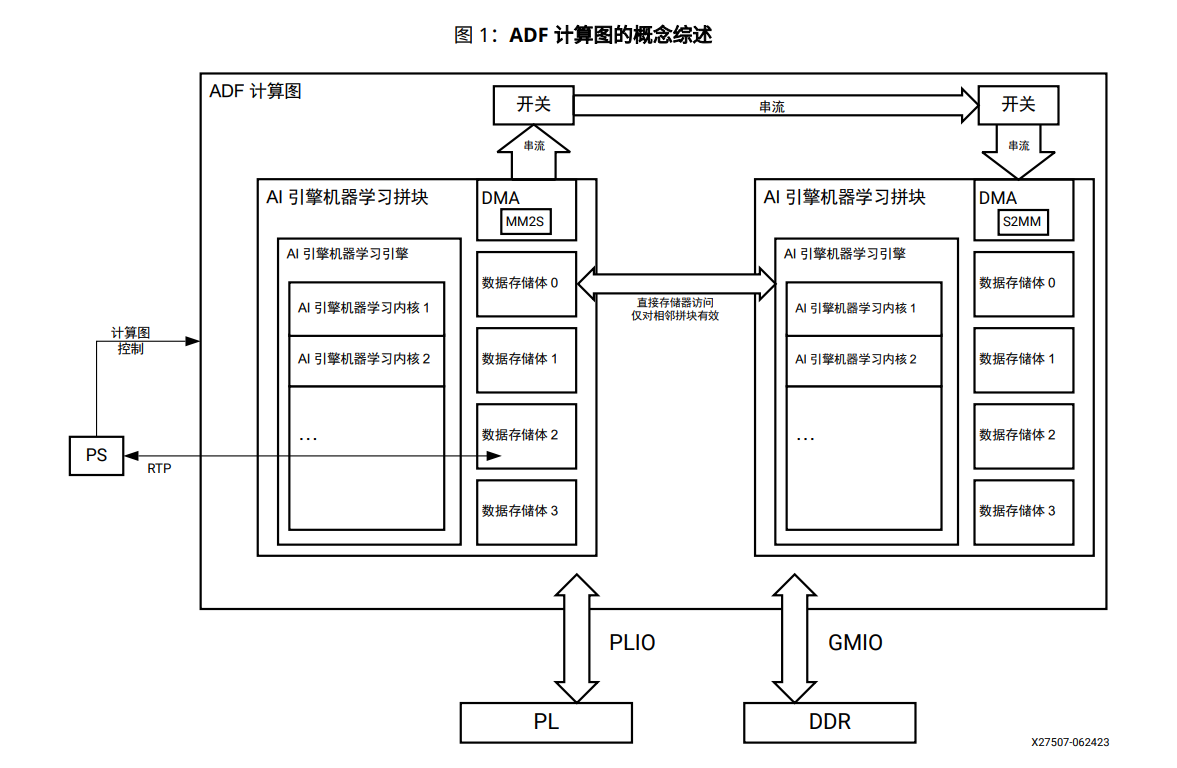

在部分賽靈思 Versal ACAP 中包含了 AI 引擎。這些 AI 引擎可排列組合為一組與內存、數據流和級聯接口相連的二維AI 引擎拼塊陣列。在當前 ACAP 器件(例如,VC1902 器件)上,此陣列最多可包含 400 個拼塊。此陣列中還包含AI 引擎接口(位于最后一行),以便于陣列中的其它器件(PS、PL 和 NoC)進行交互。

AI 引擎接口包含PL 和 NoC 接口拼塊以及配置拼塊。從 PL 到 AI 引擎陣列的連接是使用 AXI4-Stream 接口通過 PL 和 NoC 接口拼塊來實現的。從 NoC 到 AI 引擎陣列的連接是使用 AXI4 存儲器映射接口通過 NoC 接口拼塊來實現的。

有趣的是,從中可以看到,只有在 NoC 到 AI 引擎拼塊之間才存在 AXI4 存儲器映射直接通信通道,在 AI 引擎拼塊到 NoC 之間卻并不存在。

注:PL 和 NoC 接口拼塊的精確數量因器件而異。《Versal 架構和產品數據手冊:簡介》(DS950) 中羅列了 AI 引擎陣列的大小。

https://china.xilinx.com/support/documentation/data_sheets/ds950-versal-...

AI 引擎拼塊架構

現在,我們來詳細了解下此陣列,看看 AI 引擎拼塊的內部。

每個 AI 引擎拼塊都包含:

- 1 個拼塊互連模塊,用于處理 AXI4-Stream 和存儲器映射 AXI4 輸入/輸出

- 1 個存儲器模塊,其中包含 32 KB 數據內存,細分為 8 個內存 bank、1 個內存接口、DMA 和各種鎖定。

- 1 個 AI 引擎

AI 引擎可訪問全部 4 個方向中的多達 4 個內存模塊(作為 1 個連續存儲器塊)。這意味著除了拼塊本地的內存,AI 引擎還可以訪問 3 個相鄰拼塊的本地內存(除非拼塊位于陣列邊緣)。

- 北側內存模塊

- 南側內存模塊

- 東側或西側內存模塊(取決于 AI 引擎和內存模塊所在的行和相對布局)。

AI 引擎架構

AI 引擎屬于高度優化的處理器,包含下列主要特色:

- 32 位標量 RISC 處理器(名為 Scalar Unit)

- 1 個 512b SIMD 矢量單元(可提供矢量定點/整數單元)和 1 個單精度浮點 (SPFP) 矢量單元

- 3 個地址生成器單元 (AGU)

- 超長指令字 (VLIW) 功能

- 3 個數據內存端口(2 個負載端口,1 個存儲端口)

- 直接流傳輸接口(2 個輸入流,2 個輸出流)

AI 引擎陣列編程

AI 引擎拼塊按 10 或 100 為單位組成陣列。創建嵌入多項指令的單一程序用于指定并行性將是一項冗長且近乎不可能的任務。因此 AI 引擎陣列模型編程與 Kahn 處理網絡 (Kahn Process Networks) 之間的共通之處在于自主計算進程通過通信邊緣實現彼此互連,從而生成處理網絡。

(請參閱 https://perso.ensta-paris.fr/~chapoutot/various/kahn_networks.pdf )

在 AI 引擎框架中,Graph 邊緣是緩存和數據流,而計算進程則被稱為內核。在Graph中,內核經過例化,彼此相連并連接到設計其余部分(NoC 或 PL)。

編程流程分為 2 個階段:

單內核編程:

內核用于描述特定計算進程。每個內核都將在單一 AI 引擎拼塊上運行。但請注意,多個內核可在同一個 AI 引擎拼塊上運行,并共享處理時間。任意 C/C++ 代碼均可用于對 AI 引擎進行編程。標量處理器將處理大部分代碼。如果您的目標是設計高性能內核,那么應考慮采用矢量處理器,它使用稱為內部函數的專用函數。這些函數專用于 AI 引擎的矢量處理器,支持您從 AI 引擎中發掘出巨大的處理性能。賽靈思將提供預構建內核(包含在庫內),以供用戶在其定制 Graph 中使用。

Graph 編程:

賽靈思將提供 C++ 框架以從內核創建Graph。此框架包含 Graph 節點和連接聲明。這些節點可包含在 AI 引擎陣列內或可編程邏輯(HLS 內核)中。為了完全掌握內核位置,將有一系列方法可用來約束布局(內核、緩存、系統內存等)。Graph 將例化并使用緩存和數據流將內核連接在一起。它還將描述 AI 引擎陣列與其它ACAP 器件(PL 或 DDR)之間的雙向往來數據傳輸。

賽靈思將提供預構建 Graph(包含在庫內),以供用戶在其應用中使用。

在運行時以及仿真期間,AI 引擎應用由 PS 進行控制。

編輯:hfy

-

賽靈思

+關注

關注

33文章

1796瀏覽量

132138 -

AI

+關注

關注

88文章

34342瀏覽量

275532 -

可編程邏輯

+關注

關注

7文章

524瀏覽量

44588

發布評論請先 登錄

涂鴉智能重磅發布四大AIoT技術引擎,賦能開發者以AI重構物理世界

移遠通信攜手火山引擎:加速AI大模型技術應用,共繪AIoT智能未來新藍圖

融合30萬項專利,“OptoChat AI”引擎引爆萬億光子AI市場

評論