PYNQ-PRIO是一個(gè)介紹如何利用FPGA部分可重配置特性和PYNQ框架提供的方便的API,對(duì)FPGA分時(shí)復(fù)用,提高FPGA靈活性的項(xiàng)目。可重配置是指在一個(gè)FPGA工程中,劃分了靜態(tài)邏輯部分和動(dòng)態(tài)邏輯部分,靜態(tài)邏輯部分是指在運(yùn)行過程中邏輯不變的部分,動(dòng)態(tài)邏輯部分是指在運(yùn)行過程中可以根據(jù)需要下載特定比特流文件實(shí)現(xiàn)不同邏輯的部分,在工作時(shí),修改某一動(dòng)態(tài)邏輯部分不會(huì)對(duì)靜態(tài)邏輯部分和其他動(dòng)態(tài)邏輯部分造成影響,實(shí)現(xiàn)了FPGA的功能上的分時(shí)復(fù)用。

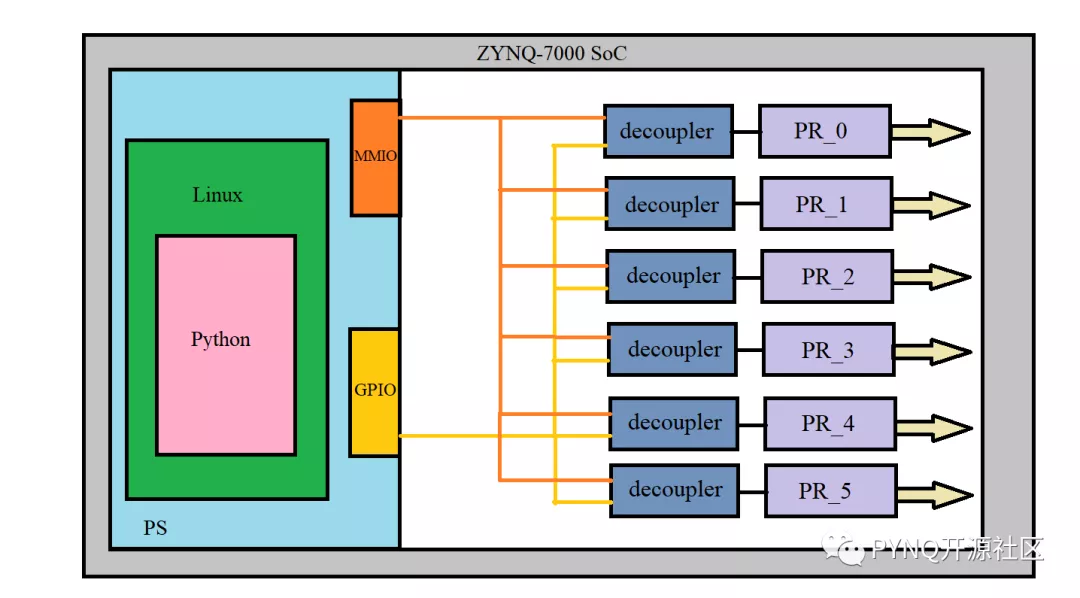

上圖為工程項(xiàng)目示意圖。通過軟硬件劃分,在PS端中負(fù)責(zé)Linux和通信,PL端例化了6個(gè)PR(Partitial Reconfiguration)塊。每個(gè)塊中有GPIO、uart和IIC等幾種不同的RM(Reconfiguration Module),它們通過各自的partitial bitstream下載。動(dòng)態(tài)邏輯部分和靜態(tài)邏輯部分使用分離器保證它們互不影響,并在動(dòng)態(tài)邏輯部分下載完成后對(duì)下載好的部分進(jìn)行復(fù)位。

此項(xiàng)目中在PYNQ框架下有兩種驅(qū)動(dòng)這些IP的方式:一是直接使用PYNQ提供的API操作overlay里面的IP,二是將這些IP通過DTS(Device Tress Source)注冊(cè)到linux sysfs中,然后調(diào)用linux提供的驅(qū)動(dòng)。

快速開始

運(yùn)行下面這條命令即可快速安裝:

sudo -H pip3 install git+https://github.com/Siudya/PYNQ-PRIO.git

項(xiàng)目演示

1 、 使用pynq API的方法:

打開~/prio/uart.ipynb,前面一段代碼是UART的驅(qū)動(dòng)程序和必要的功能代碼,不是本文重點(diǎn)請(qǐng)讀者自己研讀。

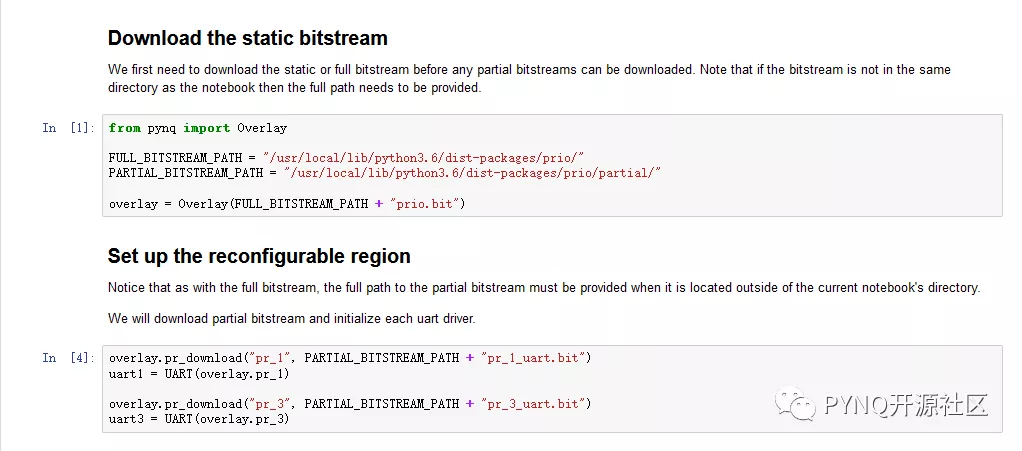

接下來就是下載bit文件。首先下載靜態(tài)邏輯bit文件,靜態(tài)bit文件中的PR部分是默認(rèn)的RM。然后下載PR的bit文件。注意,下載一個(gè)PR的bit文件后要立刻例化一個(gè)驅(qū)動(dòng)實(shí)例,這是因?yàn)槊總€(gè)PR的bit文件所對(duì)應(yīng)的hwh文件中其他PR部分都使用默認(rèn)RM,但是下載一個(gè)PR的bit文件并不會(huì)影響其他PR和靜態(tài)邏輯。

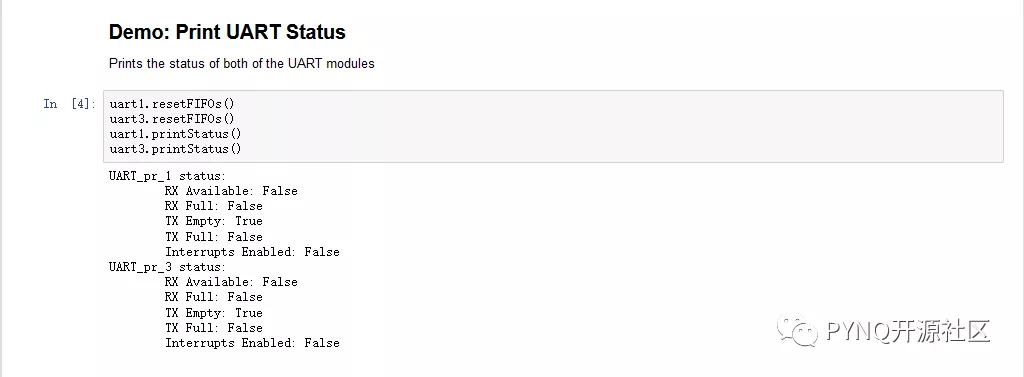

然后可以測(cè)試一下兩個(gè)UART的狀態(tài),在這里我們并沒有開啟中斷。

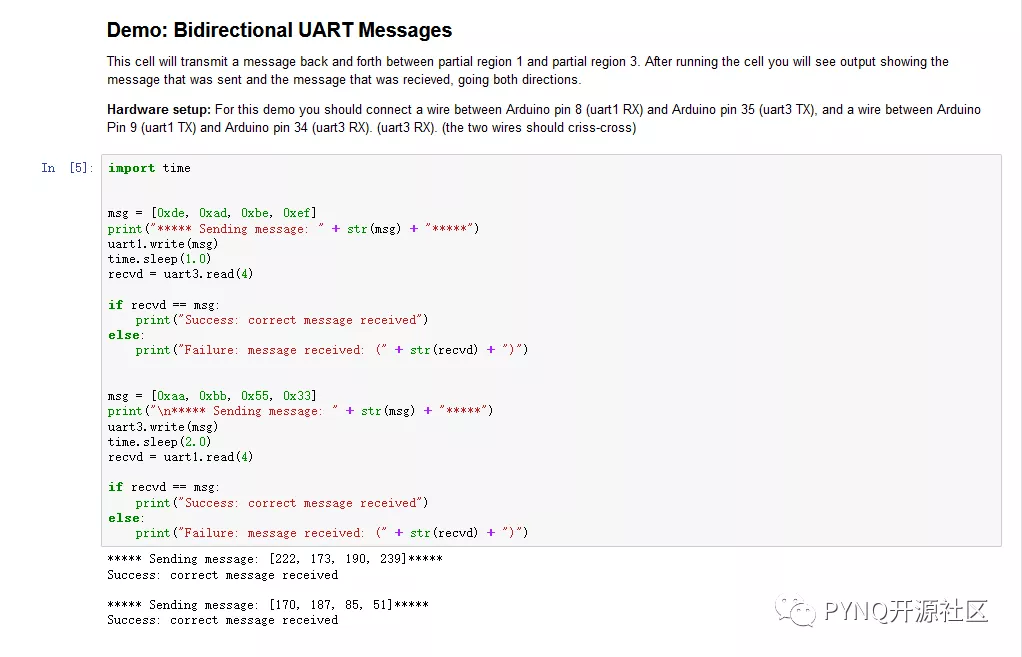

下一步我們測(cè)試兩個(gè)串口的收發(fā)。用杜邦線將uart1的TX(Arduino的Pin 9)和uart3的RX(Arduino的Pin 34),uart1的RX(Arduino的Pin 8)和uart3的TX(Arduino的Pin 35)連接起來,運(yùn)行這段代碼,可以看到信息被正確地收發(fā)了。

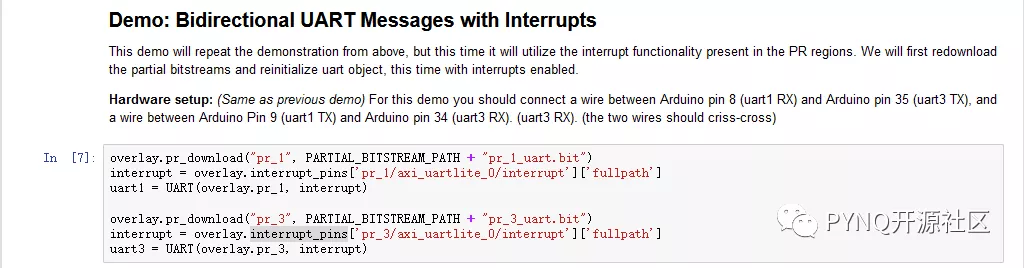

接下來我們?cè)囋嚭袛嗟氖瞻l(fā)。首先仍然是例化實(shí)例,不過在這里我們要從overlay.interrupts_pins中讀取每個(gè)uart的中斷引腳,然后初始化uart實(shí)例。

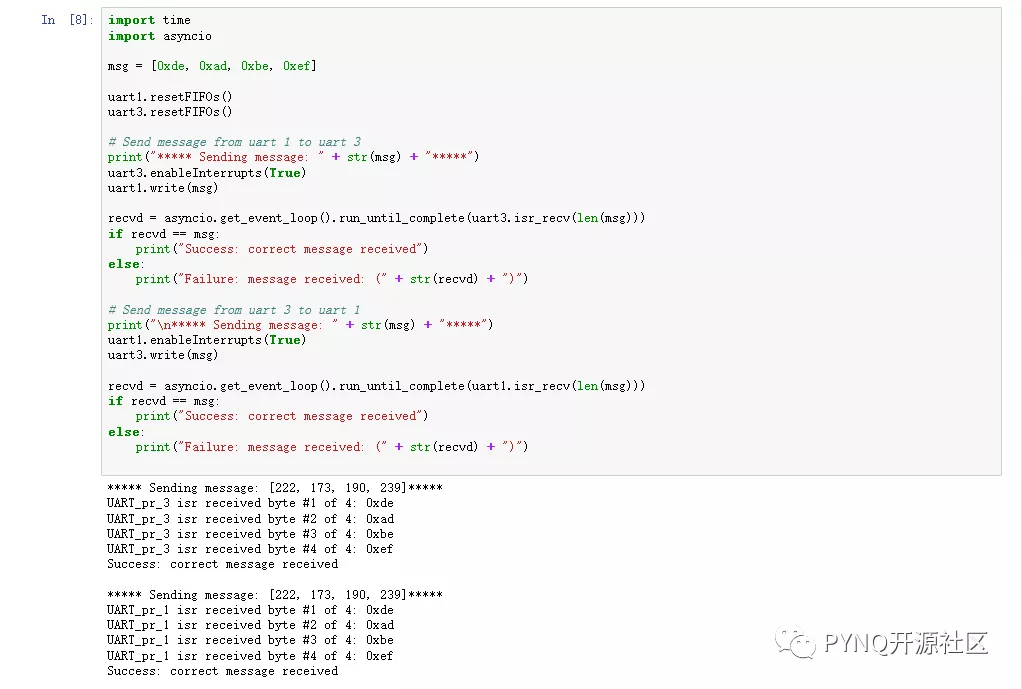

利用asyncio庫(kù)和中斷,我們可以實(shí)現(xiàn)異步收發(fā)。

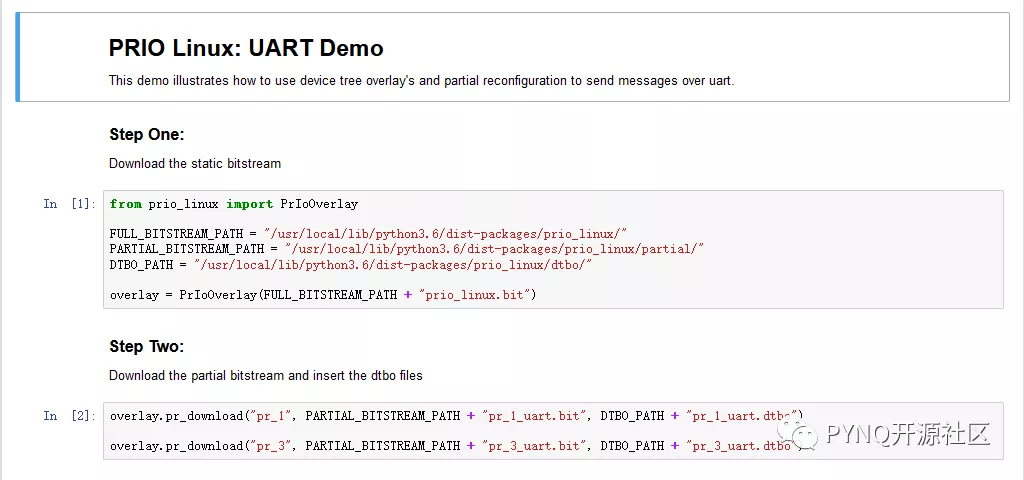

2 、使用linux sysfs API的方法:

打開~/prio_linux/uart_linux.pynb

首先和上面使用pynq的API的方法一樣,首先下載靜態(tài)邏輯的bit文件,再下載PR的bit文件。但是不同的是同時(shí)注冊(cè)了對(duì)應(yīng)的dtbo到linux系統(tǒng)中。dtbo由dtso編譯而來,dtso是描述設(shè)備樹的文件,關(guān)于它的編寫參閱以下鏈接:

https://www.raspberrypi.org/documentation/configuration/device-tree.md

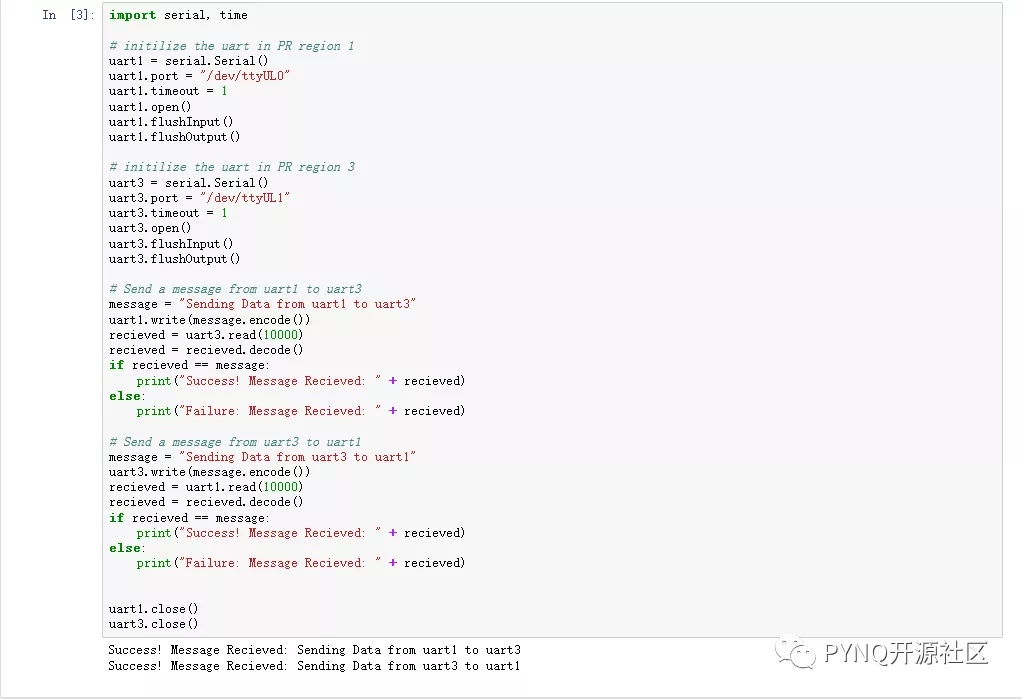

注冊(cè)完成后可以直接在/dev下看到這兩個(gè)uart模塊。然后可以使用linux自帶的serial庫(kù)調(diào)用它們。

這個(gè)項(xiàng)目中我們利用了FPGA的部分可重構(gòu)的特性,實(shí)現(xiàn)了運(yùn)行中的部分邏輯的動(dòng)態(tài)轉(zhuǎn)換。另外我們可以看到利用PYNQ提供的API,可以輕松注冊(cè)設(shè)備到Linux系統(tǒng),方便了其他程序?qū)ξ覀冏远xIP的使用。

編輯:hfy

-

FPGA

+關(guān)注

關(guān)注

1629文章

21758瀏覽量

604242 -

Linux

+關(guān)注

關(guān)注

87文章

11320瀏覽量

209835 -

uart

+關(guān)注

關(guān)注

22文章

1240瀏覽量

101489

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

利用FPGA實(shí)現(xiàn)USB 2.0通信接口

一種簡(jiǎn)單高效配置FPGA的方法

FPGA在圖像處理領(lǐng)域的優(yōu)勢(shì)有哪些?

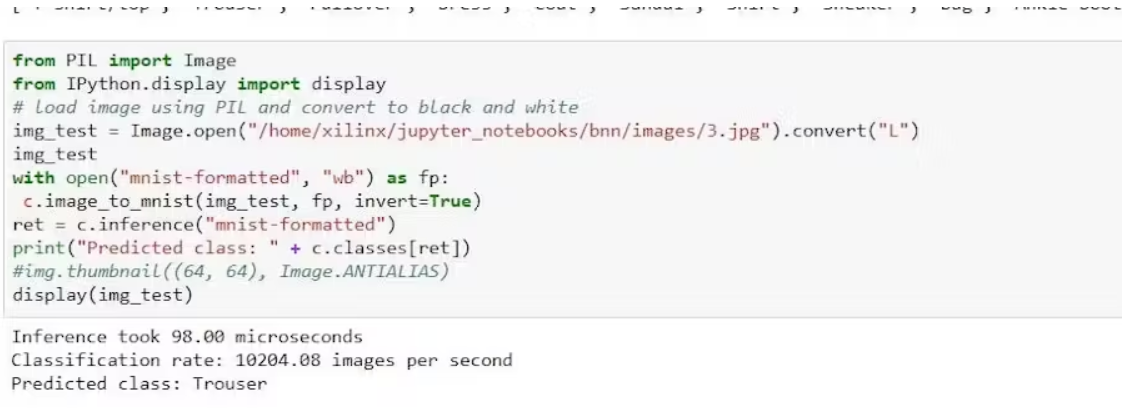

使用PYNQ訓(xùn)練和實(shí)現(xiàn)BNN

基于PYNQ的智能垃圾分類系統(tǒng)

基于FPGA的攝像頭心率檢測(cè)裝置設(shè)計(jì)

基于FPGA的類腦計(jì)算平臺(tái) —PYNQ 集群的無監(jiān)督圖像識(shí)別類腦計(jì)算系統(tǒng)

如何利用經(jīng)典藍(lán)牙的bt_spp_acceptor實(shí)現(xiàn)藍(lán)牙透?jìng)鞴δ埽?/a>

簡(jiǎn)談Xilinx Zynq-7000嵌入式系統(tǒng)設(shè)計(jì)與實(shí)現(xiàn)

FPGA開發(fā)如何降低成本,比如利用免費(fèi)的IP內(nèi)核

基于FPGA的光纖通信加密系統(tǒng)

如何利用FPGA部分可重配置特性實(shí)現(xiàn)PYNQ-PRIO經(jīng)典案例

如何利用FPGA部分可重配置特性實(shí)現(xiàn)PYNQ-PRIO經(jīng)典案例

評(píng)論