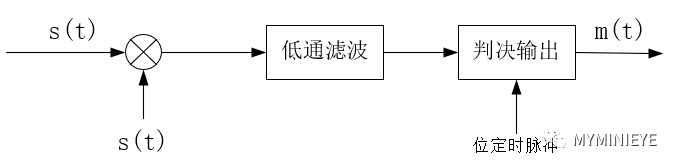

ASK相干解調原理

由圖可知,輸入信號和相干載波在乘法器中相乘,然后由低通濾波濾除所需要的基帶波形,然后通過判決輸出解調后的基帶數據,判斷輸出需要位定時脈沖(位同步脈沖)。

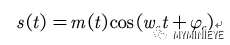

假設輸入信號為:

相干載波為:

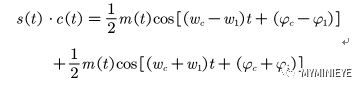

乘法器的輸出為:

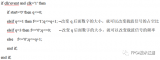

濾除高頻成分,相干條件滿足,即,則相干檢測器的輸出為:

其中Kc為低通濾波器增益,采用相干解調時,接收端需要提供一個與ASK信號載波同頻同相的相干載波,否則會造成解調后波形的失真。相干載波的提取會極大的增加設備復雜性,實際中多采用更加簡單的包絡檢波來實現ASK信號的解調。

(2)非相干解調

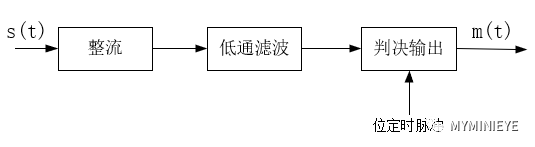

包絡檢波不需要提取相干載波,因此是一種非相干解調法,包絡檢波原理如下:

ASK非相干解調原理

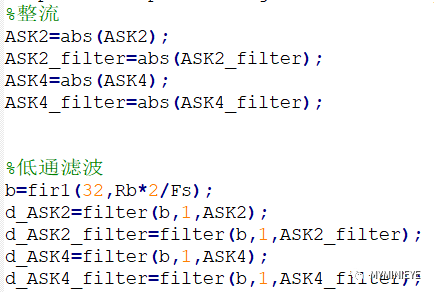

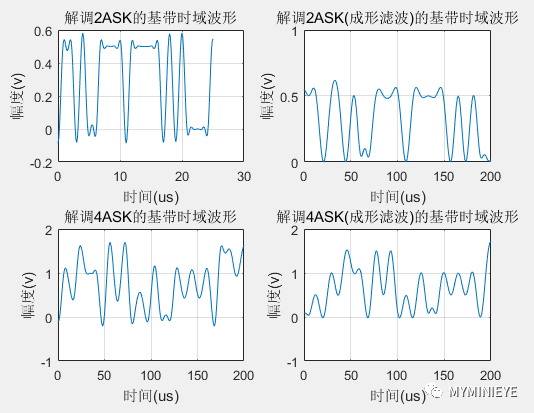

相干解調需要提供與輸入同頻同相的載波信號,通常需要采用鎖相環技術實現載波信號的提取,較為復雜,這里采用非相干解調的方法實現ASK解調,只需要將輸入信號經過整流濾波即可得到基帶信號。

matlab主要代碼如下:

3.ASK解調技術的FPGA實現

完整的ASK解調電路包括基帶解調及位同步時鐘的提取,對于數字解調系統來講,我們需要在接收端獲得與發送端相同的數據信息,最終輸出的結果是數據流,以及與數據流同步的位同步時鐘信號。

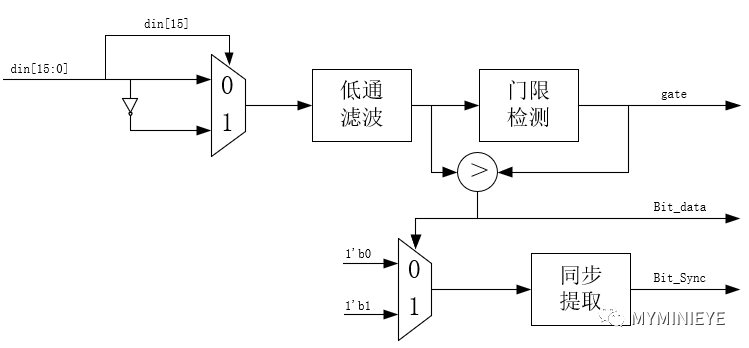

ASK的解調可以分為基帶波形的獲取,判決門限獲取,位同步時鐘提取三個模塊,在FPGA中的設計如下:

濾波和門限檢測相對簡單,這里主要介紹位同步時鐘的提取。

3.1位同步時鐘介紹

位同步也稱定時同步、符號同步、碼元同步,是數字系統特有的一種同步。

(1)如果基帶信號中已含有顯著的時鐘頻率(或時鐘導頻分量),可以使用窄帶濾波或者鎖相環提取,這種方法稱為插入導頻法。

(2)當傳輸隨機比特流信號中不含有離散的時鐘頻率及諧波時,同步信息包含在基帶數據初始相位中。不能直接提取,一般有兩種方法,非線性變換濾波和特殊鑒相器的鎖相法。

(3)基于Gardner的位定時同步算法,采用產值濾波的原理來實現位定時同步及最佳抽樣判決。

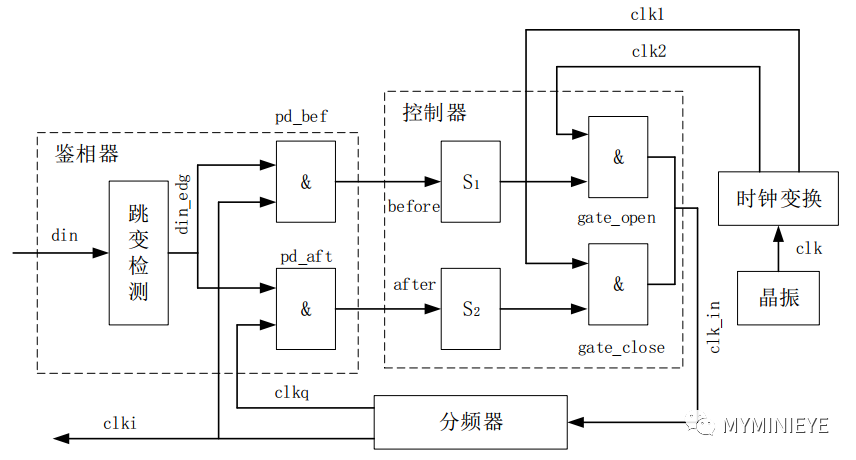

這里使用鎖相位同步法來實現同步時鐘的提取,但是這種方法只是用二進制單bit調制信號,對于多bit信號,通過簡單的門限判決無法獲得由碼元00跳變到11的初始相位,對于二進制來言。0和1之間不存在其他的碼元,數據判決只有一個門限,多進制的位同步技術可以使用Gardner算法來實現。數字鎖相位同步環的原理如下:

如上圖所示,數字鎖相位同步環主要由鑒相器、控制器、分頻及時鐘變換電路組成。輸入信號din是單bit信號,跳變檢測用于檢測輸入信號的跳變沿,當檢測到一個跳變沿的時候產生一個時鐘周期的高電平信號,提取出位同步信息,用于檢測同步信息的時鐘與時鐘變換電路的輸入時鐘信號是否相同。仿真結果如下:

當同步時鐘滯后輸入的時候,會產生一個滯后脈沖(pd_aft),然后滯后門 (pd_after) 打開,可以看到在1中gate_close門會打開,clk_in會多加一個脈沖,使得下一個時鐘提前1個調整周期。這里數據采樣速率為碼元的8倍,每次相位調整步進為一個數據采樣周期,相當于1/8個碼元周期。當同步時鐘超前輸入數據的時候會產生一個超前脈沖(pd_bef),然后超前門(pd_before)打開,clk_in會扣除一個脈沖,使得下一個時鐘滯后一個調整周期。無論加還是減脈沖,相位校正總是階躍式的,穩態相位不會為零,而是圍繞零點左右擺動。

3.2仿真結果

通過上述的分析和設計,得到最終的仿真結果,其中data為調制的二進制bit信號,abs_din是整流輸出,din為濾波器的輸出,mean為判決門限,decode_data為判決輸出,從下圖中可以看出解調后的數據decode_data能夠與輸入的2ASK信號對應,但是最后同步輸出bit_data與調制的數據對應不上。

4.總結分析

4.1 從波形上看判決輸出基本與輸入一致,最終同步的數據不對,首先定位到位同步時鐘的提取,重新梳理了位同步的原理,以及時序波形,發現了一個問題,如下所示:

過門限檢測之后的數據高低電平長短不一,位同步時鐘存在漏檢和誤檢的情況,在連0和連1出現次數較多的情況下尤為嚴重。于是我把過門限檢測之后的數據經過D出發器處理成等長度的二進制數據,并更換調制信號為1和0交替的信號。

可以看到,結果是正確的,把解調后的數據和調制數據對比也是正確的。在連1不是很多的情況下,依然能夠正確解調出正確數據,如下所示:

256點門限長度

4.2猜測可能和門限檢測的長度有關系,即對濾波之后的調制信號求平均的點數。因此改變門限檢測長度,測試了32,64,128,256點的門限長度,可以發現門限的平滑度不同,但是結果都是正確的。

32點門限長度

4.3最后我把數據改成最初的調制數據,得到結果如下:

通過matlab比對數據,發現只有前5個數據不一樣,可能是由于一開始沒有足夠的數據點數計算正確的判決門限,導致初始的解調數據是錯誤的,后續數據比對完全一致。

最終確定原因,數據比對不上是由于過門限檢測之后的數據高低電平長短不一導致的,下圖是我在仿真中找到的一個比較明顯的地方,decode_data為1010101,但是同步輸出全為1。

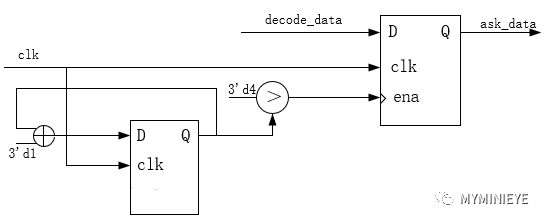

過門限檢測之后的數據不能直接給位同步時鐘提取模塊,需要做以下調整才能得到正確的解調。為什么選取4作為計數器判別,采樣頻率為碼元速率的8倍,一個碼元采樣8個點,首先同步decode_data脈沖邊沿,計數器從0~8,在門限檢測的時候,認為超過4個點為1,結果為1,超過4個點為0,結果就為0。

-

FPGA

+關注

關注

1629文章

21729瀏覽量

603002 -

無線通信

+關注

關注

58文章

4564瀏覽量

143496 -

波形

+關注

關注

3文章

379瀏覽量

31544 -

ASK

+關注

關注

2文章

75瀏覽量

45308 -

時鐘信號

+關注

關注

4文章

448瀏覽量

28542

發布評論請先 登錄

相關推薦

供應SW5106無線充電發射端全集成SOC芯片

如何提升調制解調器的信號強度

調制解調器的工作原理 如何選擇調制解調器

智融SW5106 無線充電發射端全集成 SOC

光纖光柵傳感中的解調技術有哪些

數字信號轉模擬信號是調制還是解調

基于FPGA VHDL的ASK調制與解調

什么是解調?AM波、FM波的解調原理

線性解調電路設計圖解析

ASK信號的解調原理 ASK解調技術的FPGA實現

ASK信號的解調原理 ASK解調技術的FPGA實現

評論