1. 初識XILINX

初識XILINX,是PYNQ-Z2。當時剛學完學校的數字電路課程,對FPGA并不了解,學校課程也僅僅是用VHDL驗證了一些基礎的FPGA實驗,例如生成一個n進位序列碼。并不知道FPGA有這么廣闊的應用。在一次王偉博士的培訓上,我第一次接觸到了PYNQ。在講座中,我運行了一個PYNQ的demo。通過USB攝像頭檢測邊緣處理。如下圖:

當時給了我很大的震撼,瞬間對FPGA非常感興趣。王博士指點我,想學好FPGA,光會一點VHDL的皮毛并不夠,要對工業上最流行的VERILOG非常熟悉才行。雖然我們學校并沒有開設關于VERILOG的課程,但我在圖書館借閱了相關的書籍首先進行自學,并在實際操作中補充自己。這一步也為之后全國FPGA大賽的個人能力測試建立了基礎。隨后,王博士開展面向全系的VERILOG普及培訓,我非常有幸作為助教參與其中,給低年級學弟學妹開展VERILOG基礎語法的講解。

隨后,XILINX公司推出ULTRA96板卡的試用申請。這對我來說既是機遇,也是挑戰。不負一番努力,我通過了板卡的申請。收到板卡后,困難一直伴隨著我。因為對LINUX系統并不熟悉,第一次讓設備連接網絡就花費了我很長時間。當時網上并沒有現在對它的明確資料,靠著類似的設備樹莓派的經驗去一步步試著去配置,最后總結出多種聯網方法并和實驗室同學分享。在此期間,我意識到要學好嵌入式技術,必須對LINUX做到很熟悉。

2. 參加FPGA大賽

完成基礎的培訓后,我報名參加了2019年的FPGA全國大學生競賽。我們的項目是制作一臺基于STM32平臺的智能小車,可以通過車載攝像頭設識別障礙和到路線。利用ULTRA96強大的計算性能,運行裁剪過的YOLO/SSD模型。實現識別的速度和精度的雙向贏。期間,訓練模型對我來說在初期也是一個很大的挑戰,從第一次接觸Tensorflow到訓練模型,遇到很多的問題也得到了很多老師同學的幫助。

解決重重問題后,我完成了我們比賽的所有準備,來到南京答辯。因為板卡屬于自選題目組,所以在比賽的房間內都是來自一些名校的研究生組合,無形中給了我很大壓力。在評委組驗收的時候,暴露出識別幀數低下的問題,評委也給出一些解決的建議。不負眾望,最終我取得了不錯的二等獎,對我來說也是非常的不容易。其實,得到評委的肯定的評價比得知獲獎更為開心。

我比賽中的作品

3. 假期DNNDK SSD

在假期中,尋找到了當時大賽時對障礙物識別幀數低的原因,通過對設備的調整,實現SSD模型15-20幀的識別速度。如下圖。

4. 參加XDF

因為對XILINX非常感興趣,我自費報名參加了XILINX的2019年XDF全球開發者大會。參加本次大會讓我受到了很多啟發。我們向XILINX工程師詢問了ULTRA96無法發揮完全性能可能的原因并進行了探討,對之后解決這個問題有了非常大的幫助。

在XDF的現場實驗室,我們通過做官方VITIS例程,體會到了XILINX新一代集成工具VITIS的強大整合能力。因為大賽的原因,我對小車的相關技術非常感興趣。在AVANT的展臺上,

我發現了了AVANT的工程師用ULTRA96作為ROS(Robot Operating System)作為載體運行激光雷達的運行。

5. SLAM實時建模

這給我非常大的啟發,依托ROS強大的外設庫支持、仿真能力和FPGA強大的運算性能,可以實現更高性能的機器人底盤系統。下圖是我利用ROS對REALSENSE多攝像頭傳感器的仿真,實現SLAM實時建模我房間的一角。

6. PETALINUX鏡像

最近,認識到要真正用好ZYNQ,必須掌握PETALINUX去定制所需要的系統。在這個過程中遇到了很多問題。或許是計算機編譯的速度慢、或許是資源需要連接外網導致網速很慢,最終讓整個編譯過程無限變長。為了解決這些問題,付出了很多時間作為代價。連續2周的連續從早到晚的編譯,因為我的操作不當,沒有把計算機放在通風良好的地方。計算機的主板南橋因為長時間過熱燒毀了,不過一切苦難克服之后都是值得的。通過大量的嘗試,不斷的成功和失敗。讓我越來越清楚PETALLINUX的運行規則。最后,實現帶有DPU功能的定制鏡像的制作,如下圖:

圖像處理流程:

1.讀取圖像

2.將讀取的圖像數據格式轉換為AXI格式

3.將AXI格式的圖像轉換為OPENCV可以處理的Mat格式

4.通過HLS_OPENCV處理庫對圖像進行處理

5.將處理完的圖像數據從Mat格式轉換為傳輸的AXI格式

6.將圖像的AXI轉換為圖像格式

7.將圖像進行輸出

用到的HLS_OPENCV函數詳細參考官方指南UG902

展示一個簡單的圖像處理結果:

8. VIVADO VITIS ULTRASCALE+MPSOC IP FPGA設計

VIVADO是FPGA設計最基礎的一環。它是一個功能強大的集成開發環境,包含了綜合和實現的環境。VIVADO可以實現自動管理運行數據,并可以方法運行。可以對多種硬件描述語言進行綜合。VIVADO的出現,提高了我們對FPGA的設計效率,簡化了設計流程。

VIVADO項目設計流程:

1. 加入對應板卡信息

2. 打開VIVADO并新建工程

3. 選擇板卡并完成建立

4. Create Block Design

5. 添加PS、Pl核心及組件接口并連線

6. Create HDL Wrapper

7. 綜合并生存比特流

8. 輸出硬件描述文件

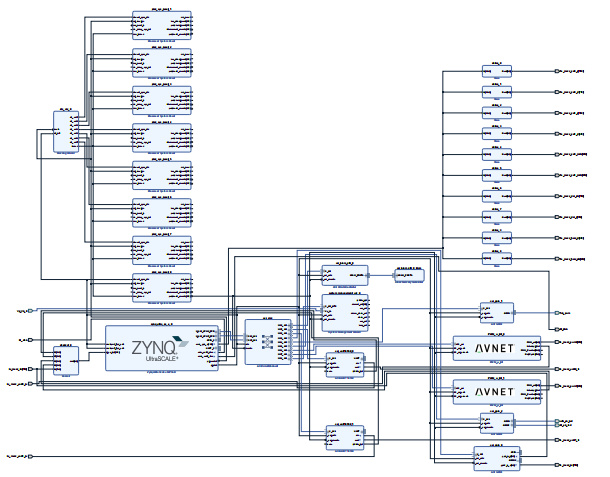

如下圖是Ultra96的板卡設計圖

VITIS是XILINX公司最新推出的統一軟件平臺,它可以為邊遠、云和混合計算應用加速提供統一編程模型。利用與高層次框架的結合和完整的加速庫,可以加快我們的設計效率。

下面是利用VITIS實現的一個終端FPGA串口輸出的仿真

VITIS流程:

1. 創建平臺項目

2. 輸入硬件描述文件并完成創建

3. 修改我們要用到的串口

4. 保存并重新BULID

5. 創建一個應用項目

6. 選擇一個串口輸出模板并修改主函數

7. 保存并重建項目

8. 通過硬件仿真

下面分別為設備平臺和仿真結果:

-

FPGA

+關注

關注

1646文章

22097瀏覽量

620730 -

賽靈思

+關注

關注

33文章

1797瀏覽量

132586 -

激光雷達

+關注

關注

973文章

4257瀏覽量

193372

發布評論請先 登錄

FPGA利用DMA IP核實現ADC數據采集

如何在Unified IDE中創建視覺庫HLS組件

使用AMD Vitis Unified IDE創建HLS組件

如何使用AMD Vitis HLS創建HLS IP

FPGA圖像處理基礎----實現緩存卷積窗口

使用IP核和開源庫減少FPGA設計周期

使用HLS流程設計和驗證圖像信號處理設備

FPGA 實時信號處理應用 FPGA在圖像處理中的優勢

芯驛電子 ALINX 推出全新 IP 核產品線,覆蓋 TCP/UDP/NVMe AXI IP 核

評論