GMII、SGMII和SerDes的區別和聯系?

GMII和SGMII區別,上一篇已經介紹了,這一篇重點介紹SGMII和SerDes區別。

GMII和SGMII

SGMII和SerDes

終于到了今天的豬腳-SerDes,為什么拿SGMII和SerDes進行對比,主要原因是,SerDes是一個串行接口,和SGMII很像,和GMII幾乎沒有什么交集,所以兩者對比就沒有什么實際意義,所以只進行SGMII和SerDes進行對比。

由于SerDes在PCIe部分起著非常重要的作用,所以這部分詳細內容會放到PCI-e部分詳解,這里只是簡單介紹一下:

SerDes,是SERializer(串行器)和DESerializer(解串器)的簡稱,是一種點對點的高速串行通信技術,串口協議跟IIC、SPI等總線協議還是有很大差別的,最大的特點就是點對點收發、沒有隨路時鐘,它的速率是隱含在協議里的,雙方必須按照約定好的波特率進行數據的發送和接受才能正確的完成通信,SPI則是主機向從機發送時鐘,從機在這個時鐘的上升沿采樣數據、下降沿發送數據,最開始人們為了提高通信速率的思路有兩條:提高隨路時鐘頻率、增加數據通路位寬,這都很好理解,舉個栗子就是四線SPI(Qspi),但逐漸地這種思路就遇到瓶頸!

第一、時鐘頻率的不斷增加,時鐘抖動和偏斜的因素變得更加明顯,也增加了時鐘質量的要求,為了充分利用時鐘,工程師們還想到了利用下降沿,沒錯,就是DDR!第二、數據總線的增加意味著管腳數的增加,這會引起PCB布局布線的災難。人們又開始把思路回到不用時鐘線的串口協議上。先看看串口收發器的偽代碼!

//串口收發器 SerialTransceiver

module serialTR(

input sys_clk,

input rst_n,

//可配置單雙工,雙工模式

input [1:0] I_rxtx_en, //收發使能,高有效

output [1:0] O_rxtx_done, //收發完成脈沖信號

input RX, //串口總線

output TX,

//數據位寬可配置

input [7:0] data2tx, //待發送數據

output [7:0] data2rx //待接收數據

);

//串口接收 ---> 串轉并

always@()begin

if(!rst_n)

//寄存器復位

else if(I_rxtx_en[1])

//1、下降沿檢測,獲取起始位

//2、3、4、5、6、7、8、9波特率定時器,采樣數據

//9、10接收校驗位和結束位

//11、12、產生完成脈沖信號

end

//串口發送 ---> 并轉串

always@(!rst_n)begin

if(!rst_n)

//復位

else if(I_rxtx_en[0])

//1、構建數據格式

//2~12 按位發送

//13、14產生完成脈沖信號

end

endmodule

這里想說明的是:

1、串口的單雙工和數據位寬都是可以配置的,按照自己的需求去設置;2、串口協議也是有時鐘的,只不過這個時鐘是隱含在協議里,除了常見的9600、38400、115200,自己也可以去配置特殊模式的串口,關鍵是雙方都要遵守相同的協議,那么SerDes呢?

相同的,SerDes也是收發兩條線,準確地說,是兩組,因為它是差分形式,即tx_p、tx_n,rx_p、rx_n;在數據端也是可以配置成不同的數據位寬和單雙工模式;

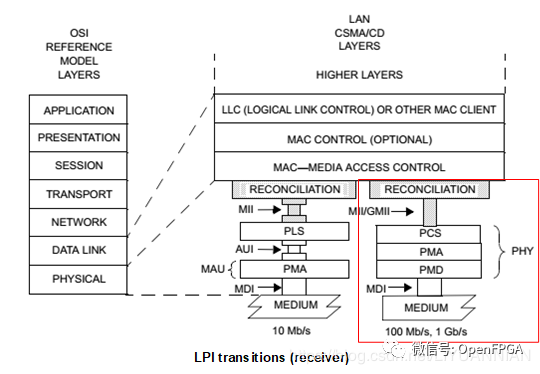

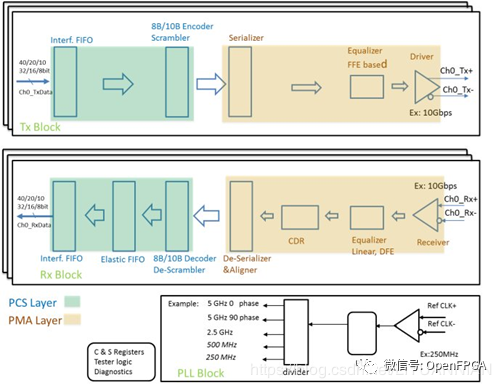

不同的,就是在于SerDes的時鐘是隱含在數據中!這就需要額外的電路去完成數據和時鐘的“融合”與“解析”,而這正是PCS和PMA的作用,其內部采用的編碼技術和信號補償技術正是為了完美的將時鐘“融合”進串行數據(發送端),再將時鐘從串行數據中“解析出來”(接收端)。

SERDES主要由物理介質相關( PMD)子層、物理媒介附加(PMA)子層和物理編碼子層( PCS )所組成。PMD是負責串行信號傳輸的電氣塊。PMA負責串化/解串化,PCS負責數據流的編碼/解碼。在PCS的上面是上層功能。針對FPGA 的SERDES ,PCS提供了ASIC塊和FPGA之間的接口邊界。

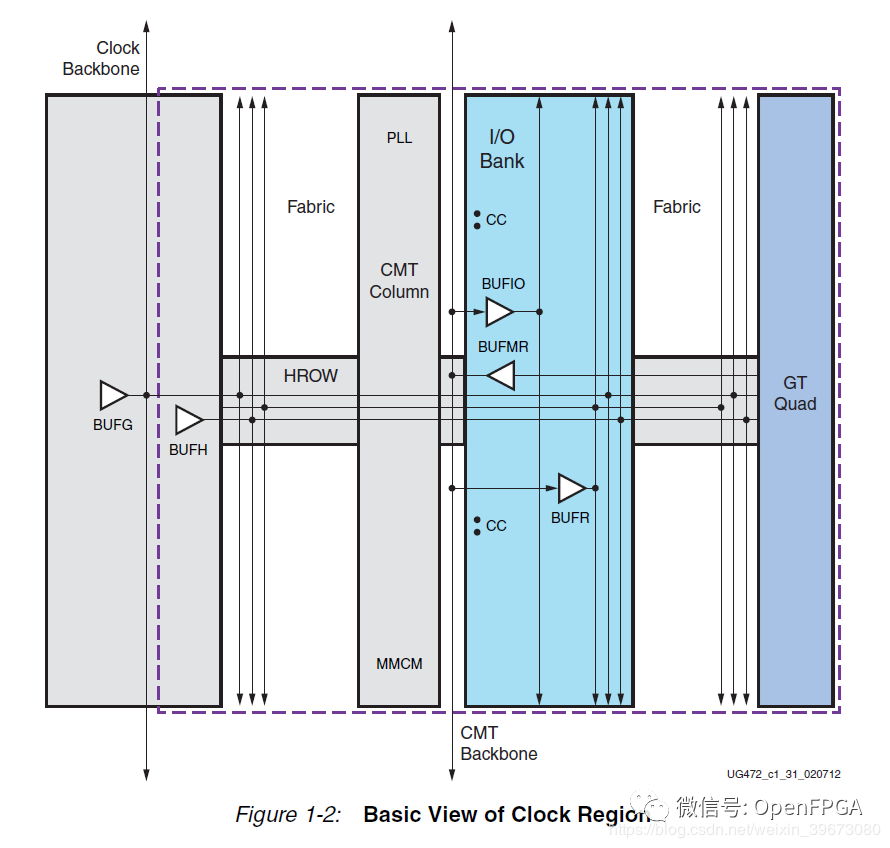

Xilinx將這個SerDes硬核進行了封裝,成為GigabitTransceiver,即GT,而它在BANK里的位置和數量都是固定的,從這個角度來看這也算是它不靈活的不足所在吧。

接下來就是SGMII和SerDes的區別

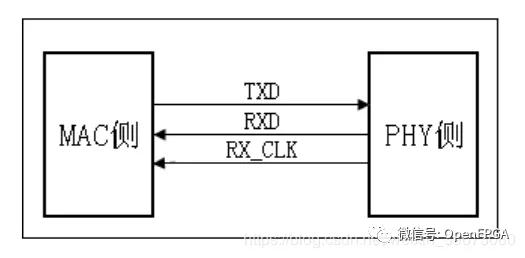

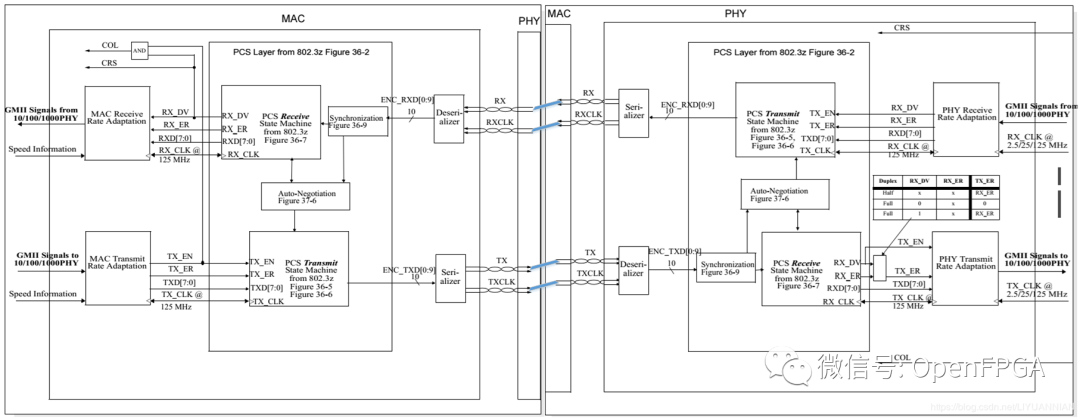

圖1 SGMII的MAC側和PHY側

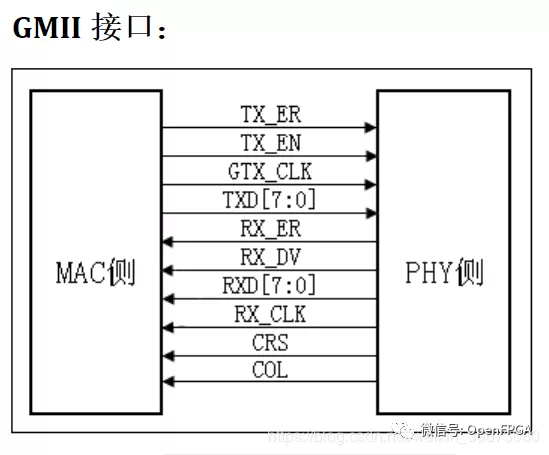

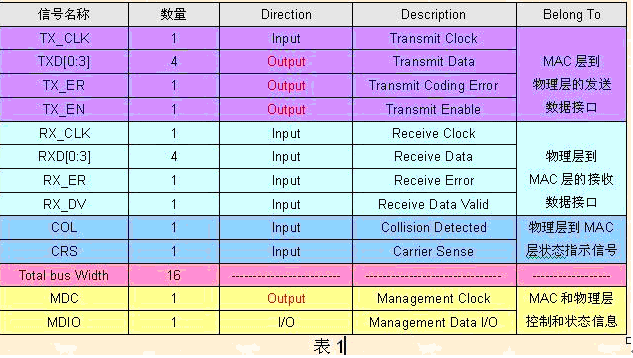

剛看到上圖時,感覺很奇怪,PCS為什么還存在于MAC中?GMII規范中PCS只存在于PHY中,見下圖。

圖2 GMII在OSI模型中的位置

實際上SGMII對應的MAC和PHY的劃分是將SGMII接口斷開,一端歸為MAC,一端歸為PHY;同樣,GMII對應的MAC和PHY的劃分是將GMII接口斷開,一端歸為MAC,一端歸為PHY。下圖是將圖1整理后的圖。

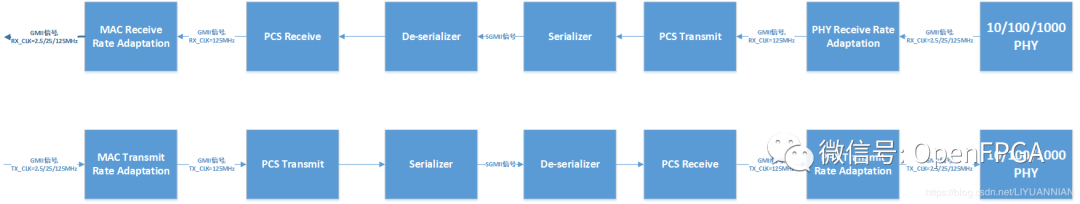

圖3 整理后的SGMII信號接收和發送流程

上圖可以看出,SGMII接口就是使用了SerDes技術的GMII接口,SerDes上跑的是10b信號,在接收端,PCS Transmit將GMII的8b信號編碼為10b信號,經過Serializer串行化后在SerDes高速路上傳輸到PCS Receive模塊,它將10b信號解碼為8b信號送至MAC Receive Rate Adaptation模塊。因此SGMII相對于GMII多了個S,這個S就是SerDes技術,它提供了一個高速傳輸通道。

在交換芯片中經常可以看到1個Port可以被配置為SGMII/SerDes模式,個人理解的是SGMII相對于SerDes多了一個速率協商(比如上圖中的PHY Receive RateAdaptation模塊),當使能了SGMII模式,就是使能了PHY Receive Rate Adaptation模塊,當使能了SerDes模式,就是禁用了或者未使用PHY Receive RateAdaptation模塊,這樣猜測的原因是在光模塊或者電模塊選型時,發現SerDes接口的光模塊或電模塊總是僅支持1000Mbps速率;而SGMII接口的電模塊總是能支持10/100/1000Mbps速率,但是沒看到能支持這種猜測的文章。

下圖是SerDes的發送和接收結構。

圖4 SerDes的發送和接收結構

SerDes通道傳輸的10b信號,因此在SerDes發送端,需要上圖的PCS實現8b/10b編碼,之后是串行化以上高速跑道;

在SerDes接收端,需要上圖的PCS實現10b/8b解碼,之后是解串行化,以下高速跑道。

在進行電路設計時,當交換的1個Port配置為SerDes模式,它能接光模塊和電模塊,但是速率是不可協商的,當接光模塊,光模塊也僅是進行光電或電光的轉換,以在光纖中傳輸,并不涉及到PCS等概念;當配置為SGMII模式,它只能接電模塊,因為電模塊內部是有PHY和變壓器的,所以此時的設計模式就是MAC+PHY+變壓器的常規模式。

總結一下:

其實,大多數MAC芯片的SGMII接口都可以配置成SerDes接口(在物理上完全兼容,只需配置寄存器即可),

SerDes直接外接光模塊,而不需要PHY層芯片,此時時鐘速率仍舊是625MHz,不過此時跟SGMII接口不同,SGMII接口速率被提高到1.25Gbps是因為插入了控制信息,而SerDes端口速率被提高是因為進行了8B/10B變換,本來8B/10B變換是PHY芯片的工作,在SerDes接口中,因為外面不接PHY芯片,此時8B/10B變換在MAC芯片中完成了。8B/10B變換的主要作用是擾碼,讓信號中不出現過長的連“0”和連“1”情況,影響時鐘信息的提取

所以感覺是mac芯片用加2bit控制信息的功能模塊去完成了8B/10B變換,這樣SerDes信號就可以直接出去了。

SerDes通道和SerDes接口是兩個概念,SGMII也是需要SerDes通道(SERDES lane)的。

而SGMII需要插入2bit控制信號變成10b是因為SGMII需要控制信來實現10/100/1000速率協商,而SerDes是固定速率(1000BASE-x)。

PHY收到mac sgmii的10b后,將控制信號去除后,將數據發送出去前還是會加擾碼完成8B/10B變換。

-

Mac

+關注

關注

0文章

1117瀏覽量

53165 -

SerDes

+關注

關注

7文章

217瀏覽量

35841 -

PCI-e總線

+關注

關注

1文章

2瀏覽量

7142

發布評論請先 登錄

評論