作者:Andreas Braun & Stefan Wiehler設(shè)計工程師,MLE 公司

創(chuàng)建 FPGA 設(shè)計和維護(hù) Vivado? 設(shè)計套件項目時,版本控制系統(tǒng)對于團(tuán)隊合作可能是一項具有挑戰(zhàn)性的任務(wù)。工程師必須能跟蹤設(shè)計變更,完整地從 HDL 或 TCL 源代碼再現(xiàn)項目并交付特定的項目狀態(tài)。Vivado 工具非常適用于這類工作,因為該工具能夠為項目生成存檔文件或創(chuàng)建 TCL 文件,從而再現(xiàn)項目狀態(tài)。

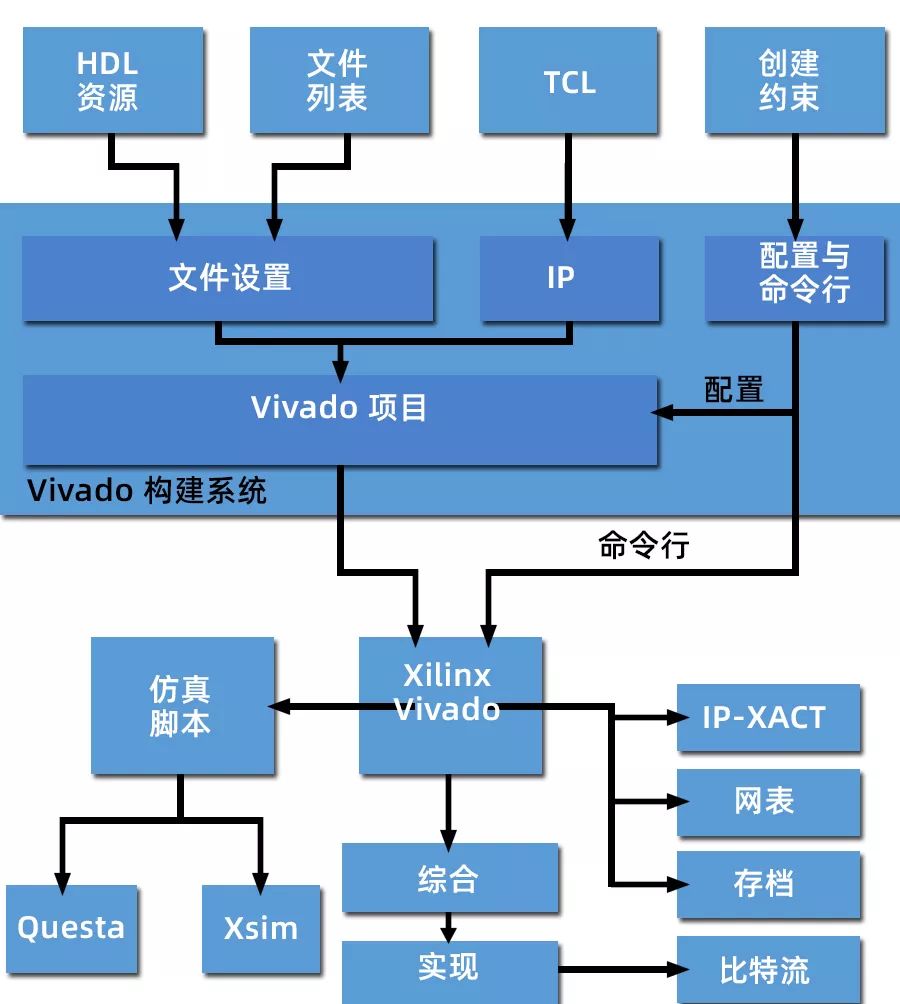

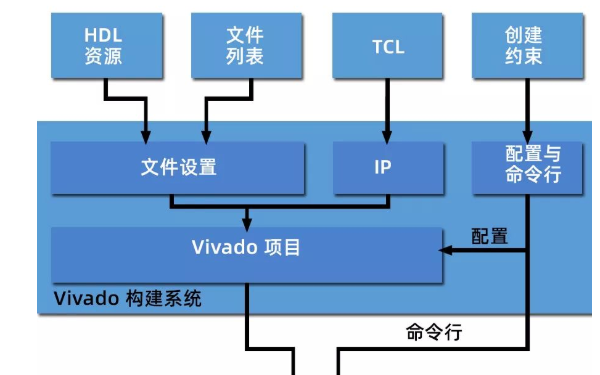

然而,上述機(jī)制需要一定數(shù)量的手動操作,而且在 Vivado 設(shè)計套件項目外對設(shè)計的參數(shù)進(jìn)行設(shè)置,也存在不夠靈活的問題。因此,為了簡化上述操作,我們已經(jīng)開發(fā)出對應(yīng)腳本。其思路是在提供項目的 HDL 和 TCL 源文件的同時,提供從頭創(chuàng)建 Vivado 設(shè)計套件項目所需的其他配置文件。設(shè)計構(gòu)建腳本的目的是幫助用戶在單獨的 Vivado 設(shè)計套件項目下開發(fā)獨立的項目組成部分(特色),且能夠以其他配置方式對項目不同組成部分的源文件進(jìn)行組合。此外,構(gòu)建腳本也可用于創(chuàng)建目標(biāo)構(gòu)建工件,例如 IP XACTIPXACT 封裝、仿真、綜合、實現(xiàn)和比特流生成。

與此同時,MLE 也面向 PetaLinux 和賽靈思軟件開發(fā)套件 (XSDK) 發(fā)布了一套易用型 Makefiles,并將為 Vitis? 統(tǒng)一軟件平臺提供后續(xù)支持。這些處理系統(tǒng) Makefiles(或簡稱為 PSMake)還提供在 GitHub 上。

-

FPGA

+關(guān)注

關(guān)注

1630文章

21781瀏覽量

604936 -

賽靈思

+關(guān)注

關(guān)注

32文章

1794瀏覽量

131410 -

HDL

+關(guān)注

關(guān)注

8文章

327瀏覽量

47424 -

TCL

+關(guān)注

關(guān)注

10文章

1736瀏覽量

88757 -

Vivado

+關(guān)注

關(guān)注

19文章

815瀏覽量

66750

發(fā)布評論請先 登錄

相關(guān)推薦

FPGA設(shè)計之自動化

自動化測試框架思想和構(gòu)建

如何實現(xiàn)智能電網(wǎng)自動化?

饋線自動化通信系統(tǒng)怎么實現(xiàn)?

如何搭建DotNet Core 21自動化構(gòu)建和部署環(huán)境

什么是開放性系統(tǒng)?如何構(gòu)建開放自動化的生態(tài)系統(tǒng)?

LabVIEW與Tektronix示波器實現(xiàn)電源測試自動化

FPGA自動化測試難度凸顯

FPGA構(gòu)建環(huán)境的自動化怎么實現(xiàn)

如何實現(xiàn)FPGA構(gòu)建環(huán)境的自動化

如何構(gòu)建藍(lán)牙控制的家庭自動化

家庭自動化系統(tǒng)開源構(gòu)建

自動化構(gòu)建環(huán)境在FPGA設(shè)計中的應(yīng)用

如何實現(xiàn) FPGA 構(gòu)建環(huán)境的自動化

如何實現(xiàn) FPGA 構(gòu)建環(huán)境的自動化

評論