互聯結構包括直通模式、只轉換模式、N-1互聯模式、N-M互聯模式。

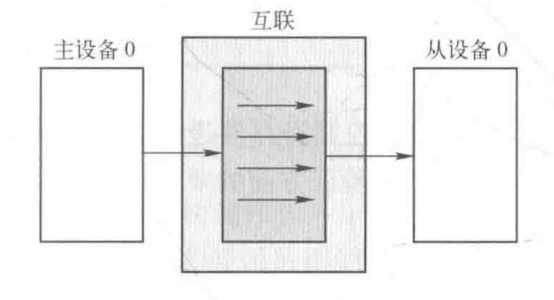

1. 直通模式

當只有一個主設備和一個從設備使用AXI互聯時,AXI互聯不執行任何轉換或流水線功能,AXI互聯結構退化成直接的線連接。在這種模式下,沒有延遲,同時不消耗邏輯資源。

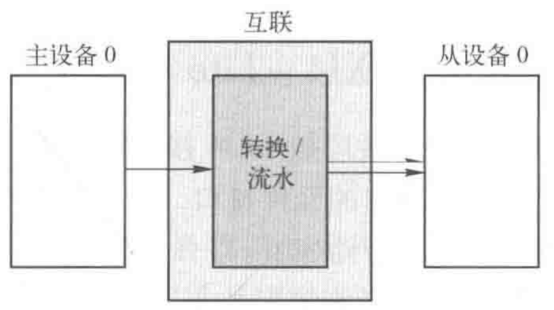

2. 只轉換模式

當連接一個主設備和一個從設備時,AXI互聯執行不同的轉換和流水線功能:數據位寬轉換、時鐘速率轉換、AXI-Lite從適應、AXI-3從適應、流水線。在只轉換模式下,AXI互聯不包含仲裁、解碼或布線邏輯,但是可能產生延遲。

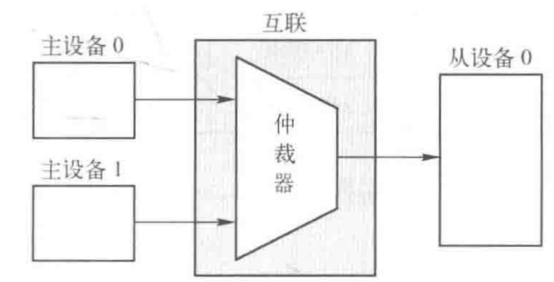

3. N-1互聯模式

N-1互聯模式是多個主設備訪問一個從設備,典型地,一個存儲器控制器,很顯然需要仲裁邏輯。這種情況下,AXI互聯不需要地址譯碼邏輯。在這種配置中,也可以執行數據寬度和時鐘速率轉換。

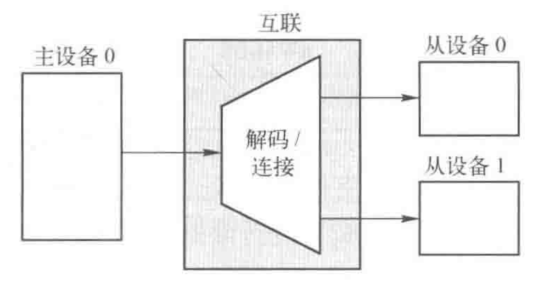

4. 1-N互聯模式

1-N互聯結構是一個主設備訪問多個存儲器映射的從外設。在這種模式下,AXI互聯不執行仲裁。

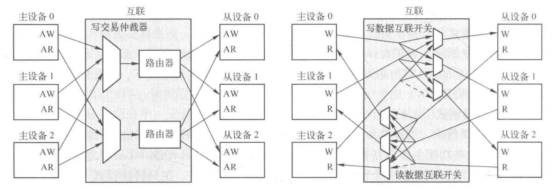

5. N-M互聯模式

AXI互聯提供了一種共享地址多數據流拓撲結構,這種結構包含稀疏的數據交叉開關連接、單線程寫和讀地址仲裁。

編輯:hfy

-

Zynq

+關注

關注

10文章

610瀏覽量

47193 -

AXI

+關注

關注

1文章

127瀏覽量

16634 -

存儲器控制器

+關注

關注

0文章

8瀏覽量

4803

發布評論請先 登錄

相關推薦

看看在SpinalHDL中AXI4總線互聯IP的設計

AMBA 4 AXI4、AXI4-Lite和AXI4-流協議斷言用戶指南

全面介紹ZYNQ-AXI互聯IP

AXI4 、 AXI4-Lite 、AXI4-Stream接口

AXI3與AXI4寫響應的依賴區別?

Xilinx FPGA AXI4總線(一)介紹【AXI4】【AXI4-Lite】【AXI-Stream】

漫談AMBA總線-AXI4協議的基本介紹

Xilinx NVMe AXI4主機控制器,AXI4接口高性能版本介紹

zynq中AXI4的五種互聯結構介紹

zynq中AXI4的五種互聯結構介紹

評論