時序路徑

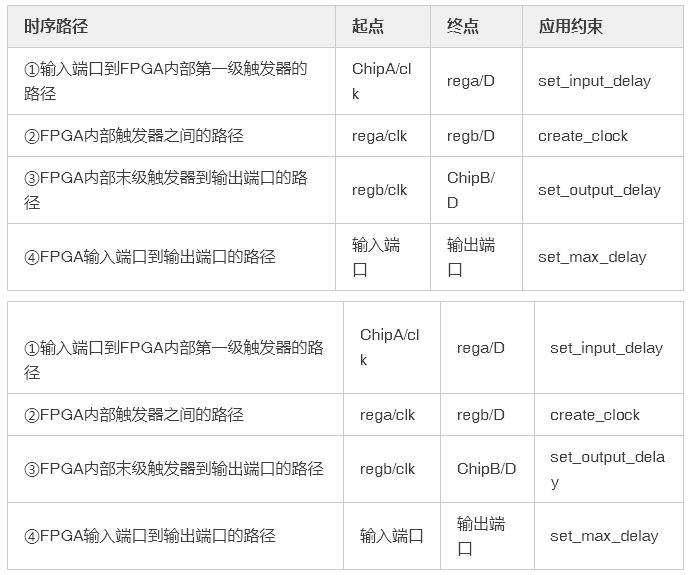

典型的時序路徑有4類,如下圖所示,這4類路徑可分為片間路徑(標記①和標記③)和片內路徑(標記②和標記④)。

對于所有的時序路徑,我們都要明確其起點和終點,這4類時序路徑的起點和終點分別如下表。

這4類路徑中,我們最為關心是②的同步時序路徑,也就是FPGA內部的時序邏輯。

時序模型

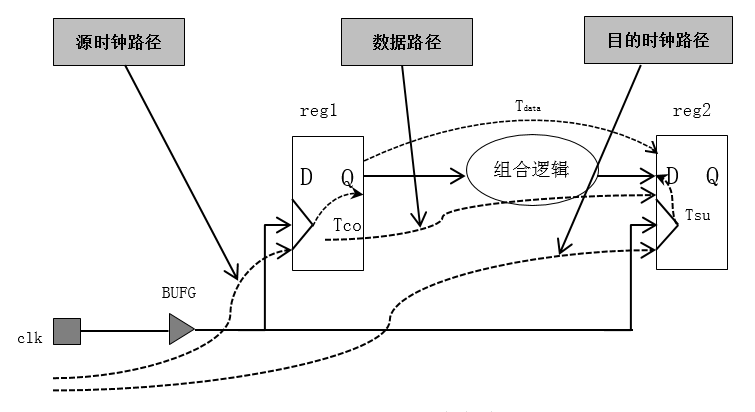

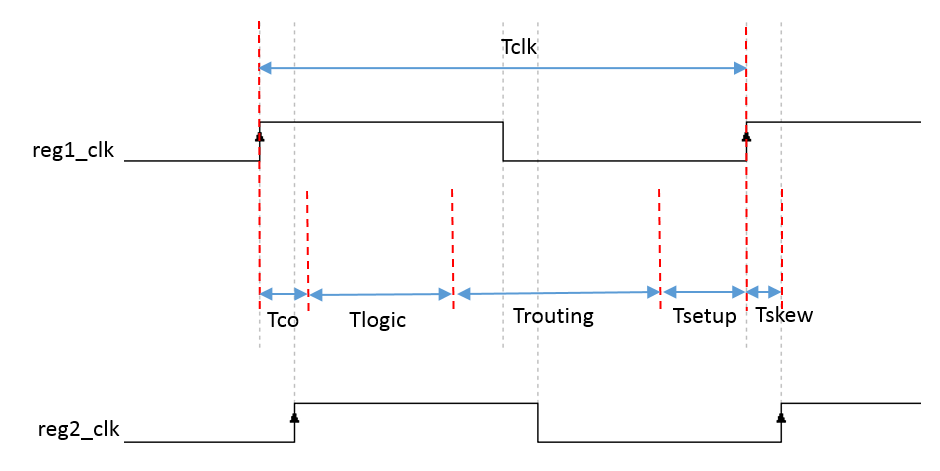

典型的時序模型如下圖所示,一個完整的時序路徑包括源時鐘路徑、數據路徑和目的時鐘路徑,也可以表示為觸發器+組合邏輯+觸發器的模型。

該時序模型的要求為(公式1)

Tclk ≥ Tco + Tlogic + Trouting + Tsetup - Tskew

其中,Tco為發端寄存器時鐘到輸出時間;Tlogic為組合邏輯延遲;Trouting為兩級寄存器之間的布線延遲;Tsetup為收端寄存器建立時間;Tskew為兩級寄存器的時鐘歪斜,其值等于時鐘同邊沿到達兩個寄存器時鐘端口的時間差;Tclk為系統所能達到的最小時鐘周期。

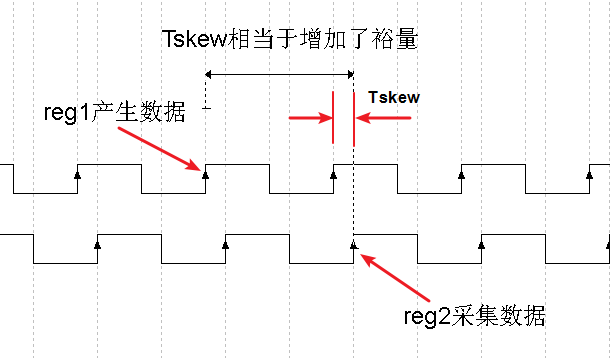

這里我們多說一下這個Tskew,skew分為兩種,positive skew和negative skew,其中positive skew見下圖,這相當于增加了后一級寄存器的觸發時間。

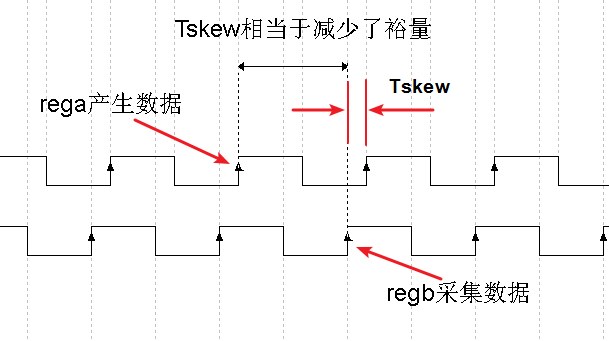

但對于negative skew,則相當于減少了后一級寄存器的觸發時間,如下圖所示。

當系統穩定后,都會是positive skew的狀態,但即便是positive skew,綜合工具在計算時序時,也不會把多出來的Tskew算進去。

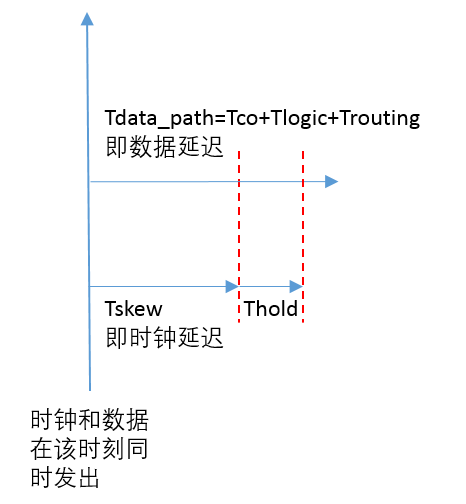

用下面這個圖來表示時序關系就更加容易理解了。為什么要減去Tskew,下面這個圖也更加直觀。

發送端寄存器產生的數據,數據經過Tco、Tlogic、Trouting后到達接收端,同時還要給接收端留出Tsetup的時間。而時鐘延遲了Tskew的時間,因此有:(公式2)

Tdata/_path + Tsetup < = Tskew + Tclk

對于同步設計Tskew可忽略(認為其值為0),因為FPGA中的時鐘樹會盡量保證到每個寄存器的延遲相同。

公式中提到了建立時間,那保持時間在什么地方體現呢?

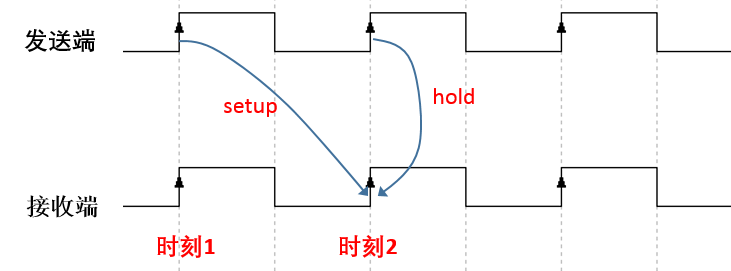

保持時間比較難理解,它的意思是reg1的輸出不能太快到達reg2,這是為了防止采到的新數據太快而沖掉了原來的數據。保持時間約束的是同一個時鐘邊沿,而不是對下一個時鐘邊沿的約束。

reg2在邊沿2時刻剛剛捕獲reg1在邊沿1時刻發出的數據,若reg1在邊沿2時刻發出的數據過快到達reg2,則會沖掉前面的數據。因此保持時間約束的是同一個邊沿。

在時鐘沿到達之后,數據要保持Thold的時間,因此,要滿足:(公式3)

Tdata/_path = Tco + Tlogic + Trouting ≥ Tskew + Thold

這兩個公式是FPGA的面試和筆試中經常問到的問題,因為這種問題能反映出應聘者對時序的理解。

在公式1中,Tco跟Tsu一樣,也取決于芯片工藝,因此,一旦芯片型號選定就只能通過Tlogic和Trouting來改善Tclk。其中,Tlogic和代碼風格有很大關系,Trouting和布局布線的策略有很大關系。

編輯:hfy

-

寄存器

+關注

關注

31文章

5419瀏覽量

123241 -

觸發器

+關注

關注

14文章

2032瀏覽量

61850 -

時序路徑

+關注

關注

0文章

12瀏覽量

1442

發布評論請先 登錄

AXI握手時序優化—pipeline緩沖器

集成電路設計中靜態時序分析介紹

高速ADC與FPGA的LVDS數據接口中避免時序誤差的設計考慮

鎖存器的基本輸出時序

DRAM內存操作與時序解析

電源時序器屬于控制繼電器嗎

電源時序器輸出電壓多少伏

電源時序器的原理及使用方法是什么

輕松實現復雜的電源時序控制

評論