隨著電子設(shè)計領(lǐng)域的高速發(fā)展,產(chǎn)品越來越小,速率越來越高,信號完整性越來越成為一個硬件工程師需要考慮的問題。串?dāng)_,阻抗匹配等詞匯也成為了硬件工程師的口頭禪。今天,我們就來學(xué)習(xí)關(guān)于串?dāng)_的一些知識。

什么是串?dāng)_

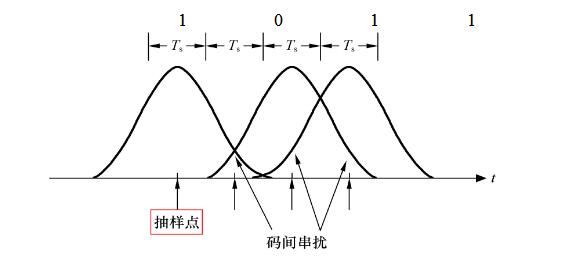

串?dāng)_(Crosstalk),顧名思義、是指不同信號互連鏈路之間的相互干擾。對于傳輸線而言,即能量從一條傳輸線耦合到另一條傳輸線上,當(dāng)不同傳輸線產(chǎn)生的電磁場發(fā)生相互作用時就會產(chǎn)生。

串?dāng)_中的信號耦合分為容性耦合和感性耦合,通常感性串?dāng)_占的比例大于容性串?dāng)_。

容性耦合會引發(fā)驅(qū)動電流浪涌,從而導(dǎo)致傳輸線上的反射。

感性耦合會產(chǎn)生地彈和電源噪聲。

在數(shù)字電路系統(tǒng)中,串?dāng)_現(xiàn)象相當(dāng)普遍,串?dāng)_可以發(fā)生在芯片內(nèi)核、芯片的封裝、PCB板上、接插件上、以及連接線纜上,只要有臨近的銅互連鏈路,就存在信號間的電磁場相互作用,從而產(chǎn)生串?dāng)_現(xiàn)象。

串?dāng)_的危害

串?dāng)_可能是數(shù)據(jù)進行高速傳輸中最重要的一個影響因素了。它是一個信號對另外一個信號耦合所產(chǎn)生的一種不受歡迎的能量值。根據(jù)麥克斯韋定律,只要有電流的存在,就會有磁場存在,磁場之間的干擾就是串?dāng)_的來源。這個感應(yīng)信號可能會導(dǎo)致數(shù)據(jù)傳輸?shù)膩G失和傳輸錯誤。 所以串?dāng)_對于綜合布線來說,無疑是個最厲害的天敵。

減小信號間串?dāng)_的方法

我們知道,信號間的串?dāng)_來源于電磁場的互相干擾作用,電場的場強是離信號源中心越遠(yuǎn)則越弱,所以控制信號間串?dāng)_最直接有效的方法就是:

方法一:增加傳輸線或互連鏈路之間的間隔距離,減小串?dāng)_

在信號串?dāng)_的控制上通常有“3W規(guī)則”、“ 5H規(guī)則”的說法,所謂“3W規(guī)則”是指傳輸線的間距需要大于3倍的傳輸線線寬W,所謂“5H規(guī)則”是指傳輸線的間距需要大于5倍的傳輸線與參考平面的距離H。在實際的PCB設(shè)計中,要均衡考慮布線空間與串?dāng)_控制,遵循的規(guī)則可以理解為上面“3W”、“ 5H”兩種規(guī)則的結(jié)合體。

“3H規(guī)則”,即傳輸線之間的間距不小于3倍的傳輸線與參考平面的距離H。

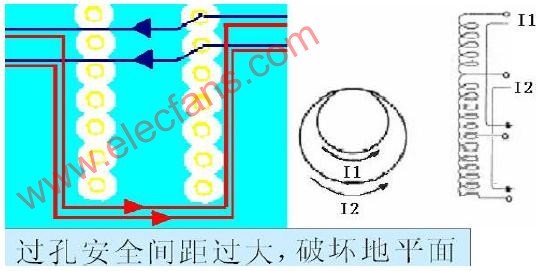

另外,信號在互連鏈路中的傳輸,是存在“回流路徑”的,電路信號傳輸必須要形成閉環(huán),它會尋找“環(huán)路電感”最小的路徑回流到源端;對于有著完整參考地平面的PCB板,信號傳輸線會沿著傳輸線垂直正下方的地平面對應(yīng)的投影路徑返回源端,這時有著完美參考平面與回流路徑的傳輸線的抗干擾能力是比較強的,因此:

方法二:讓傳輸線有完整的參考回流地平面,并且層疊設(shè)計上盡可能靠近地平面

結(jié)合信號的反射理論,串?dāng)_信號在到達(dá)源端或接收端時,如果互連鏈路匹配不好,就會再產(chǎn)生反射信號,從而造成在互連鏈路上的多重發(fā)射,這些串?dāng)_信號多重反射的結(jié)果同樣會疊加到受擾信號上,造成串?dāng)_噪聲的增加,因此:

方法三:傳輸線及互連鏈路的良好匹配設(shè)計也能減小串?dāng)_

編輯:hfy

-

信號完整性

+關(guān)注

關(guān)注

68文章

1410瀏覽量

95528 -

數(shù)字電路

+關(guān)注

關(guān)注

193文章

1608瀏覽量

80693 -

電磁場

+關(guān)注

關(guān)注

0文章

792瀏覽量

47302

發(fā)布評論請先 登錄

相關(guān)推薦

高速數(shù)字電路設(shè)計串擾問題產(chǎn)生的機理原因

消除串擾的方法

原創(chuàng)|SI問題之串擾

PCB不同頻率間模擬信號的串擾

如何降低嵌入式系統(tǒng)串擾的影響?

如何減小SRAM讀寫操作時的串擾

高速數(shù)字電路信號完整性分析與設(shè)計

VHDL與數(shù)字電路系統(tǒng)設(shè)計實驗指導(dǎo)書

數(shù)字電路設(shè)計的信號完整性問題探討

數(shù)字電路系統(tǒng)減小信號間串?dāng)_的方法

數(shù)字電路系統(tǒng)減小信號間串?dāng)_的方法

評論