靜態時序分析是檢查IC系統時序是否滿足要求的主要手段。以往時序的驗證依賴于仿真,采用仿真的方法,覆蓋率跟所施加的激勵有關,有些時序違例會被忽略。此外,仿真方法效率非常的低,會大大延長產品的開發周期。靜態時序分析工具很好地解決了這兩個問題。它不需要激勵向量,可以報出芯片中所有的時序違例,并且速度很快。

通過靜態時序分析,可以檢查設計中的關鍵路徑分布;檢查電路中的路徑延時是否會導致setup違例;檢查電路中是否由于時鐘偏移過大導致hold違例;檢查時鐘樹的偏移和延時等情況。此外靜態時序分析工具還可以與信號完整性工具結合在一起分析串擾問題。常用的靜態時序工具是PrimeTime。

下面主要闡述一下靜態時序的分析原理:靜態時序分析工具讀入門級網表、時序約束等信息,然后進行靜態時序分析。分析過程可以分為3步:

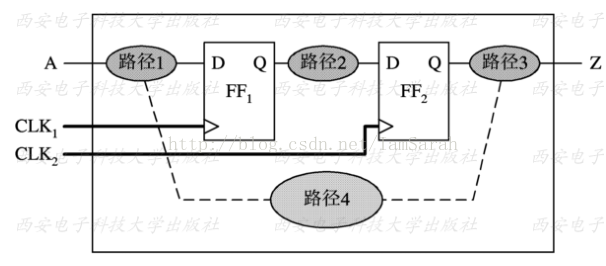

1)將電路分解為時序路徑,即將電路轉換為時序路徑的集合。時序路徑是一個點到點的數據通路,數據沿著時序路徑進行傳遞。它的起點是輸入端口或者寄存器的時鐘,終點是輸出端口或者一個寄存器的輸入引腳,每個路徑最多只能穿過一個寄存器。這樣時序路徑就可以劃分為:輸入端口到寄存器、寄存器到寄存器、寄存器到輸出端口、輸入端口到輸出端口。如下圖所示,分析其時序路徑:

根據時序路徑的定義,我們可以找到4條時序路徑:從輸入端口A到FF1的D端;從FF1的Clk端到FF2的D端;從FF2的clk端到輸出端口out1;從輸入端口A到輸出端口out1。將這些路徑在下圖標出:

2)計算每個路徑上面的延時。在一個路徑上,可能包含這幾類延時:連線延時(布局布線前后的延時計算方法不一樣)、組合邏輯的單位延時(影響因子有輸入信號的轉換時間,該值也決定輸入晶體管的翻轉速度、負載、單元本身的固有延時、制程、電壓、溫度等)、寄存器從clk端到Q端的延時。一個路徑上的延時是該路徑上所有連線的延時與單位延時的綜合。延時一般定義為從輸入跳變的50%時刻到輸出跳變的50%之間的時間。

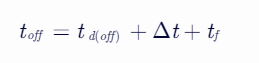

3)檢查路徑時序約束是否滿足。路徑約束主要指的是建立時間約束和保持時間約束。在寄存器的綜合庫描述中對寄存器的D端定義了建立時間和保持時間的約束。所謂建立時間約束是指在采樣時鐘到達之前,數據應該穩定的時間;保持時間是指在時鐘到達之后,數據應該保持的時間,這樣才能保證寄存器正確地鎖存數據。對于純組合邏輯,時序分析主要檢查最大延時約束和最小延時路徑。這種情況比較簡單。

時鐘對于時序電路至關重要。在進行RTL設計時,可以認為時鐘是理想的,但在靜態時序分析的時候,必須考慮到實際的時鐘情形。時鐘模型的精度直接影響了靜態時序分析的精度。時鐘的非理想性包括:

1)時鐘偏移(clock skew):同一時鐘原到達不同的寄存器的延時不同。

2)時鐘抖動(clock jitter):時鐘頻率和相位會不斷變化,脈沖寬度會發生變化。

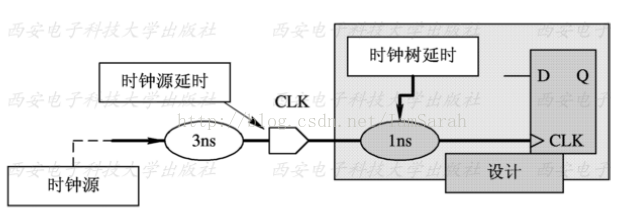

實際情況中,振蕩器、互連、電源、負載都會影響到時鐘,導致時鐘出現偏移、抖動。下面主要講一下在靜態時序分析中,如何對實際的時鐘進行建模。考慮下圖中的電路,電路中時鐘源位于芯片外部。我們將時鐘定義在芯片端口上,從時鐘源到達端口需要經過3ns左右的延時(板級走線的延時),從時鐘端口到寄存器要經過1ns左右的延時(時鐘樹的延時),對時鐘樹的延時進行建模可以采取下面的辦法:

1)先在端口上定義時鐘:

create_clock per8.0 [get_ports clk]

2)設置從時鐘源到時鐘端口的板級延時:

set_clock_latency source 3 clk

3)設置時鐘樹本身的延時,在布局布線之前可以采取下面的方法: set_clock_latency 1 clk;在布局布線之后,可以得到時鐘樹延時的確定值,采用如下的命令:set_propagated_clock clk;

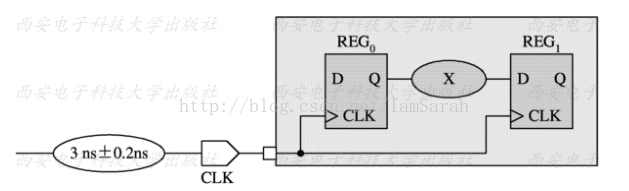

但是如果知道時鐘源上的時鐘具有0.2ns的不確定性,如下圖所示,可以采用下面的方法進行建模:

set_clock_latency 2.8 source early [get_ports clk]

set_clock_latency 3.2 source late [get_ports clk]

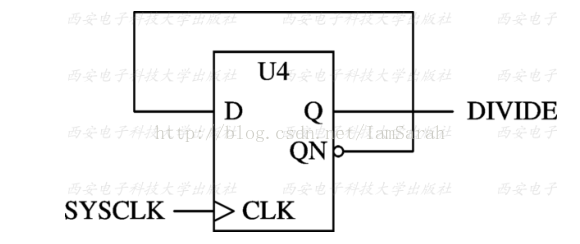

在設計中,往往存在分頻時鐘,如下圖是一個2分頻電路。

如果進行靜態時序分析時,直接援用create_clock來設置,則PT會將分頻后的時鐘看做是一個與源時鐘毫無關系的時鐘。這樣在分析源時鐘域與分頻時鐘域之間的信號時,可能會出現問題。正確設置分頻時鐘方法如下:

create_generated_clock name divide

source [get -pins U4/clk] divide-by 2 [get -pins U4/Q]

下面概括介紹一下對于靜態時序分析腳本構造的大致過程:

1)讀入設計的相關信息:鏈接庫、網表,如果是PR之后的靜態時序分析還需要讀入寄生參數信息

2)設置驅動及負載

3)設置時鐘

4)設置建立時間和保持時間

5)設置設計規則約束:最大負載、最大轉換時間等

6)分析時序:用report_timing 等檢查時序,用report_constraint 檢查是否有違例。

具體的構造過程可以參考綜合腳本,這里不再詳述。

編輯:hfy

-

寄存器

+關注

關注

31文章

5336瀏覽量

120230 -

晶體管

+關注

關注

77文章

9682瀏覽量

138080 -

數據通路

+關注

關注

0文章

6瀏覽量

7480 -

靜態時序

+關注

關注

0文章

19瀏覽量

6943

發布評論請先 登錄

相關推薦

LM4811在啟動時或者shutdown開啟關閉過程中,增益控制跟預想的有偏差是為什么?

電源時序器跳閘的原因和解決方法

鎖存器的基本輸出時序

時序邏輯電路故障分析

時序邏輯電路中如何判斷有效狀態和無效狀態

IGBT開關過程分析

電源時序器的電壓顯示功能

FPGA 高級設計:時序分析和收斂

信號分析的過程主要包括哪些

FPGA工程的時序約束實踐案例

靜態時序的分析原理及詳細過程

靜態時序的分析原理及詳細過程

評論