在fpga工程中加入時序約束的目的:

1、給quartusii 提出時序要求;

2、quartusii 在布局布線時會盡量優先去滿足給出的時序要求;

3、STA靜態時序分析工具根據你提出的約束去判斷時序是否滿足的標準。

舉個形象的比喻:就好比我要讓代工廠(類比quartus ii)給我加工一批零件,要求長寬高為10x10x10cm,誤差不超過1mm(類比時序約束條件)。代工廠按要求(即約束條件)開始進行生產加工,工廠為了不返工,肯定會盡量生產出達到我要求的零件。當加工完成后,質檢員(類比STA靜態時序分析工具)按我給出的要求進行檢驗看是否滿足要求。要是工廠想盡了各種辦法也不能達到我給出的要求,那么就是我給出的要求太高了(即時序約束中的過約束),要是我給出的要求太低(比如說加工成方形就行,而沒有指出長寬高),那么工廠很容易就生產出來了,但這并不是我想要的,這是由于我給出的約束太松 即相當于時序里的 欠約束。

quartus ii里的靜態時序分析(STA):是套用特定的時序模型,針對特定電路分析其是否違反設計者給定的時序限制。說白了就是檢查fpga內部所有寄存器的建立時間保持時間是否滿足spec給定的要求。

1、Data Arrival Time 數據到達目的寄存器REG2時間

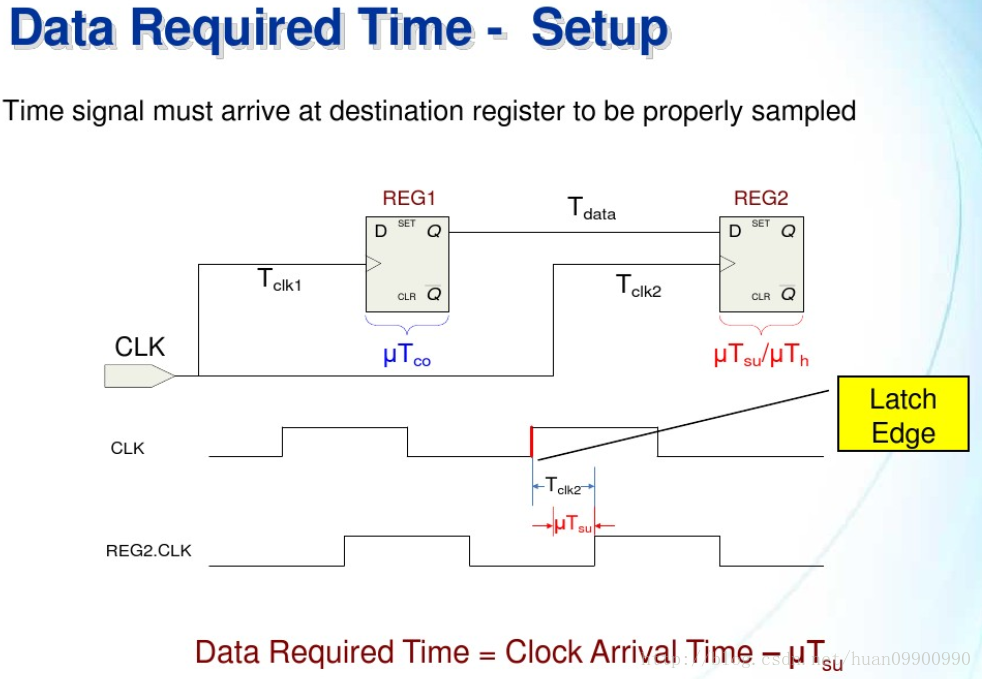

3、Data Required Time 數據需求時間-Setup

指數據需要在需求時間前到達目的寄存器,否則不滿足建立時間關系,不能被正確采樣。

最大延遲是防止數據來的太慢 ,當時鐘沿已經到來時,數據還沒到,這樣就不能在上升沿被寄存器正確采樣。

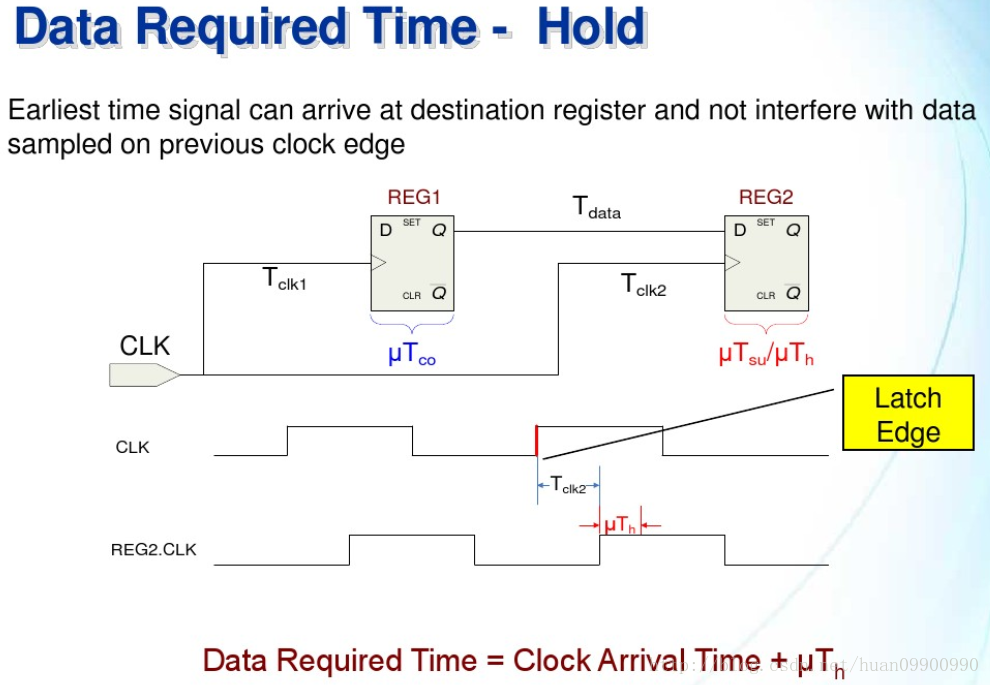

4、Data Required Time 數據需求時間-Hold

指數據在時鐘鎖存沿到達后,必須保持一段穩定的時間,使數據被正確采樣。做最小延遲約束是為了防止數據傳輸過快,使得寄存器還在鎖存上一個數據時,下一個數據就來了,使得上次鎖存數據發生錯誤。

所以 保持時間必須小于 tco+tlogic(組合邏輯延時),這里 tco+tlogic(組合邏輯延時)就是數據從源寄存器到目的寄存器的時間。

5、時序裕量slack

Setup Slack=Setup Required Time - Data Arrival Time

Hold Slack=Data Arrival Time - Hold Required Time

時序裕量為正 表示時序滿足時序約束條件,為負,時序不滿足。

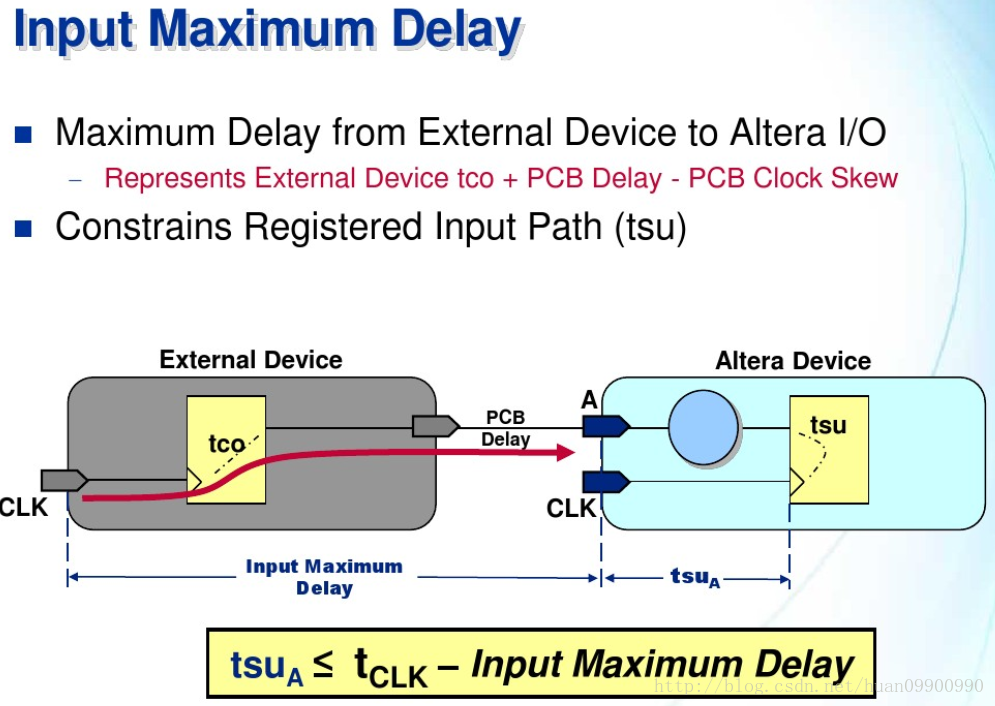

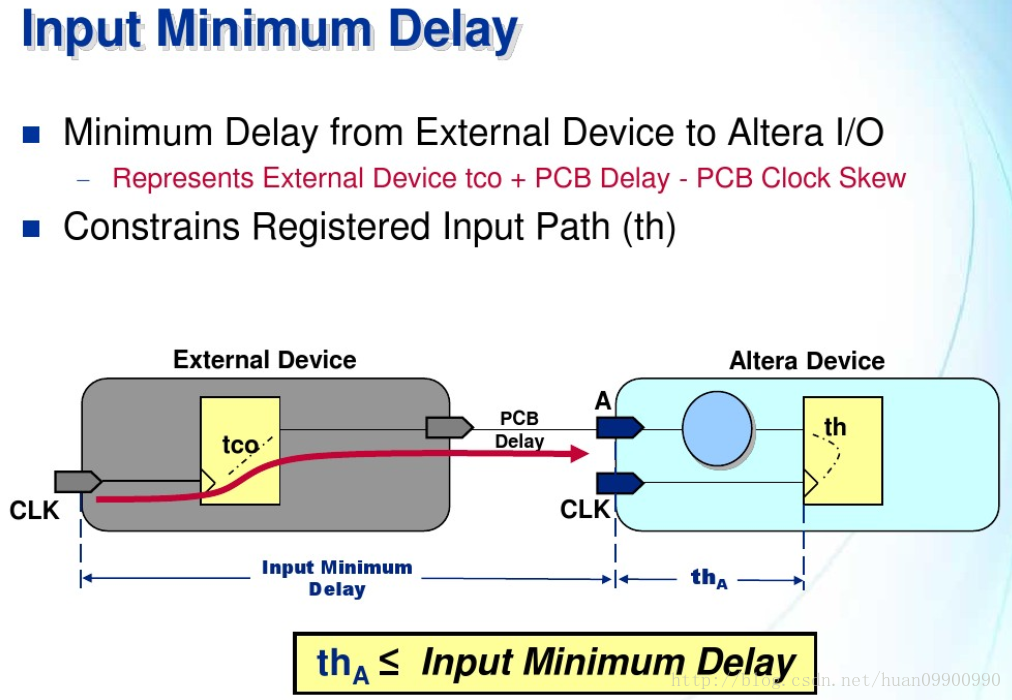

6、Input Delay 輸入最大最小延遲

Input Delay=數據路徑延遲-時鐘路徑延遲+utco(外部器件)

輸入延遲 Input Delay=Data Arrival Time-Clock Arrival Time

=launch Edge+Tclk1+uTco+Tdata-latch edge-Tclk2

數據相對于時鐘到達目的寄存器的時間差值。即數據和時鐘從同一時間點(launch)開始,到達目的寄存REG2的時間差。

數據到達REG2走的路徑延時是:時鐘從launch開始 經過Tclk1的延遲到達REG1,REG1在時鐘沿來之后,經過Tco的時間把數據送出REG1,然后數據再經過路徑延遲Tdata 到達REG2的數據管腳。

時鐘到達REG2走的路徑延時是:時鐘也從同一時間點(launch)開始,經過路徑延遲Tclk2就到達REG2的時鐘管腳。

輸入最大延遲是約束為了滿足寄存器的建立時間,輸入最小延遲是位了滿足寄存器的保持時間。

Input Maximum Delay=Data Arrival Time最大值-Clock Arrival Time 最小值

“fpga-centric”Input Maximum Delay<=tclk-tsu(fpga)

Input Minimum Delay=Data Arrival Time最小值-Clock Arrival Time 最大值

“fpga-centric” Input Minimum Delay>=th(fpga)

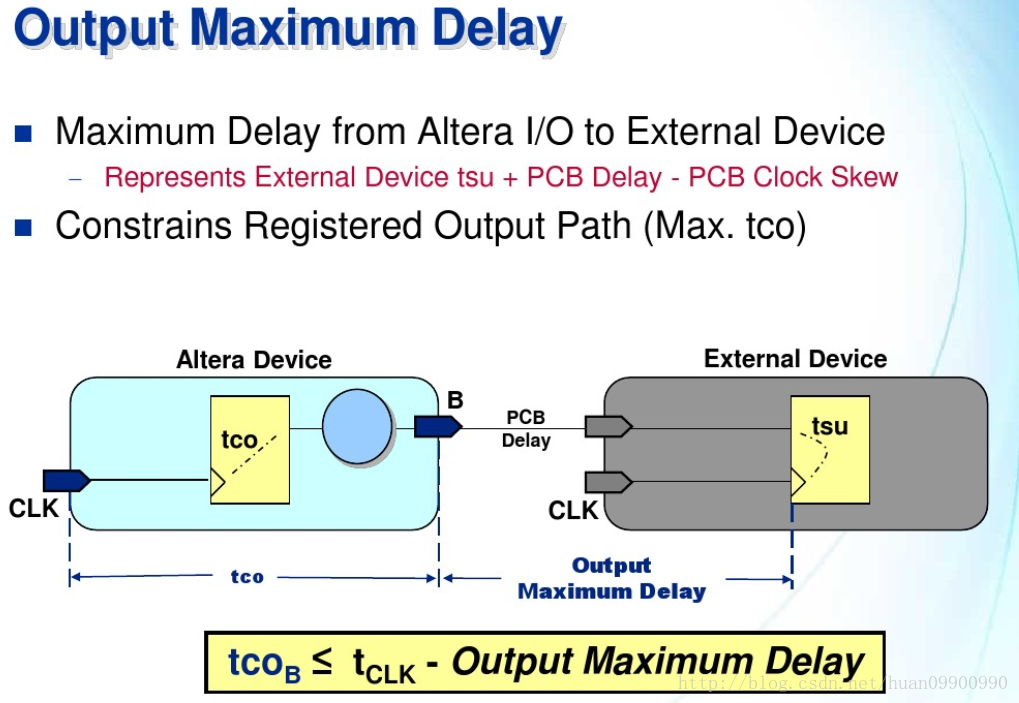

7、output Delay 輸出最大最小延遲

output Maximum Delay=外部器件tsu+數據路徑最大延遲-時鐘路徑最小延遲

output Minimum Delay=外部器件th+數據路徑最小延遲-時鐘路徑最大延遲

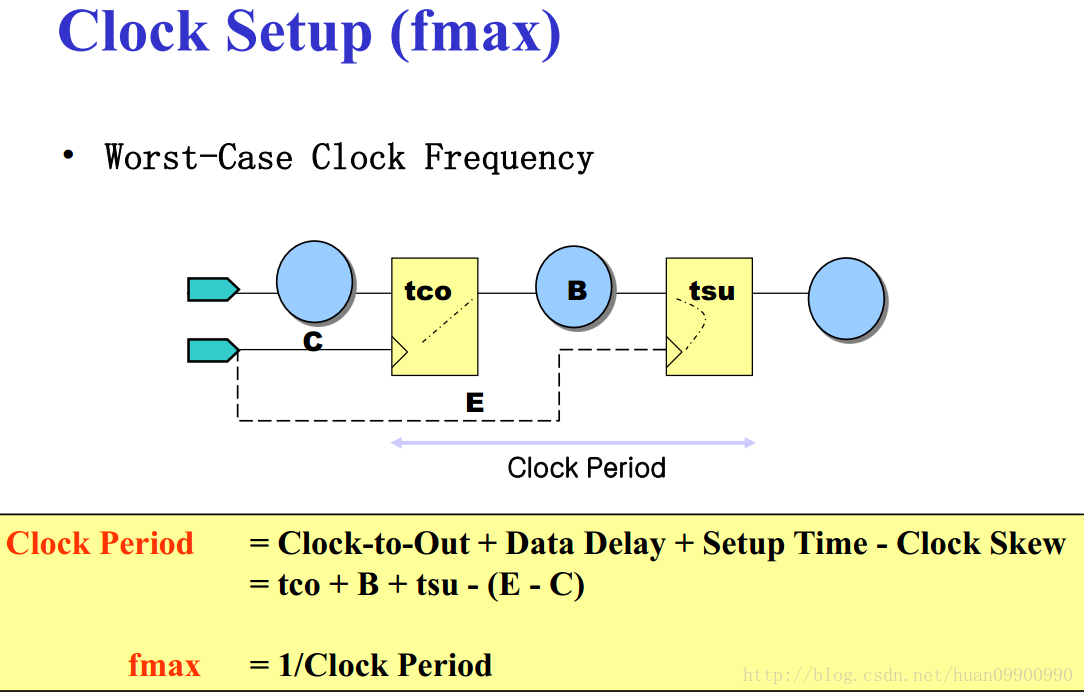

8、Fmax

指設計能運行的最高頻率,即周期為最小時,頻率最大

當Setup Slack=0時,系統剛好滿足建立時間,此時周期為最小值。

period=tco+data_delay+tsu-tskew

編輯:hfy

-

FPGA

+關注

關注

1629文章

21729瀏覽量

603016 -

寄存器

+關注

關注

31文章

5336瀏覽量

120232

發布評論請先 登錄

相關推薦

FPGA驅動AD芯片之實現與芯片通信

使用modelsim時的問題分析

時序邏輯電路故障分析

FPGA如何估算分析功耗

FPGA 高級設計:時序分析和收斂

Xilinx FPGA編程技巧之常用時序約束詳解

FPGA工程的時序約束實踐案例

Xilinx FPGA編程技巧之常用時序約束詳解

fpga仿真文件怎么寫

淺析FPGA的調試-內嵌邏輯分析儀(SignalTap)原理及實例

FPGA quartus ii里的靜態時序分析

FPGA quartus ii里的靜態時序分析

評論