一、簡(jiǎn)介

RapidIO是由Motorola和Mercury等公司率先倡導(dǎo)的一種高性能、 低引腳數(shù)、 基于數(shù)據(jù)包交換的互連體系結(jié)構(gòu),是為滿足和未來高性能嵌入式系統(tǒng)需求而設(shè)計(jì)的一種開放式互連技術(shù)標(biāo)準(zhǔn)。RapidIO主要應(yīng)用于嵌入式系統(tǒng)內(nèi)部互連,支持芯片到芯片、板到板間的通訊,可作為嵌入式設(shè)備的背板(Backplane)連接。

RapidIO協(xié)議由邏輯層、傳輸層和物理層構(gòu)成。邏輯層定義了所有協(xié)議和包格式。這是對(duì)終端進(jìn)行初始化和完成傳送的很有必要的信息。傳輸層為數(shù)據(jù)包從一個(gè)終端到另一個(gè)終端通道的必要信息。物理層描述了設(shè)備之間接口協(xié)議,例如包傳裝置,流量控制,電特性及低級(jí)錯(cuò)誤管理等。Rapid IO分為并行Rapid IO標(biāo)準(zhǔn)和串行Rapid IO標(biāo)準(zhǔn),串行RapidIO是指物理層采用串行差分模擬信號(hào)傳輸?shù)腞apidIO標(biāo)準(zhǔn)。

RapidIO行業(yè)協(xié)會(huì)成立于2000年,其宗旨是為嵌入式系統(tǒng)開發(fā)可靠的、 高性能、 基于包交換的互連技術(shù),2001 年正式發(fā)表其基本的規(guī)范。2003 年10 月,國際標(biāo)準(zhǔn)組織(ISO)和國際電工委員會(huì)(IEC)一致通過了RapidIO互連規(guī)范,即ISO/IEC DIS 18372,這使RapidIO(ISO)成為嵌入式互連技術(shù)方面得到授權(quán)的唯一標(biāo)準(zhǔn)。

RapidIO 的規(guī)范發(fā)布?xì)v史如下:

2001年3月,發(fā)布RapidIO 1.1規(guī)范;

2002年6月,發(fā)布RapidIO 1.2規(guī)范;

2005年2月,發(fā)布RapidIO 1.3規(guī)范;

2007年6月,發(fā)布RapidIO 2.0規(guī)范;

2009年8月,發(fā)布RapidIO 2.1規(guī)范;

2011年5月,發(fā)布RapidIO 2.2規(guī)范。

RapidIO 1.x標(biāo)準(zhǔn)支持的信號(hào)速率為1.25GHz、2.5GHz和3.125GHz;RapidIO 2.x標(biāo)準(zhǔn)在兼容Rapid IO 1.x標(biāo)準(zhǔn)基礎(chǔ)上,增加了支持5GHz和6.25GHz的傳輸速率 。

RapidIO 已有超過10 年的歷史,仍然生機(jī)勃勃,它還在繼續(xù)為開發(fā)人員提供高速、先進(jìn)的通訊技術(shù):可對(duì)許多集成電路、板卡、背板及計(jì)算機(jī)系統(tǒng)供應(yīng)商提供支持,支持RapidIO 標(biāo)準(zhǔn)的廠商有:Mercury Computer Systems、Freescale Semiconductor、Lucent-Alcatel、PMC-Sierra、Texas Instruments、Tundra Semiconductor、WindRiver、AMCC、Curtiss-Wright Controls、GE Fanuc 等,也就是說世界上幾乎所有的嵌入式主流廠商都已經(jīng)支持RapidIO 技術(shù),顯然,RapidIO 勢(shì)在必行。發(fā)展至今,開發(fā)人員有100 多種基于RapidIO 的產(chǎn)品可供選擇,這些產(chǎn)品涵蓋了各種開發(fā)工具、嵌入式系統(tǒng)、IP、軟件、測(cè)試與測(cè)量設(shè)備及半導(dǎo)體(ASIC、DSP、FPGA)等。

二、其他協(xié)議相比較

隨著高性能嵌入式系統(tǒng)的不斷發(fā)展,芯片間及板間互連對(duì)帶寬、成本、靈活性及可靠性的要求越來越高,傳統(tǒng)的互連方式,如處理器總線、PCI總線和以太網(wǎng),都難以滿足新的需求 。

處理器總線主要用作外部存儲(chǔ)器接口,如德州儀器(TI) C6000系列DSP的外部存儲(chǔ)器接口,可支持外接同步SDRAM、SBSRAM及FIFO,也可支持異步SRAM、FLASH等。外部存儲(chǔ)器接口也可用作與板內(nèi)FPGA或ASIC芯片互連,這種情況下,F(xiàn)PGA或ASIC模擬一個(gè)DSP支持的存儲(chǔ)器接口,DSP則把FPGA或ASIC當(dāng)作存儲(chǔ)器來訪問。這類同步接口帶寬可達(dá)10Gbps,如德州儀器TMS320C6455 DSP的DDR2接口最大帶寬為17.066Gbps,SBSRAM接口最大帶寬為8.533Gbps。

然而,這種接口也存在一些局限性:

① 接口管腳多,硬件設(shè)計(jì)困難。常見的DDR2接口有70~80個(gè)管腳;

② 只能用于板內(nèi)互連,無法用于板間互連;

③ 不是點(diǎn)對(duì)點(diǎn)的對(duì)等互連,DSP始終是主設(shè)備,其它器件只能做從設(shè)備。

PCI是廣泛用于計(jì)算機(jī)內(nèi)器件互連的技術(shù)。傳統(tǒng)PCI技術(shù)也采樣類似于上述存儲(chǔ)器接口的并行總線方式,如TMS320C6455 DSP的PCI接口,有32bits數(shù)據(jù)總線,最高時(shí)鐘速度為66MHz,共有42個(gè)管腳。最新的串行PCI Express技術(shù)采用與串行RapidIO(SRIO, Serial RapidIO)類似的物理層傳輸技術(shù),使得帶寬達(dá)到10Gbps左右。但由于其主要的應(yīng)用仍是計(jì)算機(jī),而且為了兼容傳統(tǒng)PCI技術(shù),使得它在嵌入式設(shè)備方面的應(yīng)用具有一定的局限性,如不支持點(diǎn)對(duì)點(diǎn)對(duì)等通信等。

眾所周知,以太網(wǎng)是使用最廣泛的局域網(wǎng)互連技術(shù),它也被擴(kuò)展應(yīng)用到嵌入式設(shè)備互連,但它的局限性也是顯而易見的:

① 不支持硬件糾錯(cuò),軟件協(xié)議棧開銷較大;

② 打包效率低,有效傳輸帶寬因此而減小;

③ 只支持消息傳輸模式,不支持對(duì)對(duì)端設(shè)備的直接存儲(chǔ)器訪問(DMA, Direct Memory Access)。

針對(duì)嵌入式系統(tǒng)的需求以及傳統(tǒng)互連方式的局限性,RapidIO標(biāo)準(zhǔn)按如下目標(biāo)被制定:

① 針對(duì)嵌入式系統(tǒng)機(jī)框內(nèi)高速互連應(yīng)用而設(shè)計(jì)。

② 簡(jiǎn)化協(xié)議及流控機(jī)制,限制軟件復(fù)雜度,使得糾錯(cuò)重傳機(jī)制乃至整個(gè)協(xié)議棧易于用硬件實(shí)現(xiàn)。

③ 提高打包效率,減小傳輸時(shí)延。

④ 減少管腳,降低成本。

⑤ 簡(jiǎn)化交換芯片的實(shí)現(xiàn),避免交換芯片中的包類型解析。

⑥ 分層協(xié)議結(jié)構(gòu),支持多種傳輸模式,支持多種物理層技術(shù),靈活且易于擴(kuò)展。

三、協(xié)議的三層結(jié)構(gòu)

為了滿足靈活性和可擴(kuò)展性的要求,RapidIO協(xié)議分為三層:邏輯層、傳輸層和物理層。

和以太網(wǎng)一樣,RapidIO也是基于包交換的互連技術(shù)。如圖3所示,RapidIO包由包頭、可選的載荷數(shù)據(jù)和16bits CRC校驗(yàn)組成。包頭的長(zhǎng)度因?yàn)榘愋筒煌赡苁鞘畮椎蕉畮讉€(gè)字節(jié)。每包的載荷數(shù)據(jù)長(zhǎng)度不超過256字節(jié),這有利于減少傳輸時(shí)延,簡(jiǎn)化硬件實(shí)現(xiàn)。

上述包格式定義兼顧了包效率及組包/解包的簡(jiǎn)單性。RapidIO交換器件僅需解析前后16bits,以及源/目地器件ID,這簡(jiǎn)化了交換器件的實(shí)現(xiàn)。

邏輯層協(xié)議

邏輯層定義了操作協(xié)議和相應(yīng)的包格式。RapidIO支持的邏輯層業(yè)務(wù)主要是:直接IO/DMA (Direct IO/Direct Memory Access)和消息傳遞(Message Passing)。

直接IO/DMA模式是最簡(jiǎn)單實(shí)用的傳輸方式,其前提是主設(shè)備知道被訪問端的存儲(chǔ)器映射。在這種模式下,主設(shè)備可以直接讀寫從設(shè)備的存儲(chǔ)器。直接IO/DMA在被訪問端的功能往往完全由硬件實(shí)現(xiàn),所以被訪問的器件不會(huì)有任何軟件負(fù)擔(dān)。從功能上講,這一特點(diǎn)和德州儀器DSP的傳統(tǒng)的主機(jī)接口(HPI, Host Port Interface)類似。但和HPI口相比,SRIO(Serial RapidIO)帶寬大,管腳少,傳輸方式更靈活。

對(duì)上層應(yīng)用來說,發(fā)起直接IO/DMA傳輸主要需提供以下參數(shù):目地器件ID、數(shù)據(jù)長(zhǎng)度、數(shù)據(jù)在目地器件存儲(chǔ)器中的地址。

直接IO/DMA模式又可進(jìn)一步分為以下幾種傳輸格式:

① NWRITE: 寫操作,不要求接收端響應(yīng)。

② NWRITE_R: 帶響應(yīng)的NWRITE(NWRITE with Response),要求接收端響應(yīng)。

③ SWRITE:流寫(Stream Write),數(shù)據(jù)長(zhǎng)度必須是8字節(jié)的整數(shù)倍,不要求接收端響應(yīng)。

④ NREAD: 讀操作。

SWRITE是最高效的傳輸格式;帶響應(yīng)的寫操作或讀操作效率則較低,一般只能達(dá)到不帶響應(yīng)的傳輸?shù)男实囊话搿?/p>

消息傳遞(Message Passing)模式則類似于以太網(wǎng)的傳輸方式,它不要求主設(shè)備知道被訪問設(shè)備的存儲(chǔ)器狀況。數(shù)據(jù)在被訪問設(shè)備中的位置則由郵箱號(hào)(類似于以太網(wǎng)協(xié)議中的端口號(hào))確定。從設(shè)備根據(jù)接收到的包的郵箱號(hào)把數(shù)據(jù)保存到對(duì)應(yīng)的緩沖區(qū),這一過程往往無法完全由硬件實(shí)現(xiàn),而需要軟件協(xié)助,所以會(huì)帶來一些軟件負(fù)擔(dān)。

對(duì)上層應(yīng)用來說,發(fā)起消息傳遞主要需提供以下參數(shù):目地器件ID、數(shù)據(jù)長(zhǎng)度、郵箱號(hào)。

傳輸層協(xié)議

RapidIO是基于包交換的互連技術(shù),傳輸層定義了包交換的路由和尋址機(jī)制。

RapidIO網(wǎng)絡(luò)主要由兩種器件,終端器件(End Point)和交換器件(Switch)組成。終端器件是數(shù)據(jù)包的源或目的地,不同的終端器件以器件ID來區(qū)分。RapidIO支持8 bits 或 16 bits器件ID,因此一個(gè)RapidIO網(wǎng)絡(luò)最多可容納256或65536個(gè)終端器件。與以太網(wǎng)類似,RapidIO也支持廣播或組播,每個(gè)終端器件除了獨(dú)有的器件ID外,還可配置廣播或組播ID。交換器件根據(jù)包的目地器件ID進(jìn)行包的轉(zhuǎn)發(fā),交換器件本身沒有器件ID。

RapidIO的互連拓?fù)浣Y(jié)構(gòu)非常靈活,除了通過交換器件外,兩個(gè)終端器件也可直接互連。以德州儀器(TI)的TMS320C6455 DSP為例,它有4個(gè)3.125G的SRIO口,它可支持的拓?fù)浣Y(jié)構(gòu)

物理層協(xié)議

RapidIO 1.x 協(xié)議定義了以下兩種物理層接口標(biāo)準(zhǔn):

① 8/16 并行LVDS協(xié)議

② 1x/4x 串行協(xié)議 (SRIO)

并行RapidIO由于信號(hào)線較多(40~76)難以得到廣泛的應(yīng)用,而1x/4x串行RapidIO僅4或16個(gè)信號(hào)線,逐漸成為主流,所以本文僅介紹串行RapidIO。

串行RapidIO基于現(xiàn)在已廣泛用于背板互連的SerDes(Serialize Deserialize)技術(shù),它采用差分交流耦合信號(hào)。差分交流耦合信號(hào)具有抗干擾強(qiáng)、速率高、傳輸距離較遠(yuǎn)等優(yōu)點(diǎn)。差分交流耦合信號(hào)的質(zhì)量不是由傳統(tǒng)的時(shí)序參數(shù)來衡量,而是通過眼圖來衡量,眼圖中的“眼睛”張得越開則信號(hào)質(zhì)量越好。

下圖是一個(gè)典型的串行RapidIO信號(hào)的眼圖。

差分信號(hào)的強(qiáng)弱由一對(duì)信號(hào)線的電壓差值表示,串行RapidIO協(xié)議規(guī)定信號(hào)峰-峰值的范圍是200mV-2000mV。信號(hào)幅度越大,則傳輸距離越遠(yuǎn),RapidIO協(xié)議按信號(hào)傳輸距離定義兩種傳輸指標(biāo):

① 短距離傳輸(Short Run),<=50厘米,主要用于板內(nèi)互連,推薦的發(fā)送端信號(hào)峰-峰值為500mV-1000mV

② 長(zhǎng)距離傳輸(Long Run),>50厘米,主要用于板間或背板互連,推薦的發(fā)送端信號(hào)峰-峰值為800mV-1600mV

為了支持全雙工傳輸,串行RapidIO收發(fā)信號(hào)是獨(dú)立的,所以每一個(gè)串行RapidIO口由4根信號(hào)線組成。標(biāo)準(zhǔn)的1x/4x 串行RapidIO接口,支持四個(gè)口,共16根信號(hào)線。這四個(gè)口可被用作獨(dú)立的接口傳輸不同的數(shù)據(jù);也可合并在一起當(dāng)作一個(gè)接口使用,以提高單一接口的吞吐量。

德州儀器TMS320C6455 DSP上集成了標(biāo)準(zhǔn)的1x/4x串行RapidIO接口,如圖

發(fā)送時(shí),邏輯層和傳輸層將組好的包經(jīng)過CRC編碼后被送到物理層的FIFO中,“8b/10b編碼”模塊將每8bit數(shù)據(jù)編碼成10bits數(shù)據(jù),“并/串轉(zhuǎn)換”模塊將10bits并行數(shù)據(jù)轉(zhuǎn)換成串行bits,發(fā)送模塊把數(shù)字bit轉(zhuǎn)換成差分交流耦合信號(hào)在信號(hào)線上發(fā)送出去。

這里的8b/10編碼的主要作用是:

① 保證信號(hào)有足夠的跳變,以便于接收方恢復(fù)時(shí)鐘。串行RapidIO沒有專門的時(shí)鐘信號(hào)線,接收端靠數(shù)據(jù)信號(hào)的跳變恢復(fù)時(shí)鐘。所以需要把信號(hào)跳變少的8bits數(shù)據(jù)(如全0或全1)編碼成有一定跳變的10bits數(shù)據(jù)。另外,也使得總體數(shù)據(jù)中0和1的個(gè)數(shù)均衡,以消除直流分量,保證交流耦合特性;

② 8b/10編碼可擴(kuò)大符號(hào)空間,以承載帶內(nèi)控制符號(hào)。10bits能表示1024個(gè)符號(hào),其中256個(gè)表示有效的8bits數(shù)據(jù),剩下的符號(hào)中的幾十個(gè)被用作控制符號(hào)。控制符號(hào)可被用作包分隔符,響應(yīng)標(biāo)志,或用于鏈路初始化,鏈路控制等功能;

③ 8b/10編碼能實(shí)現(xiàn)一定的檢錯(cuò)功能。1024個(gè)符號(hào)中,除了256個(gè)有效數(shù)據(jù)符號(hào)和幾十個(gè)控制符號(hào)外,其它符號(hào)都是非法的,接收方收到非法符號(hào)則表示鏈路傳輸出錯(cuò)。

接收的過程則正好相反,首先接收方需要根據(jù)數(shù)據(jù)信號(hào)的跳變恢復(fù)出時(shí)鐘,用這個(gè)時(shí)鐘采樣串行信號(hào),將串行信號(hào)轉(zhuǎn)換為10bits的并行信號(hào),再按8b/10b編碼規(guī)則解碼得到8bits數(shù)據(jù),最后做CRC校驗(yàn)并送上層處理。

數(shù)據(jù)被正確的接收時(shí),接收端會(huì)發(fā)送一個(gè)ACK響應(yīng)包給發(fā)送端;如果數(shù)據(jù)不正確(CRC錯(cuò)或非法的10bits符號(hào)),則會(huì)送NACK包,要求發(fā)送方重傳。這種重傳糾錯(cuò)的功能由物理層完成,而物理層功能往往由硬件實(shí)現(xiàn),所以不需要軟件干預(yù)。

串行RapidIO支持的信號(hào)速率有三種:1.25GHz,2.5GHz,3.125GHz。但由于8b/10b編碼,其有效數(shù)據(jù)速率分別為:1Gbps, 2Gbps, 2.5Gbps。 4個(gè)1x端口或一個(gè)4x端口支持的最高速率為10Gbps。

四、xlinx srio ip介紹

Endpoint IP由物理層、傳輸層及邏輯層組成,自帶可配置buffer design、reference clock module、reset module及configuration fabric referencedesign。支持1x、2x、4x lane widths,支持per-lane speeds of 1.25、2.5、3.125、5.0及6.25Gbaud。SRIO Gen2使用AXI4-Stream接口用于高速數(shù)據(jù)傳輸。

邏輯層定義了操作協(xié)議和包格式。

傳輸層提供端點(diǎn)器件間傳輸包所需的路由信息。

物理層定義器件級(jí)接口的細(xì)節(jié),如包傳輸機(jī)制、流量控制、電氣特性和低級(jí)錯(cuò)誤管理。

1. 1SRIO系統(tǒng)預(yù)覽

2. 邏輯層接口介紹

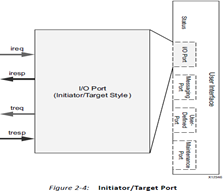

由圖一可以看到邏輯層有三種接口:ConfigurationFabric Interface,具體如下:

User Interface

主要包含一系列I/O ports和三類可選的ports,主要是用來發(fā)包和收包解析。對(duì)于使用哪些接口,在FPGA開發(fā)過程中,可以在IP core進(jìn)行配置,實(shí)現(xiàn)時(shí),每種事物根據(jù)事物的類型接入對(duì)應(yīng)的port中。

其中,任何支持I/O事物傳輸?shù)亩紝⒃贗/O ports收發(fā),如NWRITEs、NWRITE_Rs、SWRITEs、NREADs和RESPONSEs等事物;MESSAGE事物則可以在I/O ports傳輸,也可以在專用的messaging port傳輸;DOORBELL事物不管有沒有message port,都將使用IO port進(jìn)行傳輸;如果定義了maintenance接口,那么maintenance事物將通過maintenance接口進(jìn)行傳輸;如果使用了User-defined接口的話,那么用戶自定義的、系統(tǒng)不支持的或者未指明接口的事物將可以采用這種User-defined接口,如果未使能User-defined接口,那么上面提到這3種事物包將被丟棄。

必備的I/O Port

IO port支持2種格式:HELLO format 和SRIOstream。對(duì)于模式和包格式的選擇都需要在創(chuàng)建IPcore的時(shí)候選定好,并且IO ports里面所有的channels都必須使用相同的包格式。

IO ports配置成condensedIO模式主要是為了減少channels數(shù),此時(shí)只有一個(gè)AXI4-stream 用來收發(fā)數(shù)據(jù)。在這種模式下,SRIO的IO port很接近于PCIE的AXI總線。(注意端口命名的參考是LOG層).

initiator/Target允許在遠(yuǎn)端的initiator發(fā)起事物并把本地的endpoint作為事物傳送目標(biāo)。從下面其接口圖可以看出,其實(shí)感覺有點(diǎn)類似IIC,規(guī)定什么時(shí)候誰為master,向slave發(fā)起操作,故具備了2套獨(dú)立的AXI4-stream用來收發(fā)數(shù)據(jù)。

s_axis_ireq* are associated with INITIATOR_IREQ.

m_axis_iresp* are associated with INITIATOR_IRESP.

m_axis_treq* are associated with TARGET_TREQ.

s_axis_tresp* are associated with TARGET_TRESP.

可選的Messaging Port

為什么是可選的呢,因?yàn)閙essage也可以作為普通的wrtie事物通過I/O prot進(jìn)行傳輸,IP core 產(chǎn)生時(shí)可以對(duì)這個(gè)進(jìn)行選擇。默認(rèn)是和I/O port復(fù)用的,但是如果作為獨(dú)立的port也是可以的,接口類型和initiator/Target一樣。

可選的Maintenance Port

雖然說這個(gè)是可選的,可是在xilinx的IP core配置上,這個(gè)好像是一定存在的,并且還被推薦配置成AXI4-Liteinterface,當(dāng)然也可以配置成AXI4-Stream。這2種interface的區(qū)別主要在于AXI4-Lite interface不僅可以讓用戶app target本地的配置空間,還可以target遠(yuǎn)端的配置空間,而AXI4-Stream interface只能配置遠(yuǎn)端的配置空間。

可選的User-Defined Port

User-definedport采用的是SRIO stream format,并且擁有2個(gè)AXI4-Stream channels。

3. BUF接口垃圾桶

BUF層夾雜在LOG層和PHY層中間,為包的傳送和流控制提供了保證。當(dāng)然收發(fā)的buffer大小是可配的,值得注意的是,這里說的大小不是說fifo size或深度之類的,而是max sized packets的個(gè)數(shù),即按最大size包的個(gè)數(shù)進(jìn)行管理的。

上面的和LOG和PHY層的interface是AXI4-Stream,而cfgb則是AXI4-Liteinterface接口,實(shí)現(xiàn)進(jìn)入BUF層的配置空間。

該層主要包含以下一些接口:

(1)clock andresetinterface

(2)transport interface

(3)link interface

(4)BUF configurationfabric interface

4. 物理層接口

RapidIO串行物理層,通常稱為串行RapidIO,針對(duì)板上或通過背板的器件間的電氣連接。串行物理層定義器件間的全雙工串行鏈路,在每個(gè)方向上使用單向差分信號(hào)。RapidIO串行物理層支持RapidIO器件間的包傳送,包括包和控制符號(hào)的傳送、流量控制、錯(cuò)誤管理和其他器件到器件的功能。

由于串行RapidIO規(guī)范僅在物理層定義(RapidIO技術(shù)定于物理層為電氣接口和器件到器件的鏈路協(xié)議),多數(shù)RapidIO控制器的邏輯是相同的。因此,串行RapidIO規(guī)范保留了許多已有的設(shè)計(jì)經(jīng)驗(yàn)和經(jīng)過證實(shí)的基礎(chǔ)結(jié)構(gòu),簡(jiǎn)化了并行與串行鏈路間的系統(tǒng)級(jí)交換操作。

RapidIO串行物理層有如下特征:

(1)采用8B/10B編碼方案將發(fā)送時(shí)鐘嵌入到數(shù)據(jù)中;

(2)在每個(gè)方向上支持一個(gè)串行差分對(duì),稱為1通道;或支持四個(gè)并列的串行差分對(duì),稱為4通道;

(3)使用專用的8B/10B碼來管理鏈路,管理內(nèi)容包括流量控制、包定界和錯(cuò)誤報(bào)告;

(4)允許在RapidIO1x/4xLP-Serial(串行RapidIO)端口和RapidIO物理層8/16 LP-LVDS(并行RapidIO)端口之間進(jìn)行包傳輸而無需包處理;

(5)使用與并行RapidIO物理層相似的重傳和錯(cuò)誤恢復(fù)協(xié)議;

(6)支持每通道1.25G、2.5G和3.125G波特率(數(shù)據(jù)流為1.0Gbps、2.0Gbps和2.5Gbps)的傳送速率。(現(xiàn)在支持的應(yīng)該更多了,可以高達(dá)6.25G了)

該層主要包含以下一些接口:

(1)clock and reset interface

(2)link interface

(3)serial interface

(4)control and statusinterface

(5)configuration fabricinterface

(6)serial transceiversinterface

(7)configuration fabricreference design interface

五、xlinx srio ip

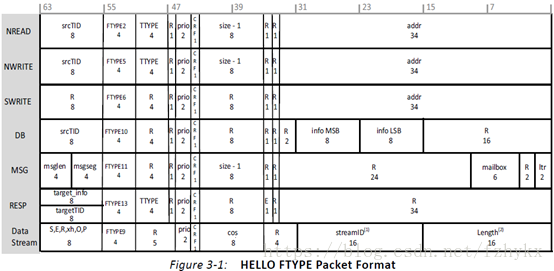

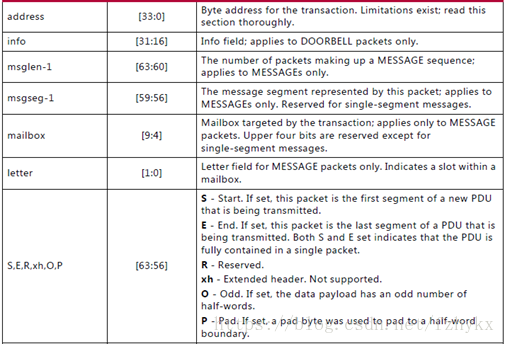

在利用Xilinx的IP進(jìn)行開發(fā)時(shí),為了簡(jiǎn)化報(bào)文的解析和組包,SRIO Gen2 usesAXI4-Stream,Xilinx推出了一種簡(jiǎn)化的報(bào)文格式,這樣一來,我們可以發(fā)現(xiàn),這樣又很接近PCIE的TLP報(bào)文格式了。

lHELLO format

引腳示意:

編輯:hfy

-

嵌入式系統(tǒng)

+關(guān)注

關(guān)注

41文章

3587瀏覽量

129436 -

RapidIO

+關(guān)注

關(guān)注

1文章

39瀏覽量

20807 -

PCI

+關(guān)注

關(guān)注

4文章

663瀏覽量

130251 -

存儲(chǔ)器接口

+關(guān)注

關(guān)注

0文章

16瀏覽量

7951 -

嵌入式設(shè)備

+關(guān)注

關(guān)注

0文章

110瀏覽量

16955

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

新手怎么學(xué)嵌入式?

嵌入式系統(tǒng)開發(fā)與硬件的關(guān)系 嵌入式系統(tǒng)開發(fā)常見問題解決

嵌入式系統(tǒng)的原理和應(yīng)用

嵌入式系統(tǒng)的體系結(jié)構(gòu)包括哪些

嵌入式常用數(shù)據(jù)結(jié)構(gòu)有哪些

嵌入式系統(tǒng)怎么學(xué)?

如何提升嵌入式編程能力?

嵌入式系統(tǒng)軟硬件基礎(chǔ)知識(shí)大全

深度詳解嵌入式系統(tǒng)專用輕量級(jí)框架設(shè)計(jì)

嵌入式系統(tǒng) RapidIO協(xié)議結(jié)構(gòu)詳解

嵌入式系統(tǒng) RapidIO協(xié)議結(jié)構(gòu)詳解

評(píng)論