DDR對(duì)于做項(xiàng)目來(lái)說(shuō),是必不可少的。一般用于數(shù)據(jù)緩存和平滑帶寬。今天介紹下Xilinx DDR控制器MIG IP核的例化及仿真。

開發(fā)工具:Vivado 2014.4

1、IP Catalog中搜索MIG,點(diǎn)擊相應(yīng)IP進(jìn)入如下配置界面。

(1)DDR控制器的個(gè)數(shù),根據(jù)你的實(shí)際需求而定,需要幾個(gè)控制器,你心里應(yīng)該清楚吧。

(2)MIG IP核的用戶側(cè)接口,選擇AXI4。基本上,Xilinx的IP都提供了AXI標(biāo)準(zhǔn)接口,所以,控制Xilinx的IP,要先學(xué)會(huì)AXI協(xié)議。

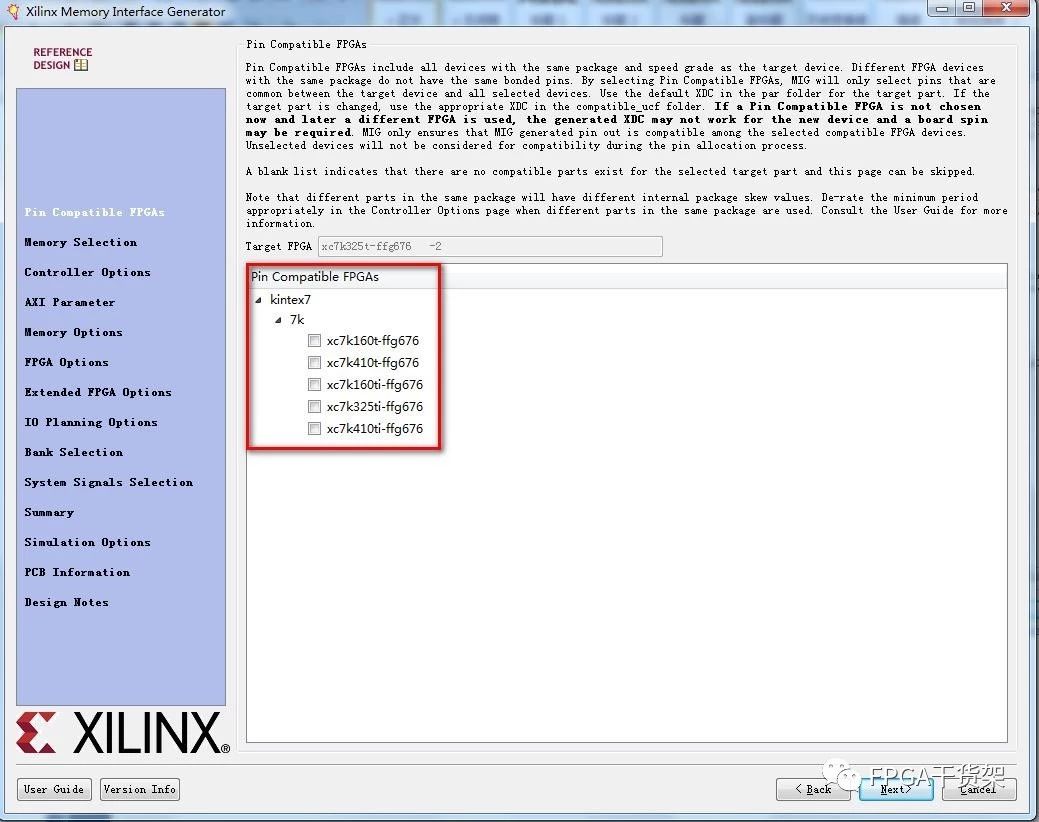

2、點(diǎn)擊Next,進(jìn)入下一配置頁(yè)面,這里選擇是否兼容其他相同封裝的芯片,看實(shí)際需求,一般默認(rèn),直接Next。

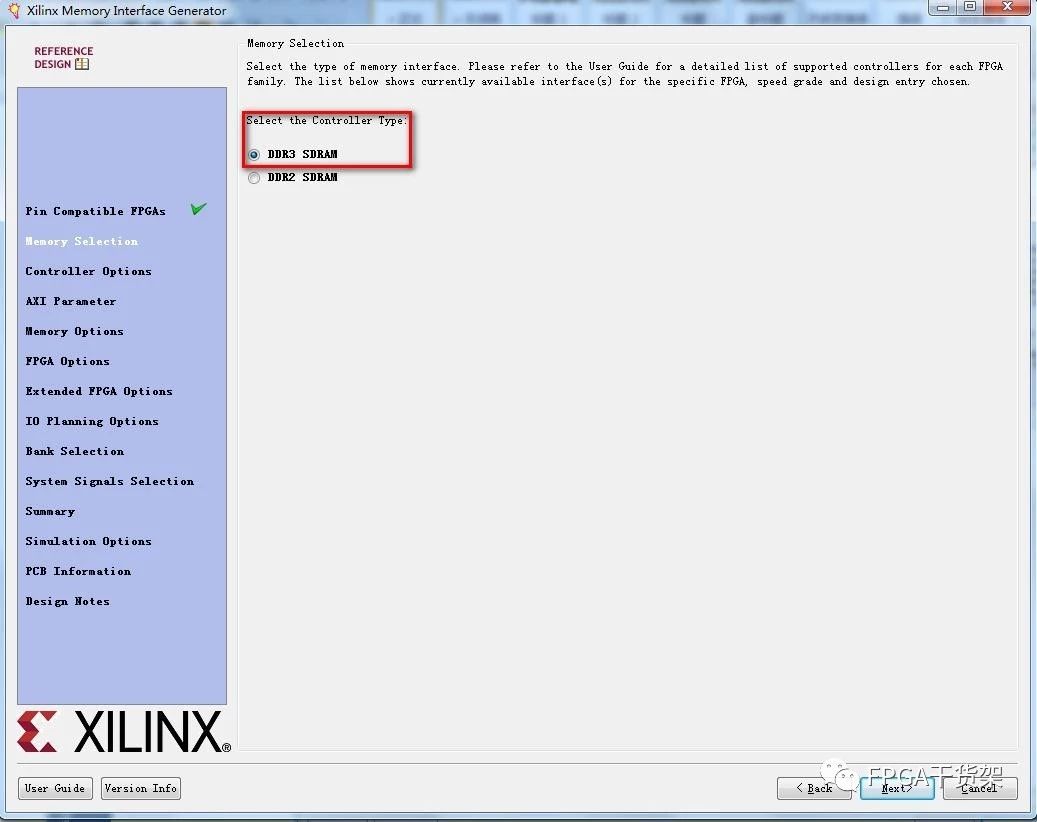

3、選擇控制器類型,是DDR3還是DDR2,你自己的芯片是DDR幾就選幾。

4、下面的配置很重要。

(1)400MHz是DDR芯片實(shí)際跑的時(shí)鐘頻率,這個(gè)要看硬件設(shè)計(jì)是多少了。時(shí)鐘周期范圍1112ns~3300ns。

(2)4:1是DDR時(shí)鐘頻率:MIG控制器用戶側(cè)的用戶時(shí)鐘頻率。若DDR時(shí)鐘頻率是400MHz,則用戶時(shí)鐘頻率為100MHz。

(3)Components指的是DDR3的型號(hào)是元件類,而不是像筆記本那種的插條類(SODIMMs)。

(4)DDR的型號(hào)。

(5)DDR的位寬。

(6)DDR控制器會(huì)調(diào)度命令的順序,當(dāng)選擇strict時(shí),嚴(yán)格按照命令先后順序執(zhí)行;選擇normal時(shí),為了得到更高的效率,可能對(duì)命令重排序。為了操作簡(jiǎn)單,我們選擇strict。

5、下面是AXI相關(guān)參數(shù)的配置,也很重要。

(1)AXI接口的數(shù)據(jù)位寬。

(2)MIG控制器的仲裁機(jī)制,讀優(yōu)先或者寫優(yōu)先。

(3)Narrow Burst支持,disable。

(4)AXI接口的地址位寬。

(5)AXI讀寫通道的ID寬度。ID用來(lái)標(biāo)識(shí)是寫響應(yīng)和寫數(shù)據(jù)的一致性。

6、配置同樣重要。

(1)輸入系統(tǒng)參考時(shí)鐘頻率。

(2)Burst讀寫類型為順序讀寫,不選交叉讀寫。

(3)DDR和AXI總線之間的地址映射。涉及到DDR的操作效率。

7、配置不當(dāng),將直接導(dǎo)致無(wú)法生成IP。

(1)系統(tǒng)時(shí)鐘,可以選差分、單端、No Buffer,根據(jù)實(shí)際情況選。

(2)參考時(shí)鐘,可以和系統(tǒng)時(shí)鐘共用,選擇No Buffer。

(3)系統(tǒng)復(fù)位極性,根據(jù)實(shí)際情況選。

10、仿真

每次涉及到仿真官方提供的IP時(shí),都要詬病一下Altera做的多難用,Xilinx做的多人性化。Xilinx針對(duì)IP的仿真,只需要在生成IP后,點(diǎn)擊個(gè)Open Example Design即可,而腦殘的Altera非要給你整得特別復(fù)雜,非得你運(yùn)行個(gè)tcl腳本(這還算簡(jiǎn)單的呢),才能啟動(dòng)仿真,不能和Xilinx學(xué)學(xué)嗎?

對(duì)于K7的MIG IP核,啟動(dòng)仿真后,初始化完成大約在106us左右,要耐心等待啊,初始化完成是第一步,初始化完成了,才能有后續(xù),不然的話,老老實(shí)實(shí)先讓初始化拉高再說(shuō)吧。

編輯:hfy

-

FPGA

+關(guān)注

關(guān)注

1629文章

21729瀏覽量

603010 -

DDR

+關(guān)注

關(guān)注

11文章

712瀏覽量

65318 -

Xilinx

+關(guān)注

關(guān)注

71文章

2167瀏覽量

121305 -

MIG

+關(guān)注

關(guān)注

0文章

12瀏覽量

10979

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

mig生成的DDR的IP核的問(wèn)題

xilinx MIG DDR2使用問(wèn)題

例說(shuō)FPGA連載41:DDR控制器集成與讀寫測(cè)試之DDR2 IP核接口描述

MIG IP核管腳分配問(wèn)題

使用user design文件夾下的.v文件,如果編寫頂層讀寫控制程序?qū)?b class='flag-5'>mig-39-2.v進(jìn)行例化,如何操作才能使用sim_tb_top.v仿真文件?

基于FPGA的DDR3 SDRAM控制器的設(shè)計(jì)與優(yōu)化

Xilinx ISE中的DDR控制器是否有任何IP實(shí)現(xiàn)

如何在ML505板上移植DDR2控制器?

可以使用mig生成ddr控制器嗎?

如何調(diào)試Zynq UltraScale+ MPSoC VCU DDR控制器

XILINX MIG(DDR3) IP的AXI接口與APP接口的區(qū)別以及優(yōu)缺點(diǎn)對(duì)比

如何根據(jù)Xilinx官方提供的技術(shù)參數(shù)來(lái)實(shí)現(xiàn)對(duì)IP核的讀寫控制

Xilinx DDR2 IP 核控制器設(shè)計(jì)方案介紹與實(shí)現(xiàn)

DDR3 SDRAM的IP核調(diào)取流程

Xilinx DDR控制器MIG IP核的例化及仿真

Xilinx DDR控制器MIG IP核的例化及仿真

評(píng)論