1. 時鐘介紹

在數字設計中,時鐘代表從寄存器(register)到寄存器可靠傳輸數據的時間基準。Xilinx Vivado集成設計環境(IDE)時序引擎使用ClocK特征計算時序路徑要求,并通過松弛計算報告設計時序裕度(Slack)。

時鐘必須正確定義,以獲得最佳的時序路徑。以下特性定義了時鐘:

1,時鐘定義在它的樹根的驅動器管腳或端口上,被稱為源點。

2,時鐘的邊沿是由周期和波形特性相結合來描述的。

3,周期以納秒(ns)為單位,時鐘對應于波形重復的時間。

4,波形是時鐘周期內上升邊沿和下降邊沿絕對時間的列表,以納秒(ns)為單位。列表必須包含偶數的值。第一個值總是相對應的。到第一個上升的邊沿。除非另有規定,占空比默認為50%,相移到0ns。

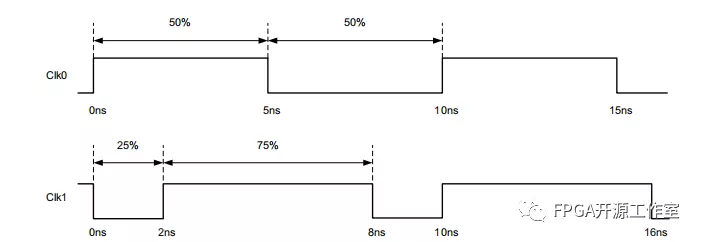

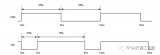

如圖1所示,時鐘CLK0具有10ns周期、50%占空比和0ns相位。時鐘CLK1具有8ns周期、75%占空比(8ns內的高電平時間為6ns)和2ns上升沿相位偏移。

Clk0: period = 10, waveform = {0 5}

Clk1: period = 8, waveform = {2 8}

圖1 時鐘波形示例

1.1 傳播時鐘(Propagated Clocks)

周期和波形屬性代表時鐘的理想特性。當進入FPGA并通過時鐘樹傳播時,時鐘邊沿被延遲并受到噪聲和硬件行為引起的變化的影響。這些特性稱為時鐘網絡延遲和時鐘不確定性。

時鐘的不確定性包括:

1,時鐘抖動(Clock jitter)

2,相位誤差

3,您指定的任何其他不確定性

默認情況下,Vivado IDE始終將時鐘視為傳播時鐘,即非理想時鐘,以便提供包括時鐘樹插入延遲和不確定性的準確松弛值。

1.2專用硬件資源

Xilinx FPGA的專用硬件資源有效支持大量設計時鐘。這些時鐘通常由電路板上的外部元件產生。它們通常通過輸入端口進入設備。

它們也可以由稱為時鐘修改塊的特殊原語生成,例如:

1,MMCM

2,BUFR

3,PLL

它們也可以通過常規單元格(如LUTS和寄存器)進行轉換。

2 主時鐘(Primary Clocks)

主時鐘是通過輸入端口或GT收發器輸出引腳(例如,恢復時鐘)進入設計的板時鐘。

主時鐘只能由create_clock命令定義。

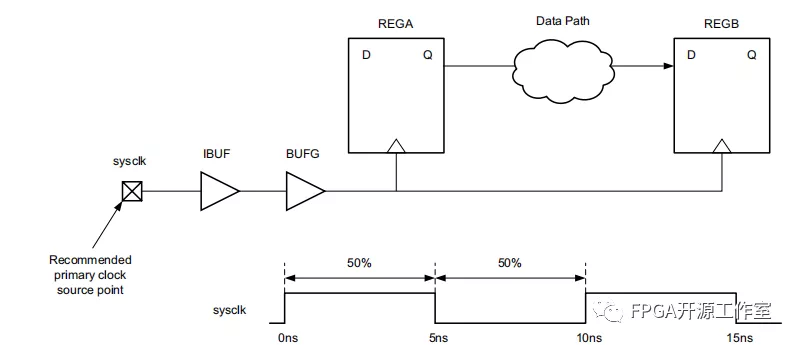

如圖2所示,板時鐘通過端口sysclk進入器件,然后在到達路徑寄存器之前通過輸入緩沖器和時鐘緩沖器傳播。

1,時鐘周期10ns

2,占空比50%

3,沒有相位偏移

相應的Xilinx設計約束(XDC):

create_clock -period 10 [get_ports sysclk]

圖2 主時鐘

與sysclk類似,板時鐘devclk通過端口clkIn進入設備。

1,時鐘周期10ns

2,占空比為25%

3,相位偏移90度

對應的XDC:

create_clock -name devclk -period 10 -waveform {2.5 5} [get_ports ClkIn]

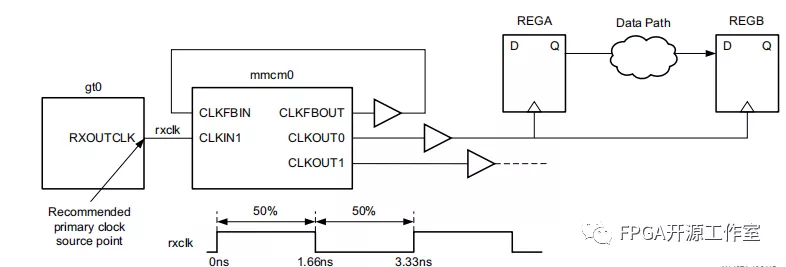

如圖3所示,展示了一個收發器gt0,它從電路板上的高速鏈路恢復時鐘rxclk。時鐘rxclk的周期為3.33 ns,占空比為50%,并被路由到MMCM,MMCM為設計生成多個補償時鐘。

對應的XDC:

create_clock -name sysclk -period 3.33 [get_ports SYS_CLK_clk_p]

圖3 GT主時鐘

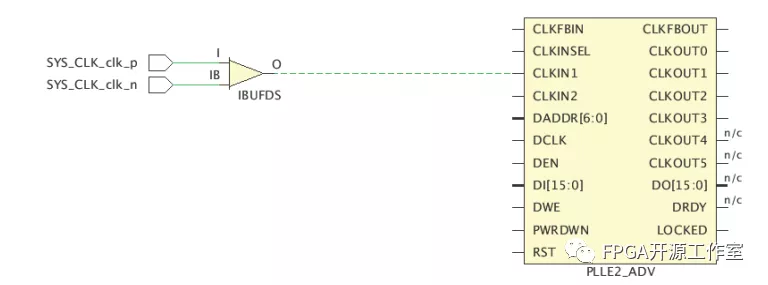

如圖4所示,差分緩沖器驅動PLL。在這種情況下,主時鐘只能在差分緩沖區的正輸入上創建。在緩沖區的每個正/負輸入上創建主時鐘將導致不切實際的CDC路徑。

相應的XDC:

create_clock -name sysclk -period 3.33 [get_ports SYS_CLK_clk_p]

圖4 差動緩沖器上的主時鐘

3虛擬時鐘( Virtual Clocks)

虛擬時鐘是指在設計中沒有物理連接到任何Netlist元素的時鐘。

虛擬時鐘是通過create_clock命令定義的,而不指定源對象。

虛擬時鐘通常用于在下列情況之一中指定輸入和輸出延遲約束:

1,外部設備I/O參考時鐘不是設計時鐘之一。

2,FPGA I / O路徑與內部生成的時鐘有關,該時鐘無法與從中導出的時鐘板正確計時。

3,希望只為與I/O延遲約束相關的時鐘指定不同的抖動和延遲,而不修改內部時鐘特性。

例如,時鐘CLK_virt的周期為10 ns,不附加到任何Netlist對象。未指定[]參數。在這種情況下,-name選項是強制性的.

相應的XDC:

create_clock -name clk_virt -period 10

在輸入和輸出延遲約束使用之前,必須定義虛擬時鐘

4 生成時鐘(Generated Clocks)

生成的時鐘由設計內部的特殊單元(稱為時鐘修改塊(例如,MMCM))或某些用戶邏輯驅動。

生成的時鐘與主時鐘相關聯。create_generated_clock命令考慮主時鐘的起始點。主時鐘可以是主時鐘或另一個生成時鐘。

生成的時鐘屬性直接來自其主時鐘。必須描述修改電路如何轉換主時鐘,而不是指定其周期或波形。

4.1 用戶定義產生時鐘

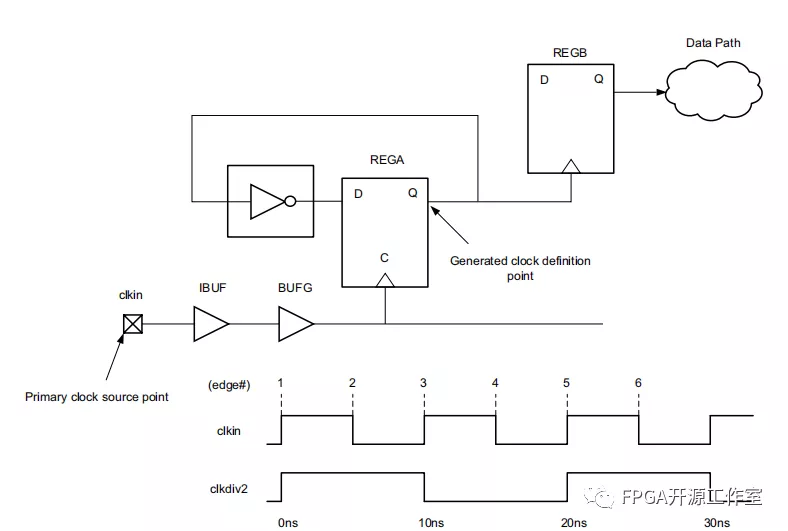

例1:一個簡單的二分頻

圖5 Generated Clocks

主時鐘clkin的周期為10 ns。寄存器REGA將其除以2,驅動其他寄存器時鐘引腳。相應的生成時鐘稱為clkdiv2。

以下是兩個同等的制約因素:

create_clock -name clkin -period 10 [get_ports clkin]

# Option 1: master clock source is the primary clock source point

create_generated_clock -name clkdiv2 -source [get_ports clkin] -divide_by 2 /

[get_pins REGA/Q]

# Option 2: master clock source is the REGA clock pin

create_generated_clock -name clkdiv2 -source [get_pins REGA/C] -divide_by 2 /

[get_pins REGA/Q]

例2:除以2使用-edges選項

以下示例等效于示例1中定義的生成時鐘:簡單除法2

# waveform specified with -edges instead of -divide_by

create_generated_clock -name clkdiv2 -source [get_pins REGA/C] -edges {1 3 5} / [get_pins REGA/Q]

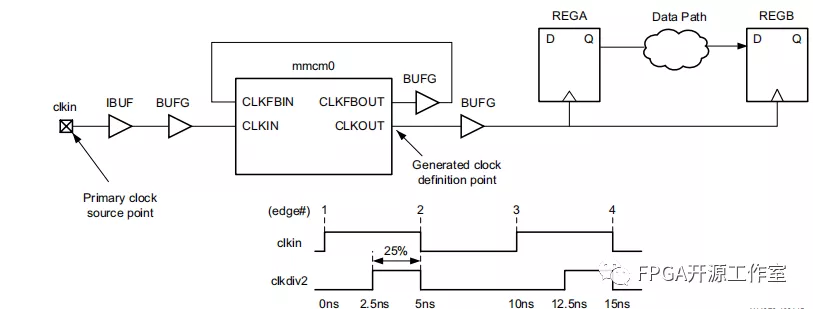

例3:使用-edges和-edge_shift選項進行占空比更改和相移

通過使用-edge_shift選項,生成的時鐘波形的每個邊沿也可以單獨移位正值或負值。僅在需要相移時才使用此選項。

-edge_shift選項不能與以下任何內容同時使用:

1,-divide_by

2,-multiply_by

3,-invert

考慮主時鐘clkin,周期為10 ns,占空比為50%。它到達單元mmcm0,產生一個占空比為25%的時鐘,移動90度。生成的時鐘定義指的是主時鐘邊沿1,2和3.這些邊沿分別出現在0ns,5ns和10ns。要獲得所需波形,請將第一個和第三個邊沿移動2.5ns。

create_clock -name clkin -period 10 [get_ports clkin]

create_generated_clock -name clkshift -source [get_pins mmcm0/CLKIN] -edges {1 2 3} / -edge_shift {2.5 0 2.5} [get_pins mmcm0/CLKOUT]

# First rising edge: 0ns + 2.5ns = 2.5ns

# Falling edge: 5ns + 0ns = 5ns

# Second rising edge: 10ns + 2.5ns = 12.5ns

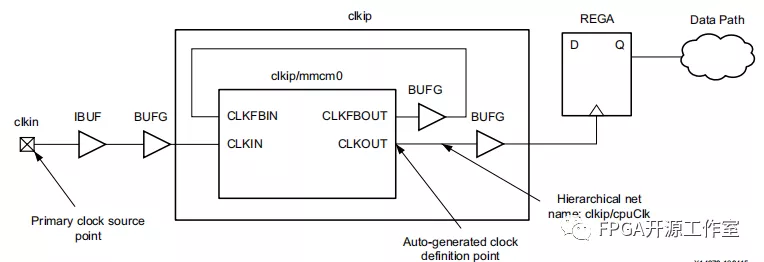

4.2 自動派生時鐘(Automatically Derived Clocks)

自動派生的時鐘也稱為自動生成的時鐘。如果已經定義了相關的主時鐘,Vivado IDE會自動為時鐘修改模塊(CMBs)的輸出引腳創建約束。

在Xilinx 7系列器件中,CMBs是:

1,MMCM*/ PLL*

2,BUFR

3, PHASER*

例:以下自動導出的時鐘示例是由MMCM生成的時鐘。主時鐘clkin驅動MMCME2實例clkip / mmcm0的輸入CLKIN。自動生成時鐘的名稱是cpuClk,其定義點是clkip / mmcm0 / CLKOUT。

5 時鐘組(Clock Groups)

默認情況下,Vivado IDE會對設計中所有時鐘之間的路徑進行計時,除非您通過使用時鐘組或錯誤的路徑約束來指定。set_clock_groups命令禁用您標識的時鐘組之間的時序分析,而不是同一組內的時鐘之間的時序分析。與set_false_path約束不同,時鐘之間的兩個方向都會忽略時序。

可以使用-group選項多次指定多組時鐘。如果設計中不存在組中的任何時鐘,則該組變空。只有當至少兩個組有效且不為空時,set_clock_groups約束才會保持有效。如果只有一個組保持有效且所有其他組都為空,則不應用set_clock_groups約束并生成錯誤消息。

使用原理圖查看器或時鐘網絡報告可視化時鐘樹的拓撲,并確定哪些時鐘不能一起定時。您還可以使用時鐘交互報告來查看兩個時鐘之間的現有約束,并確定它們是否共享相同的主時鐘 - 也就是說,它們具有已知的相位關系 - 或者識別沒有共同周期的時鐘(不可擴展)。

5.1時鐘類別

1)同步時鐘(Synchronous Clocks)

當兩個時鐘的相對相位是可預測的時,它們是同步的。當它們的樹源自網表中的同一根,并且它們具有共同的時間段時,通常就是這種情況。

2)異步時鐘(Asynchronous Clocks )

當無法確定它們的相對相位時,兩個時鐘是異步的。

例如,由電路板上的獨立振蕩器產生并通過不同輸入端口進入FPGA的兩個時鐘沒有已知的相位關系。因此,它們必須被視為異步。如果它們是由電路板上的相同振蕩器產生的,那就不是真的。

3)不可擴展時鐘(Unexpandable Clocks )

當定時引擎無法確定超過1000個周期的共同周期時,兩個時鐘不可擴展。在這種情況下,在時序分析期間使用1000個周期內的最差設置關系,但是時序引擎無法確保這是最悲觀的情況。

這是典型的情況下,兩個時鐘的奇數分數周期比。例如,考慮由共享同一個主時鐘的兩個MMCM生成的兩個時鐘clk 0和clk 1:

1,clk0的周期為5.125 ns。

2,Clk1的周期為6.666 ns.

它們的時鐘上升沿不會在1000個周期內重新對齊。定時引擎在兩個時鐘之間的時序路徑上使用0.01 ns的建立路徑要求。即使兩個時鐘在其時鐘樹根處具有已知的相位關系,它們的波形也不允許它們之間的安全時序分析。

5.2異步時鐘組(Asynchronous Clock Groups)

異步時鐘和不可擴展的時鐘無法安全定時。在分析期間,可以使用set_clock_groups命令忽略它們之間的時序路徑。

創建異步時鐘組

使用-asynchronous選項創建異步組。

set_clock_groups -name async_clk0_clk1 -asynchronous -group {clk0 usrclk itfclk} -group {clk1 gtclkrx gtclktx}

5.3 排他時鐘組(Exclusive Clock Groups)

一些設計具有幾種需要使用不同時鐘的操作模式。時鐘之間的選擇通常使用諸如BUFGMUX和BUFGCTRL或A LUT的時鐘多路復用器來完成。

通過使用set_clock_groups的選項來約束它們:

1,-logically_exclusive

2, -physically_exclusive

例:MMCM實例生成clk0和clk1,它們連接到BUFGMUX實例clkmux。clkmux的輸出驅動設計時鐘樹。

默認情況下,Vivado IDE會分析clk0和clk1之間的路徑,即使兩個時鐘共享同一個時鐘樹且不能同時存在。

您必須輸入以下約束以禁用兩個時鐘之間的分析:

set_clock_groups -name exclusive_clk0_clk1 -physically_exclusive /

-group clk0 -group clk1

6 時鐘延遲、抖動和不確定性(Clock Latency, Jitter, and Uncertainty)

6.1 時鐘延遲

在電路板上和FPGA內部傳播之后,時鐘邊沿到達目的地并有一定的延遲。此延遲通常表示為:

1,源延遲(時鐘源點之前的延遲,通常在設備外部)

2,網絡延遲

對于Xilinx FPGA,主要使用set_clock_latency命令指定器件外部的時鐘延遲。

# Minimum source latency value for clock sysClk (for both Slow and Fast corners)

set_clock_latency -source -early 0.2 [get_clocks sysClk]

# Maximum source latency value for clock sysClk (for both Slow and Fast corners)

set_clock_latency -source -late 0.5 [get_clocks sysClk]

6.2時鐘不確定性

1)時鐘抖動(Clock Jitter)

對于ASIC器件,時鐘抖動通常用時鐘不確定性特性表示。但是,對于Xilinx FPGA,抖動屬性是可預測的。它們可以由時序分析引擎自動計算,也可以單獨指定。

①輸入抖動是連續時鐘邊沿與標稱或理想時鐘到達時間的變化之間的差異。輸入抖動是絕對值,表示時鐘邊沿每一側的變化。

使用set_input_jitter命令分別指定每個主時鐘的輸入抖動。您不能直接在生成的時鐘上指定輸入抖動。Vivado IDE定時引擎自動計算生成的時鐘從其主時鐘繼承的抖動。

②系統抖動是由電源噪聲,電路板噪聲或系統的任何額外抖動引起的整體抖動。

使用set_system_jitter命令僅為整個設計設置一個值,即所有時鐘。

以下命令在通過輸入端口clkin傳播的主時鐘上設置+/- 100 ps抖動:

set_input_jitter [get_clocks -of_objects [get_ports clkin]] 0.1

2)額外的時鐘不確定性

使用set_clock_uncertainty命令根據需要為不同的角點,延遲或特定時鐘關系定義額外的時鐘不確定性。這是從時序角度為設計的一部分添加額外余量的便捷方式。

set_clock_uncertainty 2.0 -from [get_clocks clk1] -to [get_clocks clk2]

set_clock_uncertainty 1.0 [get_clocks clk1]

編輯:hfy

-

寄存器

+關注

關注

31文章

5336瀏覽量

120230 -

數字設計

+關注

關注

0文章

46瀏覽量

22295

發布評論請先 登錄

相關推薦

FPGA時序約束之衍生時鐘約束和時鐘分組約束

時序約束之時鐘約束

時序約束之時鐘組約束

STM32F407之時鐘、頻率、存儲的整體特性

時鐘約束的概念

FPGA開發之時序約束(周期約束)

硬件設計中教你如何正確的約束時鐘

時序約束一主時鐘與生成時鐘

數字設計之時鐘約束和時鐘類型介紹

數字設計之時鐘約束和時鐘類型介紹

評論