在這篇文章中,我們將介紹如何調用 Hyperlynx?、如何設置簡單的原理圖以及如何運行一些基本的仿真操作。Hyperlynx? 可支持下列兩種仿真工作流程。

LineSim:

用來預布局仿真,是設計周期中的早期仿真工具,主要用來評估假設情景并幫助定義電路板參數和布線指南。通過創建 I/O 緩存器、走線,終端以及連接器/電纜組件的示意圖,在“Schematic GUI”中完成 LineSim 中的仿真。

BoardSim:

用于布局后仿真以對 PCB 設計進行分析。PCB 中所需的網絡從布局文件中選出,然后在像 LineSim 這樣的工具中進行仿真。由于它使用的是含布線約束、相鄰網絡布線以及距離等信息的布局文件,仿真是高度準確的。 可以在 LineSim 中查找任何違規操作或所需的更改,并在最終 PCB 上簽發制造之前將其反饋到布局中。

在本系列中,可以使用 LineSim 和 Boardsim(如需要),具體取決于所討論的主題。

現在我們通過一個簡單的仿真操作來了解一下這個工具。調用 Hyperlynx? 并選擇“New -> New SI Schematic”,如果調用的是“Waveform Viewer”,選擇“Both”或“Oscilloscope”

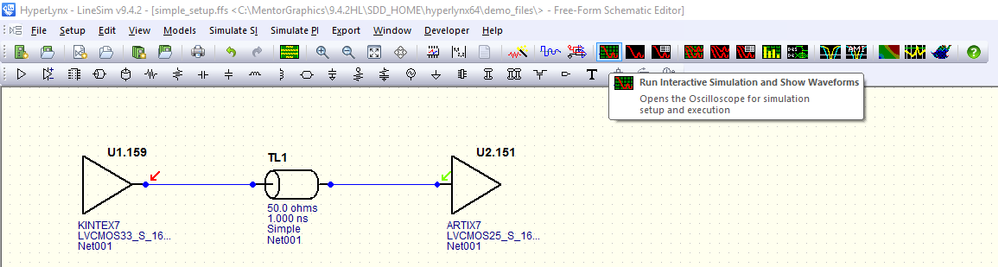

Hyperlynx? 支持 SI 仿真所需的基本元素,如下面的屏幕截圖所示:

發射器和接收器(IBIS 模型)

傳輸線

“Simple”、“Microstrip”、“Stripline”、“Wire”、“Cable”、“Connector”

疊加線和耦合線

通孔

S 參數/Spice 模型

電壓和接地

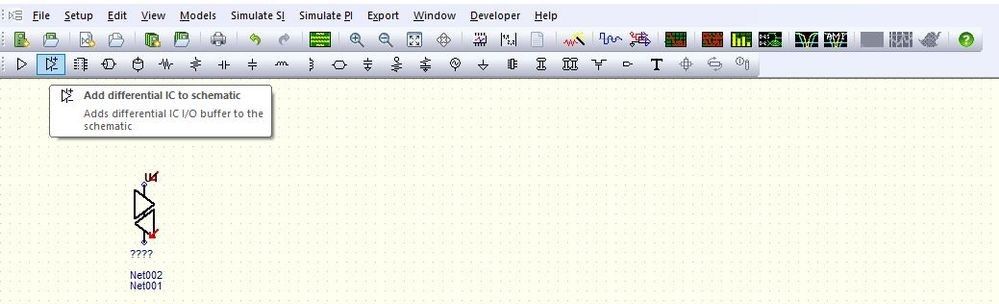

要創建原理圖,請針對單端 I/O 標準選擇“Add IC to Schematic”或針對差分 I/O 標準選擇“Add differential IC to Schematic”。

單端建立:

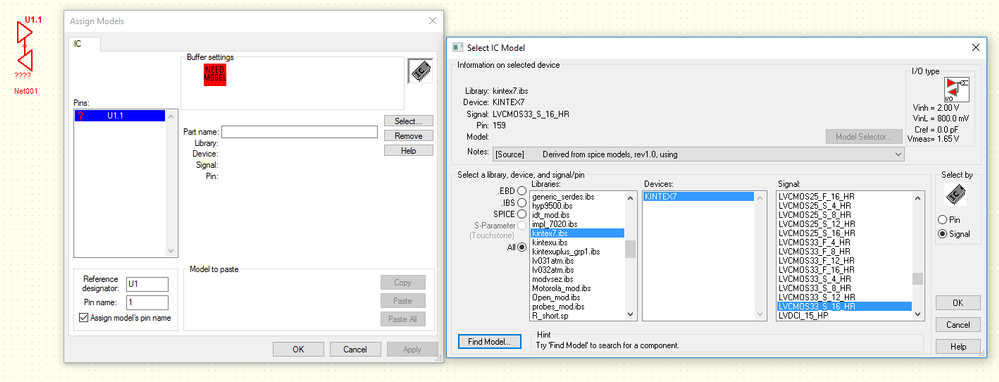

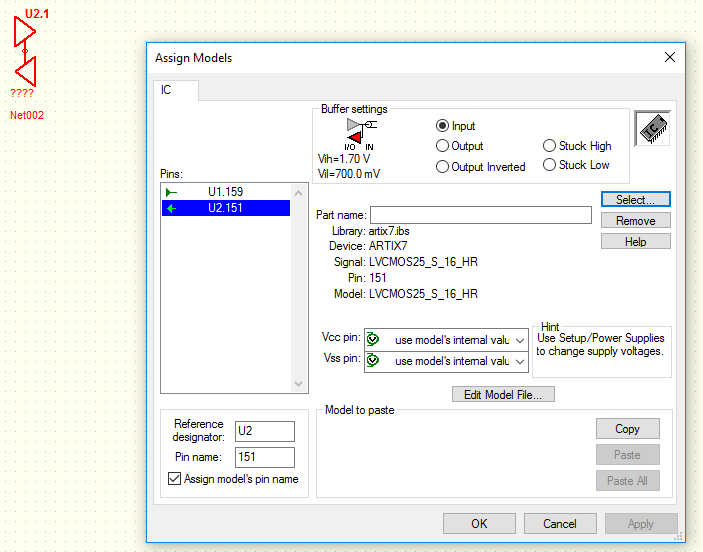

雙擊 IC 打開“Assign Models”窗口。我們將使用單端 I/O 標準 LVCMOS33。

注意:您需要將 IBIS 文件 (.ibs) 保存在 Hyperlynx? 的“Libs”文件夾 (C:/MentorGraphics/9.4.2HL/SDD_HOME/hyperlynx64/Libs) of Hyperlynx? 中,才能在默認庫中查看它。 您可以選擇在“Setup -> Options ->Directories”下的“Model-Library”文件路徑中添加更多文件夾。要包含設計文件夾中的所有文件夾,務必選中“Add design folder”和“Add design folder subfolders”。

選擇必要的模型設置(在此示例中為變送器,因此應選擇輸出),然后單擊“OK”

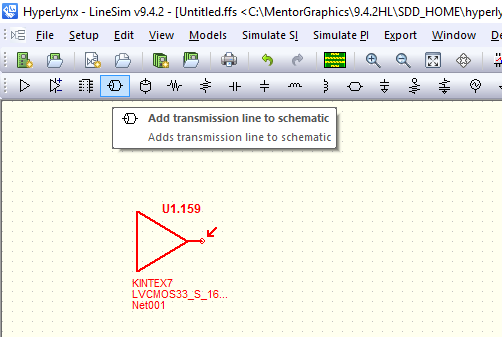

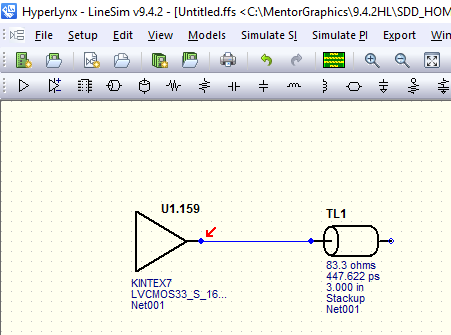

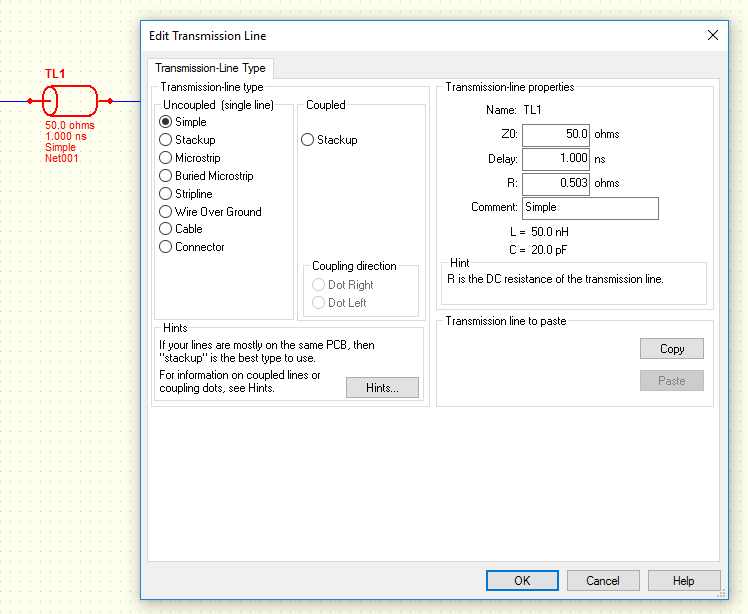

單擊“Add transmission line to schematic”

雙擊 TL1 設置傳輸線并選擇“Simple”非耦合類型,然后將“Z0“設置為 50 ohms、將“Delay”設置為 1.000 ns

通過選擇必要的“Receiver IBIS Model”并將“Buffer”設置為“Input”來設置“接收器”并完成原理圖。保存原理圖設置。

運行仿真,選擇“Run Interactive Simulations and Show Waveforms”按鈕(該按鈕會打開“Digital Oscilloscope”窗口)。

在“Oscilloscope”窗口中設置以下設置,然后單擊“Start Simulation

Operation -> Standard

Stimulus -> Global,

Oscillator -> 100 MHz, 50% Duty

IC modeling -> Typical

Thresholds for -> U2.151

Horizontal Scale -> 5 ns/div”

藍線顯示 U2 的 Vinh、Vinl 閾值。在確定接收器波形是否如預期那樣超過這些閾值時,上述步驟非常有用,讓接收器可以確定所需的邏輯是“Low”還是“High”。 RX 波形 (綠色)和 TX 波形 (紅色)的轉換不清晰,我們會在本系列后面的主題中詳細討論。

差分建立:

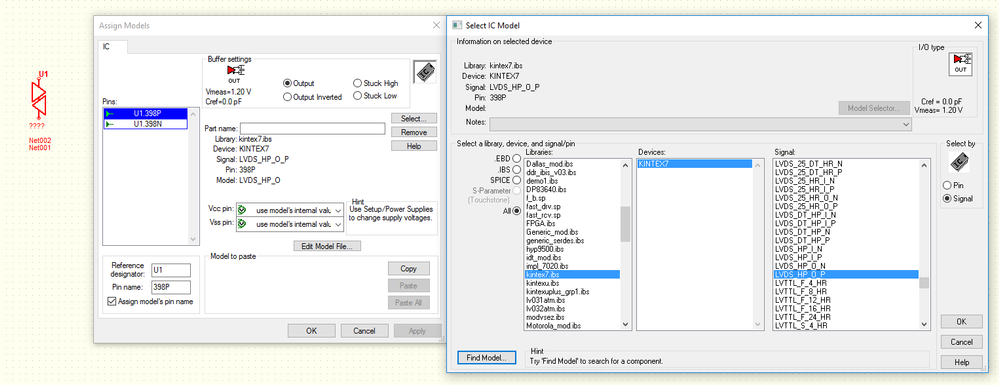

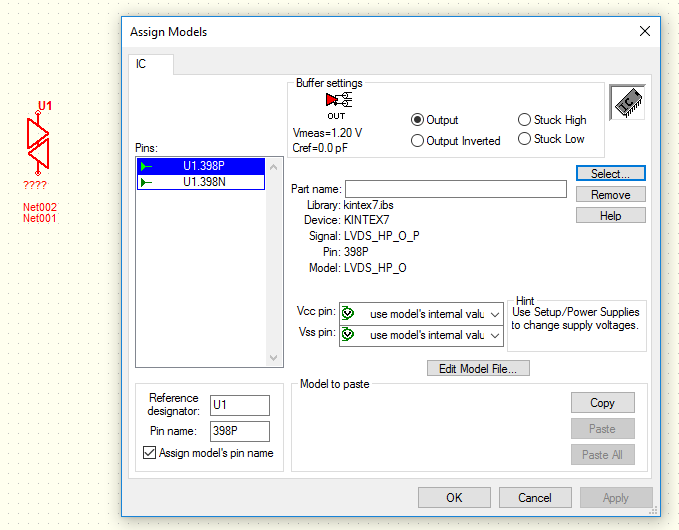

“Add differential IC to Schematic”后雙擊 IC,打開“Assign Models”窗口。我們將通過差分 I/O 標準 LVDS 來進行此建立,因為它是最常用的差分 I/O 標準之一。

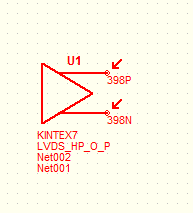

選擇必要的模型設置。在這個示例中用的是一個發射器,因此“P”后綴被選為輸出,而且“N”會自動變為“Output Inverted”,因為這是一個差分緩存器。單擊“OK”。

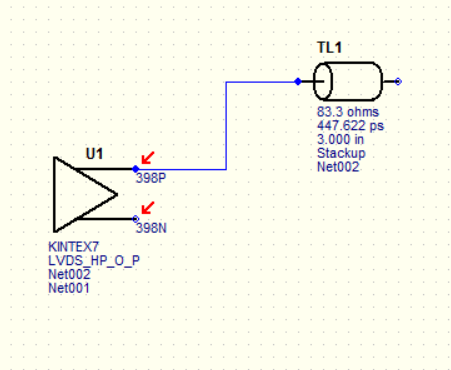

單擊“Add transmission line to schematic”。

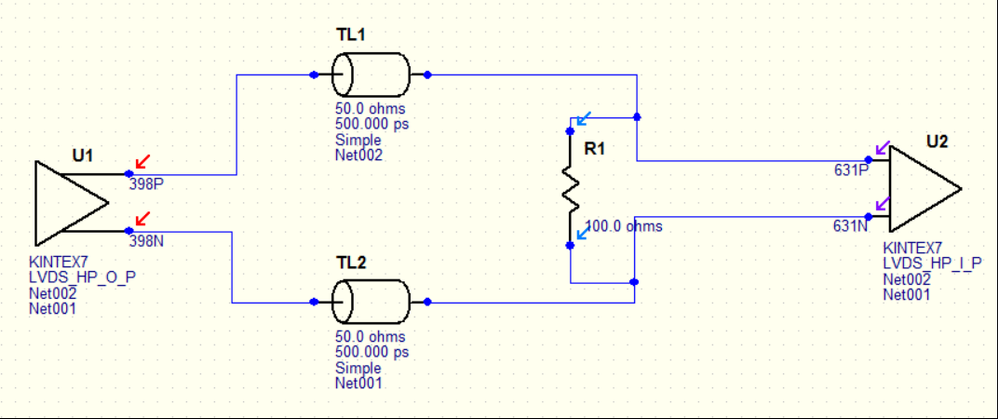

雙擊 TL1 設置傳輸線。如果是非耦合類型,選擇“Simple”,然后將“Z0”設置為 50 歐姆;將“Delay”設置為 0.5 ns,并選擇“Copy”以重復使用“N”傳輸線。

添加 TL2,雙擊“Edit”,然后選擇“Paste”將 TL1 的屬性復制到 TL2。

通過選擇必要的“Receiver IBIS Model”并將“Buffer”設置為“Input”來設置“Receiver”。這樣原理圖就完成了。

保存原理圖設置。

添加 LVDS 所需的 100 歐姆終端電阻,并通過雙擊“R”符號將值設置為 100 歐姆。

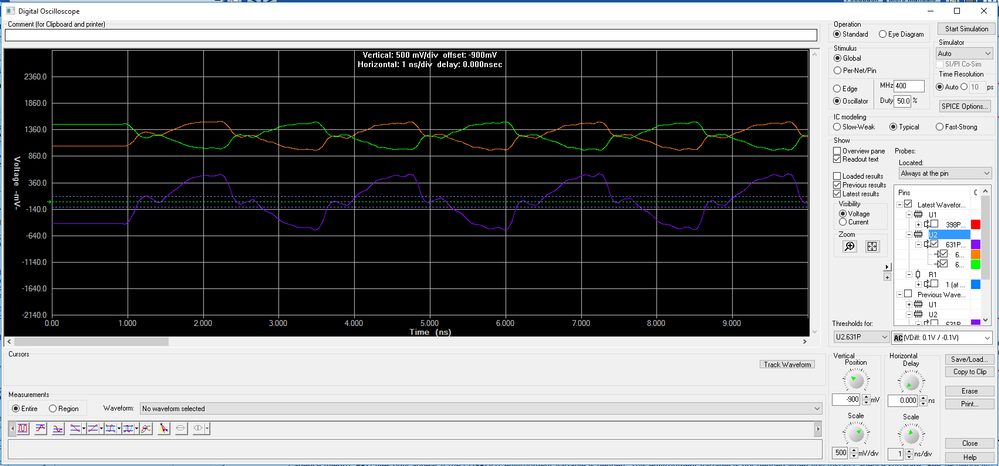

通過選擇“Run Interactive Simulations and Show Waveforms”按鈕。(該按鈕隨即會打開“Digital Oscilloscope”窗口)來運行仿真。在“Oscilloscope”窗口中輸入以下設置,然后單擊“Start Simulation”:

Operation -> Standard

Stimulus -> Global,

Oscillator -> 400 MHz, 50% Duty

IC modeling -> Typical

Thresholds for -> U2.631P

Horizontal Scale -> 1ns/div

Horizontal Scale -> 1ns/div

Vertical Position -> -900 mv/div

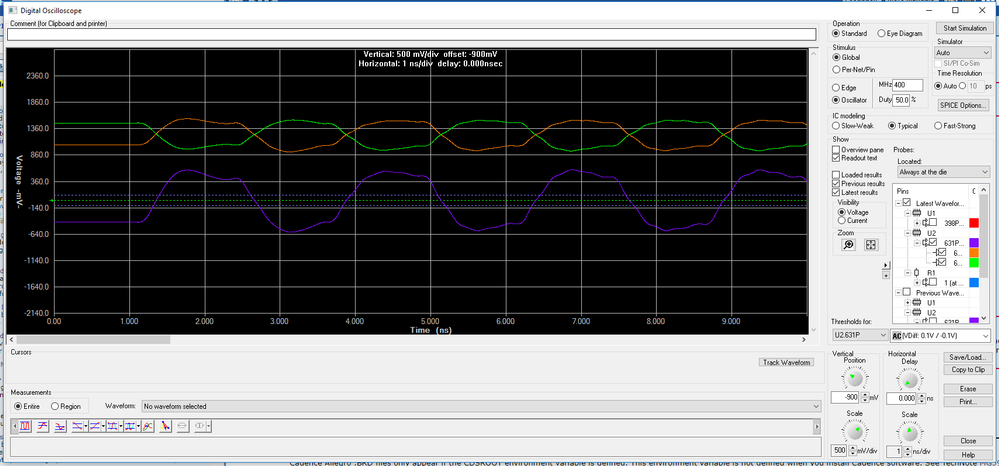

信號探測可以在“At the Pin”或“At the die”處完成。

在引腳處探測:

如果您在電路板上的引腳上進行物理探測,此操作指的是將仿真探頭置于引腳上,從而展示您在實驗室示波器中會看到的結果。“Purple”是差分探頭的波形。

在裸片處探測:

指的是將仿真探頭放置在裸片內從而展示裸片所看到的、無法在電路板上探測到結果。

有關如何對內部和外部終端進行探測的詳情,請參閱(Xilinx Answer 57566)。

定義 Stackup

PCB 的疊層需要針對介電材料、金屬類型、信號以及平面層在電路板中其他項目的布置來進行定義。在運行仿真之前進行此設置有助于模擬 PCB 及各種特性(例如走線阻抗、走線分離及其他參數等)。

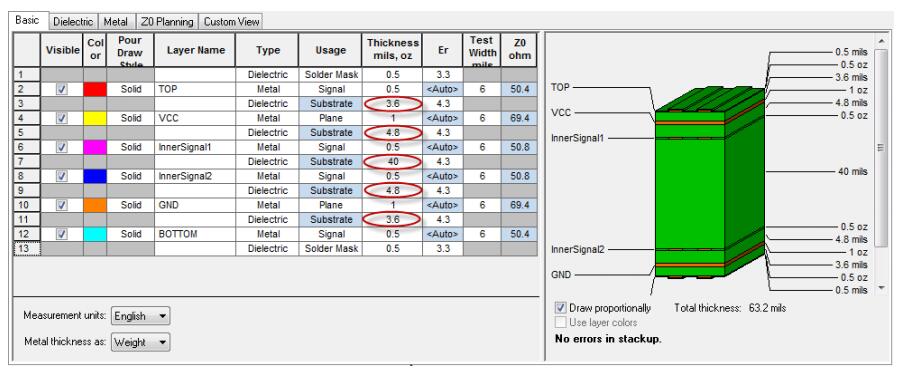

Hyperlynx? 提供了一個含基于電子數據表視圖的 Stackup Editor(您可以在該視圖中輸入值和圖像面板以使疊加結果可視化)。編輯器可以通過選擇“Setup -> Stackup Edit”或“Edit Stackup”按鈕來訪問,如下所示:

如上圖所示,編輯器有各種標簽及其快捷說明。

基要:通過添加/刪除層、設置測量單位(英制/公制)和金屬厚度(厚度/重量)來定義疊層信息。

介電:定義疊層的介電特性,如技術、損耗角正切和導熱系數。可以選擇根據周圍的介電層來計算金屬層的介電常數。

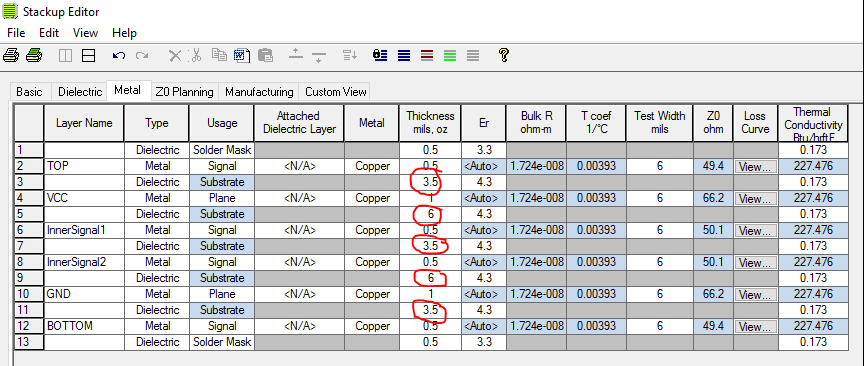

金屬:定義金屬特性,如金屬類型(銅/鋁/錫等)、厚度和金屬的其他屬性。

Z0 規劃:定義疊層的特征阻抗。此計劃編制標簽是最有用的標簽之一,因為它讓您能夠在計算單跡和差分對走線的特定目標阻抗時得出最佳數據。

制造:定義金屬表面的粗糙度和痕量蝕刻參數。

定制視圖:用來設置從其他標簽派生的電子數據表信息的自定義視圖,并可根據用戶偏愛進行調整。

有關這些標簽的高級詳細信息,請參閱“Hyperlynx”用戶指南。

現在我們來設置一個“Z0”為 50 歐姆的疊層,因為這是最常用的值。走線阻抗由走線的“Width”、參考平面上方的“Height”或“Dielectric thickness”以及“Dielectric constant”來決定。有多種方法來可設置疊層編輯器中的阻抗,然而我們將使用“Metal”標簽來快速設置所需的阻抗。

打開“Stackup Editor”,然后單擊“View -> Calculate Z0”(如果未啟用,則啟用它)。這樣工具就可以基于疊加來自動計算特征阻抗了。

如下所示,選擇“Metal”標簽,然后設置“電介質厚度”,并將信號層標記為“Z0”。

確保在您修改參數后,“Picture”面板中顯示“No errors found in stackup”的消息。

通過“Z0 Planning”標簽來檢查單跡和差分對的目標阻抗所需的走線寬度和間距。這個步驟很有用,由于接口/協議具有不同的阻抗要求,因此此標簽有助于理解要滿足這些規格所需的寬度或間距。

1. 適用于單跡:從“Plan for”下拉列表中選擇“單跡”,并在信號層的“Target Z0”值列中輸入 50、60、40、50,然后按“Enter”鍵。實現這些阻抗所需的“Trace”寬度隨即會被更新。

2. 適用于差分對:從“Plan for”下拉列表中選擇“差分對”,在“Strategy”中選擇“Solve for width”,然后在信號層的“Target Z0”值列中輸入 100、90、80、100。現在按“Enter”鍵。實現這些阻抗所需的“Trace”寬度隨即會顯示。也可以按照差分走線分離策略,通過選擇“Solve for Separation”的方法來滿足“Target Z0”的需要。此策略還包括使用兩者(即“Solve for width”和“Solve for Separation”)的選項,并在“Z0 Curve”列中顯示結果。

堆棧現已創建,可將其導出以便在將來進行設計和仿真時重用,從而節省時間。單擊“File -> Export -> save as .stk file”

單擊“OK”關閉編輯器。

注意:PCB 設計的疊層創建是設計進程中最重要和最關鍵的步驟之一,需要根據復雜性投入所需的時間和精力。“What If”分析可以在編輯器中根據設計和制造要求使用,以實現最終的疊加。但是,上述步驟旨在深入了解編輯器,并僅針對本系列中提及的未來設計和仿真提供疊加。這些步驟不基于任何設計參數。

接下來你們可以通過我們上面討論的步驟來熟悉這些工具和接口。

在下一篇文章中,我們將介紹 Hyperlynx? 的其他一些功能,為您提供如何使用該工具的基礎知識。

在那之前,好好熟悉一下這個工具及各種設置,我們下次再見。

編輯:hfy

-

PCB設計

+關注

關注

394文章

4690瀏覽量

85755 -

信號完整性

+關注

關注

68文章

1408瀏覽量

95499

發布評論請先 登錄

相關推薦

HYPERLYNX 仿真工具使用指南

信號完整性仿真應用

信號完整性與電源完整性的仿真分析與設計

基于HyperLynx的高速DSP信號完整性仿真

信號完整性仿真實驗:Hyperlynx?調用及兩種仿真工作流程

信號完整性仿真實驗:Hyperlynx?調用及兩種仿真工作流程

評論