將通過五篇文章來給大家講解xilinx FPGA 使用mig IP對DDR3的讀寫控制,旨在讓大家更快的學習和應用DDR3。

本實驗和工程基于Digilent的Arty Artix-35T FPGA開發板完成。

軟件使用Vivado 2018.1。

參考工程:ddr3_test。

第五篇:mig讀寫時序下板實現

1頂層文件和約束文件

ddr3_test.v

參見參考工程:ddr3_test。

ddr3.xdc

1. set_property PACKAGE_PIN E3 [get_ports clk]

2. set_property IOSTANDARD LVCMOS33 [get_ports clk]

3. set_property PACKAGE_PIN D9 [get_ports reset]

4. set_property PACKAGE_PIN E1 [get_ports init_calib_complete]

5. set_property IOSTANDARD LVCMOS33 [get_ports init_calib_complete]

6. set_property IOSTANDARD LVCMOS33 [get_ports reset]

2 下板實現讀寫時序

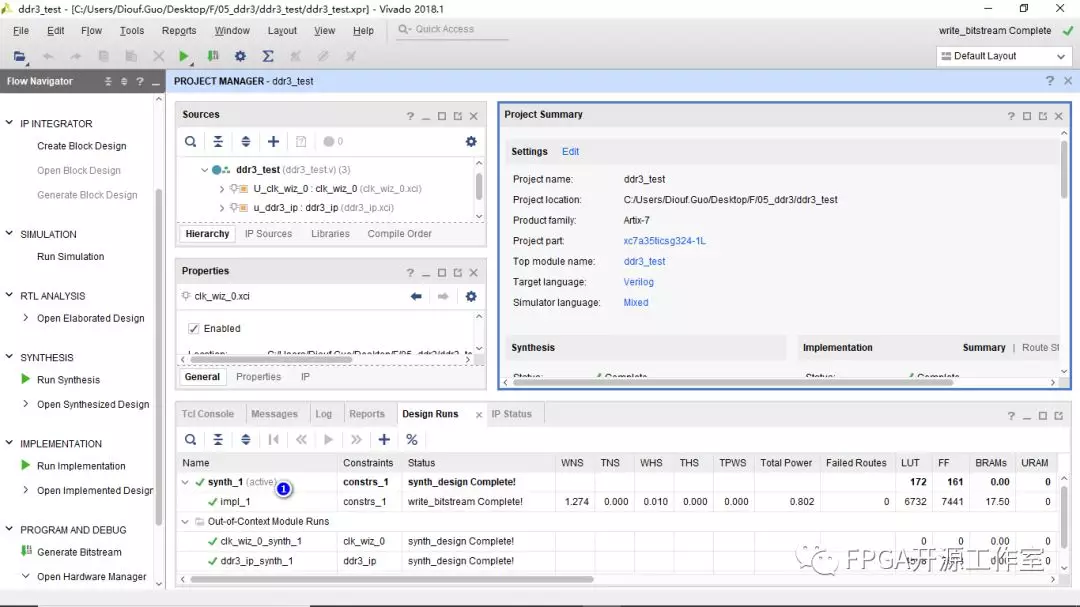

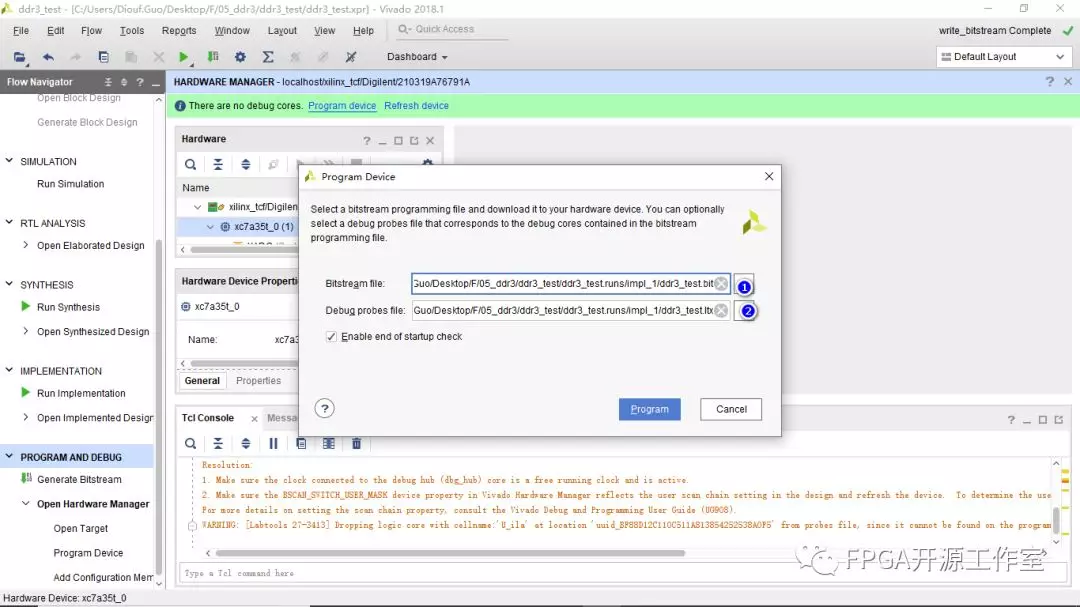

1>①完成綜合和實現

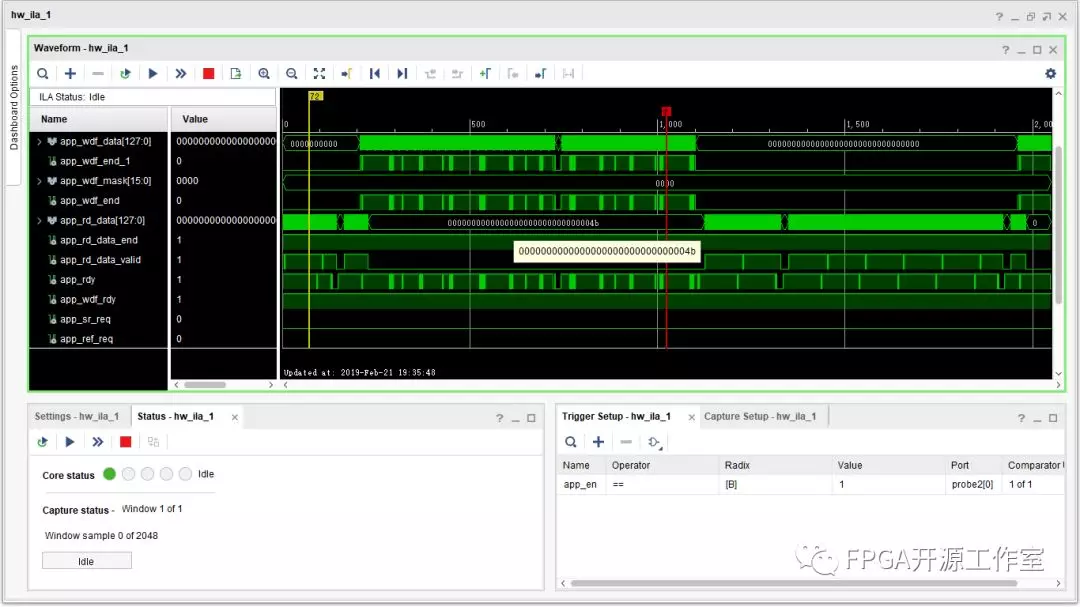

3>下載完成,查看波形。

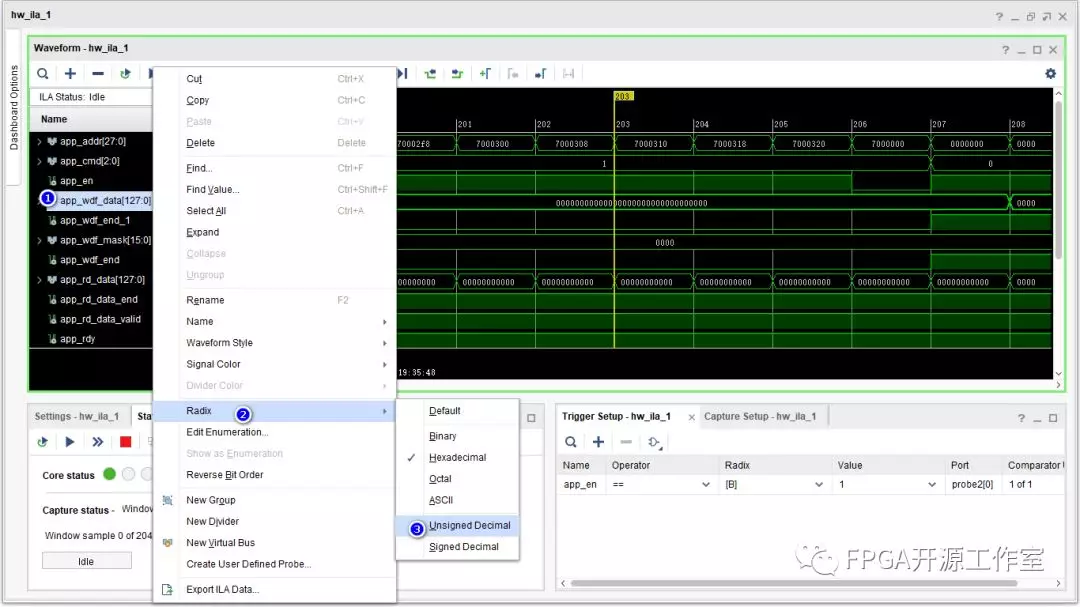

4>將app_wdf_data數據格式改為Unsigned Decimal。

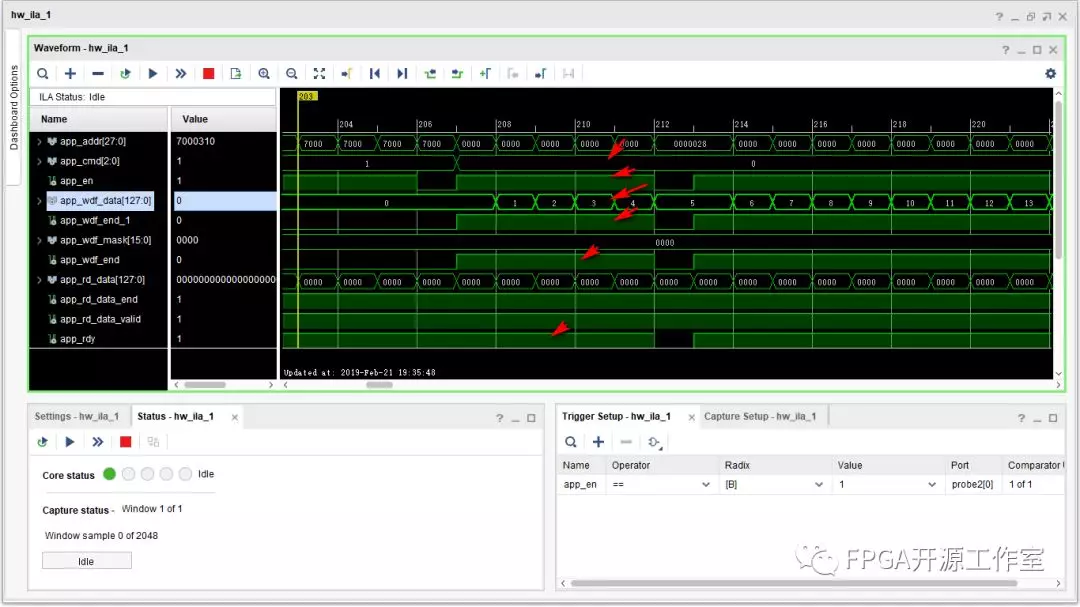

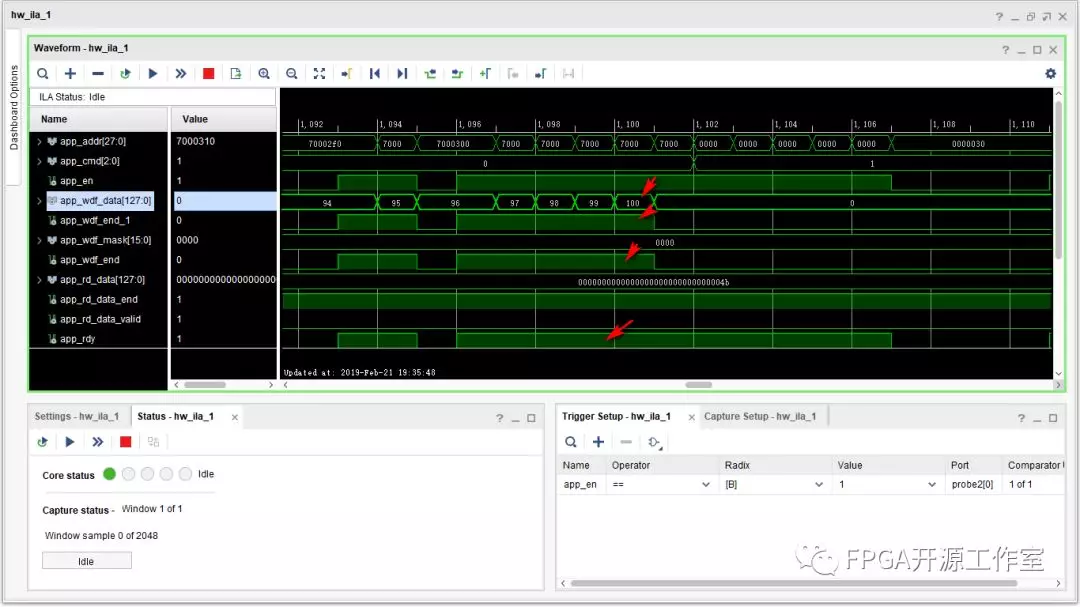

5>查看寫時序。

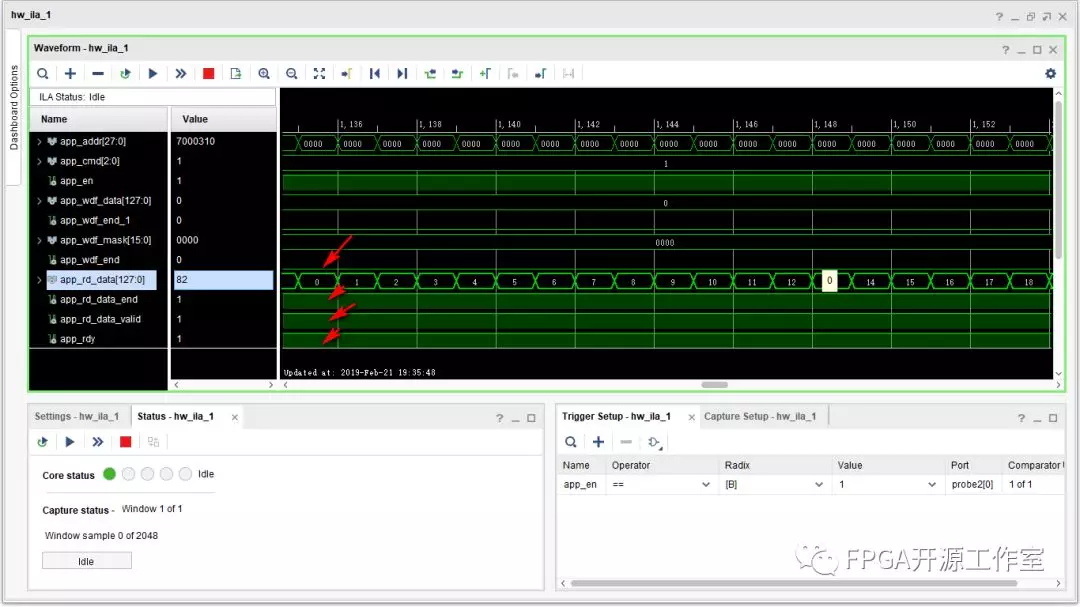

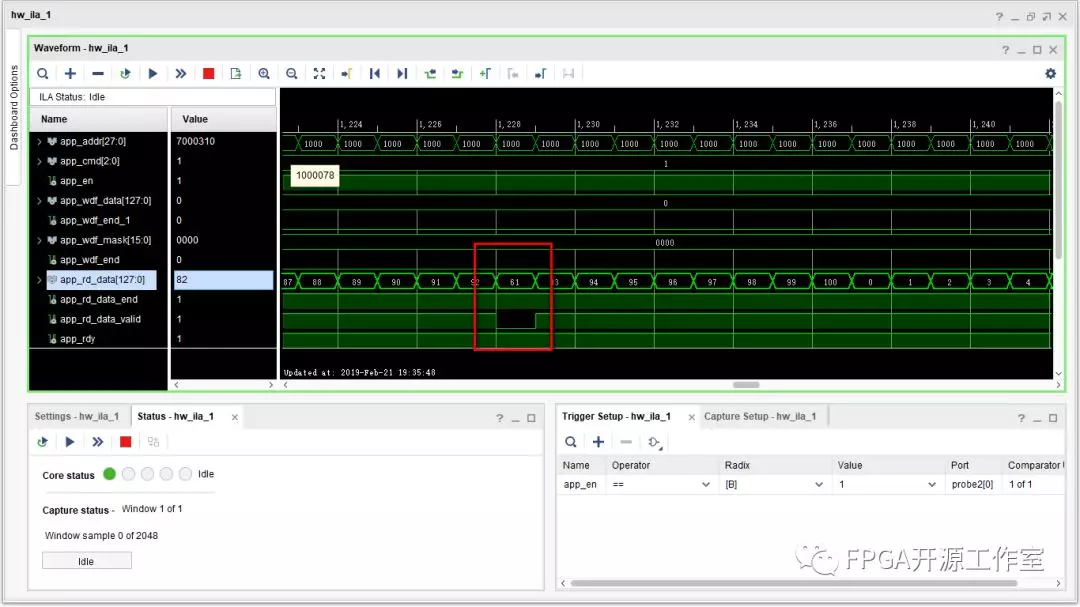

6>查看讀時序。

基于xilinx mig ip對ddr3讀寫驗證完成。

編輯:hfy

-

FPGA

+關注

關注

1629文章

21729瀏覽量

603008 -

DDR3

+關注

關注

2文章

276瀏覽量

42243

發布評論請先 登錄

相關推薦

正點原子fpga開發板不同型號

正點原子和野火開發板哪個好

【米爾-Xilinx XC7A100T FPGA開發板試用】+01.開箱(zmj)

基于FPGA的DDR3多端口讀寫存儲管理設計

國產FPGA核心板!米爾紫光同創Logos-2和Xilinx Artix-7核心板

FPGA核心板 Xilinx Artix-7系列XC7A100T開發平臺,米爾FPGA工業開發板

精選推薦!紫光盤古系列FPGA開發板信息匯總

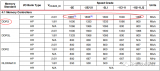

全套DDR、DDR2、DDR3、DDR3L、LPDDR3 和 DDR4 電源解決方案同步降壓控制器數據表

fpga開發板是什么?fpga開發板有哪些?

完整的DDR2、DDR3和DDR3L內存電源解決方案同步降壓控制器TPS51216數據表

完整的DDR、DDR2和DDR3內存電源解決方案同步降壓控制器數據表

基于Digilent的Arty Artix-35T FPGA開發板的DDR3讀寫控制

基于Digilent的Arty Artix-35T FPGA開發板的DDR3讀寫控制

評論