本文主要介紹以太網(wǎng)Drive Side接口(MAC和PHY之間的接口),也被稱為MII(Media Independent Interface),支持從10M到100G的不同應(yīng)用場(chǎng)合,主要包括MII、RMII、SMII(Cisco Systems Specification)、SSMII、S3MII、GMII、RGMII、SGMII、QSGMII(Cisco Systems Specification)、TBI、RTBI、XGMII、XAUI、RXAUI、XLGMII、XLAUI、CGMII、CAUI、HIGIG(Broadcom Specification)、Interlaken等接口,下面就針對(duì)10Mbps到100Gbps的不同接口進(jìn)行介紹,最后介紹一下PHY芯片的控制接口MDIO BUS。

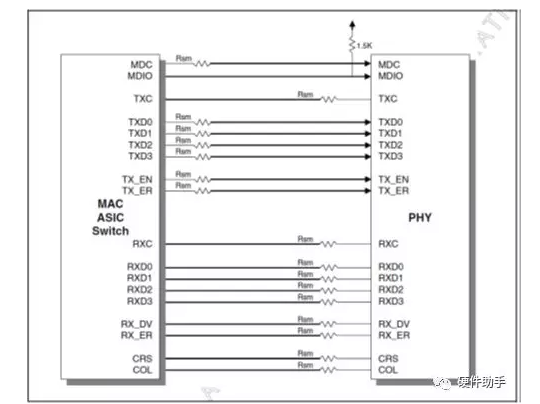

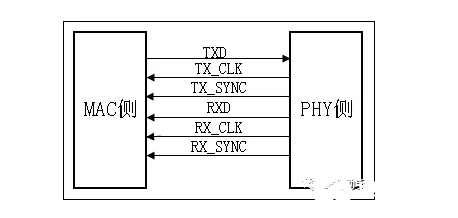

1、MII接口

100Mbps速率下,時(shí)鐘頻率為25MHz,10Mbps速率下,時(shí)鐘頻率為2.5MHz。TXC和RXC均由PHY提供。PHY在TXC的上升沿采樣TXD上的數(shù)據(jù),MAC在RXC的上升沿采樣RXD上的數(shù)據(jù)。

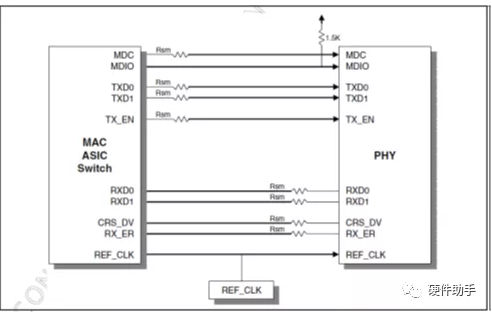

2、RMII接口

REF_CLK是由外部時(shí)鐘源提供的50MHz參考時(shí)鐘,與MII接口不同,MII接口中的接收時(shí)鐘和發(fā)送時(shí)鐘是分開的,而且都是由PHY芯片提供給MAC芯片的。這里需要注意的是,由于數(shù)據(jù)接收時(shí)鐘是由外部晶振提供而不是由載波信號(hào)提取的,所以在PHY層芯片內(nèi)的數(shù)據(jù)接收部分需要設(shè)計(jì)一個(gè)FIFO,用來(lái)協(xié)調(diào)兩個(gè)不同的時(shí)鐘,在發(fā)送接收的數(shù)據(jù)時(shí)提供緩沖。PHY層芯片的發(fā)送部分則不需要FIFO,它直接將接收到的數(shù)據(jù)發(fā)送到MAC就可以了。

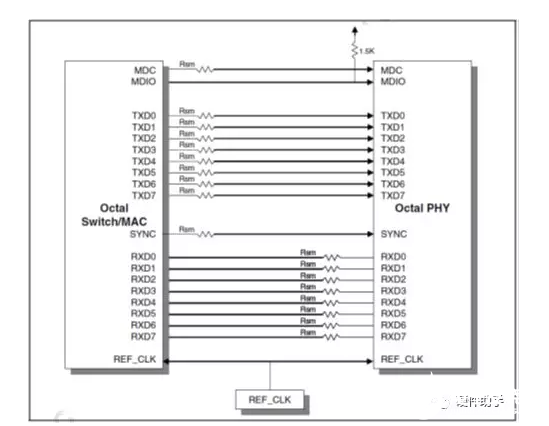

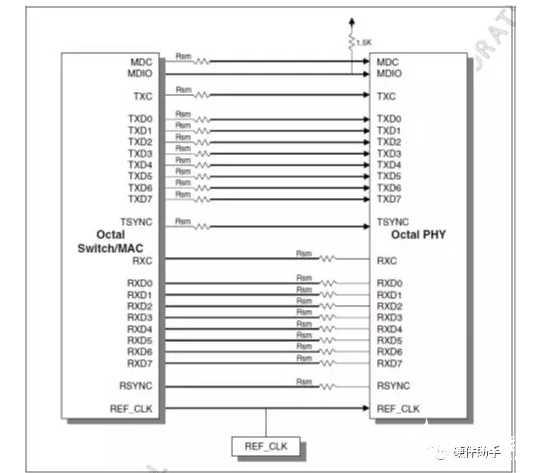

3、SMII(Cisco Systems Specification)接口

REF_CLK:所有端口共用的一個(gè)參考時(shí)鐘,頻率為125MHz,為什么100Mbps速率要用125MHz時(shí)鐘呢?因?yàn)樵诿?位數(shù)據(jù)中會(huì)插入2位控制信號(hào)。

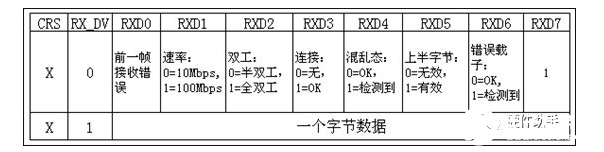

TXD/RXD以10比特為一組,以SYNC為高電平來(lái)指示一組數(shù)據(jù)的開始,在SYNC變高后的10個(gè)時(shí)鐘周期內(nèi),TXD上依次輸出的數(shù)據(jù)是:TXD[7:0]、TX_EN、TX_ER,控制信號(hào)的含義與MII接口中的相同;RXD上依次輸出的數(shù)據(jù)是:RXD[7:0]、RX_DV、CRS,RXD[7:0]的含義與RX_DV有關(guān),當(dāng)RX_DV為有效時(shí)(高電平),RXD[7:0]上傳輸?shù)氖俏锢韺咏邮盏臄?shù)據(jù)。當(dāng)RX_DV為無(wú)效時(shí)(低電平),RXD[7:0]上傳輸?shù)氖俏锢韺拥臓顟B(tài)信息數(shù)據(jù)。

當(dāng)速率為10Mbps時(shí),每一組數(shù)據(jù)要重復(fù)10次,MAC/PHY芯片每10個(gè)周期采樣一次。MAC/PHY芯片在接收到數(shù)據(jù)后會(huì)進(jìn)行串/并轉(zhuǎn)換。

?4、SSMII接口

5、S3MII接口

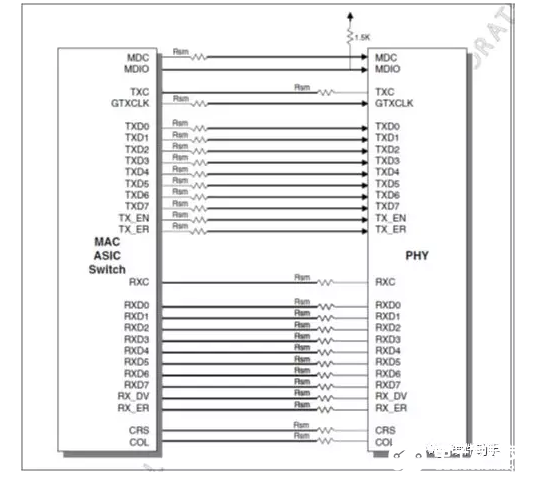

6、GMII接口

GMII的數(shù)據(jù)寬度為8位,GMII接口中的發(fā)送參考時(shí)鐘GTX_CLK和接收參考時(shí)鐘RX_CLK的頻率均為125MHz(1000Mbps/8=125MHz)。GMII接口中的GTX_CLK是由MAC芯片提供給PHY芯片。

在實(shí)際應(yīng)用中,絕大多數(shù)GMII接口都是兼容MII接口的,一般的GMII接口都有兩個(gè)發(fā)送參考時(shí)鐘:TX_CLK和GTX_CLK(兩者的方向是不一樣的),在用作MII模式時(shí),使用TX_CLK和8根數(shù)據(jù)線中的4根。

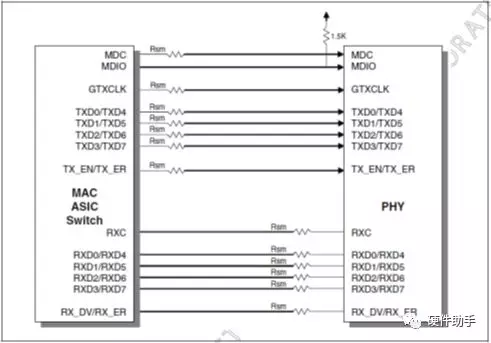

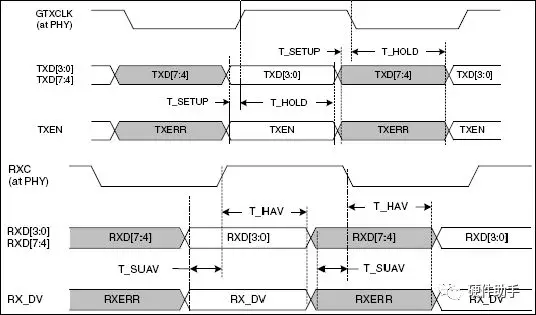

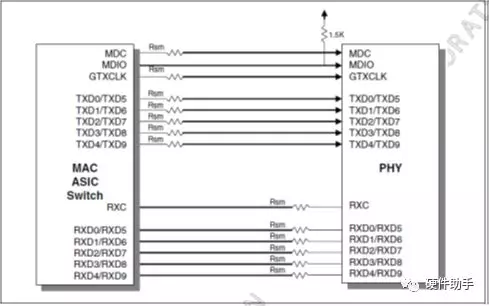

7、RGMII接口

RGMII的時(shí)鐘頻率為125MHz,TX/RX數(shù)據(jù)寬度從8為變?yōu)?位,為了保持1000Mbps的傳輸速率不變,RGMII接口在時(shí)鐘的上升沿和下降沿都采樣數(shù)據(jù)。在參考時(shí)鐘的上升沿發(fā)送GMII接口中的TXD[3:0]/RXD[3:0],在參考時(shí)鐘的下降沿發(fā)送GMII接口中的TXD[7:4]/RXD[7:4]。RGMII同時(shí)也兼容100Mbps和10Mbps兩種速率,此時(shí)參考時(shí)鐘速率分別為25MHz和2.5MHz。

TX_EN信號(hào)線上傳送TX_EN和TX_ER兩種信息,在TX_CLK的上升沿發(fā)送TX_EN,下降沿發(fā)送TX_ER;同樣的,RX_DV信號(hào)線上也傳送RX_DV和RX_ER兩種信息,在RX_CLK的上升沿發(fā)送RX_DV,下降沿發(fā)送RX_ER。

8、SGMII接口

SGMII收發(fā)各一對(duì)差分信號(hào)線,時(shí)鐘頻率625MHz,在時(shí)鐘信號(hào)的上升沿和下降沿均采樣,參考時(shí)鐘RX_CLK由PHY提供,是可選的,主要用于MAC側(cè)沒(méi)有時(shí)鐘的情況,一般情況下,RX_CLK不使用。收發(fā)都可以從數(shù)據(jù)中恢復(fù)出時(shí)鐘。

在TXD發(fā)送的串行數(shù)據(jù)中,每8比特?cái)?shù)據(jù)會(huì)插入TX_EN/TX_ER兩比特控制信息,同樣,在RXD接收數(shù)據(jù)中,每8比特?cái)?shù)據(jù)會(huì)插入RX_DV/RX_ER兩比特控制信息,所以總的數(shù)據(jù)速率為1.25Gbps=625Mbps*2。

其實(shí),大多數(shù)MAC芯片的SGMII接口都可以配置成SerDes接口(在物理上完全兼容,只需配置寄存器即可),直接外接光模塊,而不需要PHY層芯片,此時(shí)時(shí)鐘速率仍舊是625MHz,不過(guò)此時(shí)跟SGMII接口不同,SGMII接口速率被提高到1.25Gbps是因?yàn)椴迦肓丝刂菩畔ⅲ鳶erDes端口速率被提高是因?yàn)檫M(jìn)行了8b/10b變換,本來(lái)8b/10b變換是PHY芯片的工作,在SerDes接口中,因?yàn)橥饷娌唤覲HY芯片,此時(shí)8b/10b變換在MAC芯片中完成了。8b/10b變換的主要作用是擾碼,讓信號(hào)中不出現(xiàn)過(guò)長(zhǎng)的連“0”和連“1”情況,影響時(shí)鐘信息的提取。

9、TBI接口

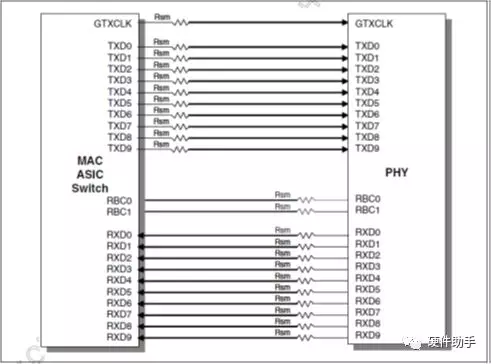

TBI即Ten BitInterface的意思,接口數(shù)據(jù)位寬由GMII接口的8位增加到10位,其實(shí),TBI接口跟GMII接口的差別不是很大,多出來(lái)的2位數(shù)據(jù)主要是因?yàn)樵赥BI接口下,MAC芯片在將數(shù)據(jù)發(fā)給PHY芯片之前進(jìn)行了8b/10b變換(8b/10b變換本是在PHY芯片中完成的,TBI在MAC中完成了,所以每傳輸一個(gè)字節(jié)需要傳輸10bit數(shù)據(jù))。

RBC0和RBC1是從接收數(shù)據(jù)中恢復(fù)出來(lái)的半頻時(shí)鐘,頻率為62.5MHz,RBC0和RBC1不是差分信號(hào),而是兩個(gè)獨(dú)立的信號(hào),兩者之間有180度的相位差,在這兩個(gè)時(shí)鐘的上升沿都采樣數(shù)據(jù)。RBC0和RBC1也叫偽差分信號(hào)。除掉上面說(shuō)到的之外,剩下的信號(hào)都跟GMII接口中的相同。

大多數(shù)芯片的TBI接口和GMII接口兼容。在用作TBI接口時(shí),CRS和COL一般不用。

10、RTBI接口

RTBI接口數(shù)據(jù)位寬為5bit,時(shí)鐘頻率為125MHz,在時(shí)鐘的上升沿和下降沿都采樣數(shù)據(jù),同RGMII接口一樣,TX_EN線上會(huì)傳送TX_EN和TX_ER兩種信息,在時(shí)鐘的上升沿傳TX_EN,下降沿傳TX_ER;RX_DV線上傳送RX_DV和RX_ER兩種信息,在RX_CLK上升沿傳RX_DV,下降沿傳RX_ER。

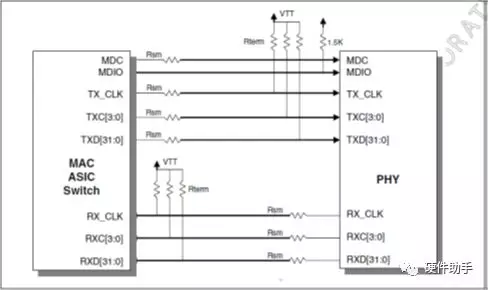

11、XGMII接口

XGMII接口的單端信號(hào)采用HSTL/SSTL_2邏輯,端口電壓1.5V/2.5V,由于SSTL_2的端口電壓高,功耗大,現(xiàn)在已很少使用。

TXC[3:0]:發(fā)送通道控制信號(hào),TXC=0時(shí),表示TXD上傳輸?shù)氖菙?shù)據(jù);TXC=1時(shí),表示TXD上傳輸?shù)氖强刂谱址XC[3:0]分別對(duì)應(yīng)TXD[31:24],TXD[23:16],TXD[15:8],TXD[7:0]。

RXC[3:0]:接收通道控制信號(hào),RXC=0時(shí),表示RXD上傳輸?shù)氖菙?shù)據(jù);RXC=1時(shí),表示RXD上傳輸?shù)氖强刂谱址XC[3:0]分別對(duì)應(yīng)RXD[31:24],RXD[23:16],RXD[15:8],RXD[7:0]。

TX_CLK:TXD和TXC的參考時(shí)鐘,時(shí)鐘頻率156.25MHz,在時(shí)鐘信號(hào)的上升沿和下降沿都采樣數(shù)據(jù)。

RX_CLK:RXD和RXC的參考時(shí)鐘,時(shí)鐘頻率156.25MHz,在時(shí)鐘信號(hào)的上升沿和下降沿都采樣數(shù)據(jù)。156.25MHz*2*32=10Gbps。

XGMII接口還有XLGMII(40Gb)、CGMII(100Gb)等變種。其基本已經(jīng)被XAUI/XLAUI/CAUI接口取代了。

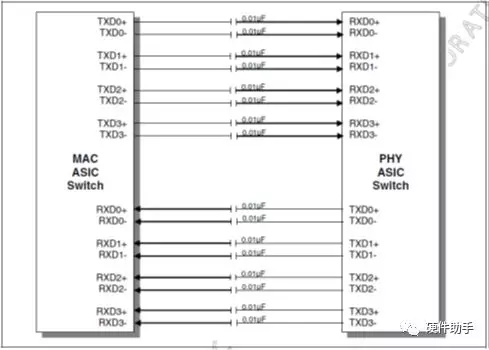

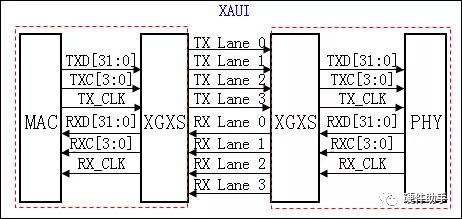

12、XAUI接口

XAUI接口有如下一系列的變種:RXAUI、XLAUI(40Gb)、CAUI(100Gb)等。

由于受電氣特性的影響,XGMII接口的PCB走線最大傳輸距離僅有7cm,并且XGMII接口的連線數(shù)量太多,給實(shí)際應(yīng)用帶來(lái)不便。因此,在實(shí)際應(yīng)用中,XGMII接口通常被XAUI接口代替,XAUI即10Gigabit Attachment Unit Interface,XAUI在XGMII的基礎(chǔ)上實(shí)現(xiàn)了XGMII接口的物理距離擴(kuò)展,將PCB走線的傳輸距離增加到50cm,使背板走線成為可能。

源端XGMII把收發(fā)32位寬度數(shù)據(jù)流分為4個(gè)獨(dú)立的lane通道,每個(gè)lane通道對(duì)應(yīng)一個(gè)字節(jié),經(jīng)XGXS(XGMII ExtenderSublayer)完成8b/10b編碼后,將4個(gè)lane分別對(duì)應(yīng)XAUI的4個(gè)獨(dú)立通道,XAUI端口速率為:2.5Gbps*1.25*4=12.5Gbps。

在發(fā)送端的XGXS模塊中,將TXD[31:0]/RXD[31:0],TXC[3:0]/RXC[3:0],TX_CLK/RX_CLK轉(zhuǎn)換成串行數(shù)據(jù)從TX Lane[3:0]/RX Lane[3:0]中發(fā)出去,在接收端的XGXS模塊中,串行數(shù)據(jù)被轉(zhuǎn)換成并行,并且進(jìn)行時(shí)鐘恢復(fù)和補(bǔ)償,完成時(shí)鐘去抖,經(jīng)過(guò)5b/4b解碼后,重新聚合成XGMII。

XAUI接口采用差分線,收發(fā)各四對(duì),CML邏輯,AC耦合方式,耦合電容在10nF~100nF之間。

XAUI接口可以直接接光模塊,如XENPAK/X2等。也可以轉(zhuǎn)換成一路10G信號(hào)XFI,接X(jué)FP/SFP+等。

有些芯片不支持XAUI接口,只支持XGMII接口,這時(shí)可以用專門的芯片進(jìn)行XGMII→XAUI接口轉(zhuǎn)換,如BCM8011等。

XAUI/XLAUI/CAUI是四通道串行總線,采用的差分信號(hào),CML邏輯傳輸,并且進(jìn)行了擾碼,大大增強(qiáng)了信號(hào)的抗擾性能,使得信號(hào)的有效傳輸距離增加到50cm。

XAUI/XLAUI/CAUI在物理結(jié)構(gòu)上是一樣的,收發(fā)通道獨(dú)立,各四對(duì)差分信號(hào)線。

對(duì)于XAUI總線,每對(duì)差分線上的數(shù)據(jù)速率為3.125Gbps,總數(shù)據(jù)帶寬為12.5Gbps,有效帶寬為12.5Gbps*0.8=10Gbps(因?yàn)閄AUI總線數(shù)據(jù)在傳輸前進(jìn)行了8b/10b變換,編碼效率為80%)。

對(duì)于XLAUI總線,每對(duì)差分線上的數(shù)據(jù)速率為10.3125Gbps,總數(shù)據(jù)帶寬為41.25Gbps,有效帶寬為41.25Gbps*(64/66)=40Gbps(因?yàn)閄LAUI總線數(shù)據(jù)在傳輸前進(jìn)行了64b/66B變換,編碼效率為96.97%)。

對(duì)于CAUI總線,每對(duì)差分線上的數(shù)據(jù)速率為25.78125Gbps,總數(shù)據(jù)帶寬為103.125Gbps,有效帶寬為103.125Gbps*(64/66)=100Gbps(因?yàn)镃AUI總線數(shù)據(jù)在傳輸前進(jìn)行了64B/66B變換,編碼效率為96.97%)。

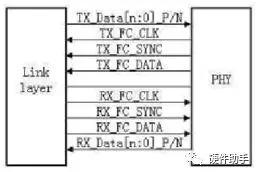

13、Interlaken

Interlaken是Cisco和Cortina公司共同推出的一種高速通道化的C2C(芯片間)接口協(xié)議。主要用于10Gbps端口的MAC、OC-768SONET Framer、下一代100Gbps以太網(wǎng)集成電路、100Gbps Swich Fabric與包處理器。主要有以下特征:

- 支持256個(gè)通道,可以擴(kuò)展到64K;

- 與SPI4.2(SystemPacket Interface Level 4 (SPI-4) Phase 2 Revision 1: OC-192 System Interfacefor Physical and Link Layer Devices.(OIF-SPI-4-2.1))類似,通過(guò)簡(jiǎn)單control word來(lái)表示packet;

- 通過(guò)Meta Frame完成各個(gè)lane的對(duì)齊;

- 協(xié)議本身和實(shí)際使用lane數(shù)目和SerDes速率無(wú)關(guān);

- 提供帶外帶內(nèi)兩種flow control方式,以及xon/xoff的整個(gè)接口的flow control;

- 采用64/67B數(shù)據(jù)編碼;

- 接口本身性能隨lane增加而同比增加。

TX_Ddta[n:0]p/n:數(shù)據(jù)發(fā)送通道,CML差分電平,每對(duì)差分線速率為1~6.25Gbps;

TX_FC_CLK:數(shù)據(jù)發(fā)送通道帶外流控參考時(shí)鐘,LVCMOS電平;

TX_FC_SYNC:數(shù)據(jù)發(fā)送通道帶外流控同步信號(hào),LVCMOS電平;

TX_FC_DATA:數(shù)據(jù)發(fā)送通道帶外流控?cái)?shù)據(jù)信號(hào),LVCMOS電平;

RX_Ddta[n:0]p/n:數(shù)據(jù)接收通道,CML差分電平,每對(duì)差分線速率為1~6.25Gbps;

RX_FC_CLK:數(shù)據(jù)接收通道帶外流控參考時(shí)鐘,LVCMOS電平;

RX_FC_SYNC:數(shù)據(jù)接收通道帶外流控同步信號(hào),LVCMOS電平;

RX_FC_DATA:數(shù)據(jù)接收通道帶外流控?cái)?shù)據(jù)信號(hào),LVCMOS電平;

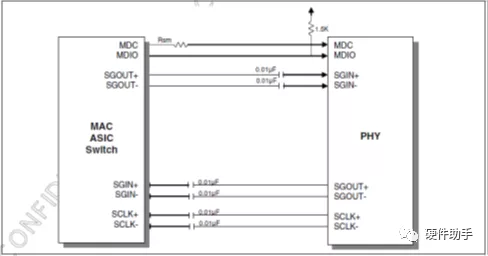

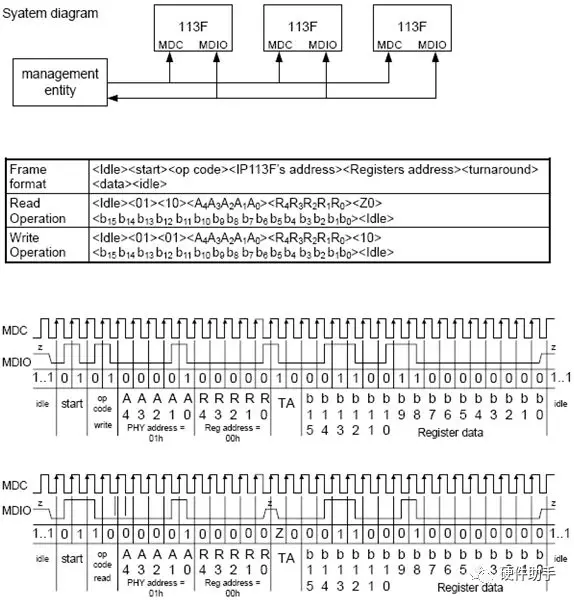

14、MDIO BUS(SMI(Serial Management Interface))

MDIO是一個(gè)以太網(wǎng)控制器的傳輸協(xié)議,廣泛用于以太網(wǎng)控制器和PHY之間的數(shù)據(jù)通訊。

MDIO(Management Data Input/Output),管理數(shù)據(jù)輸入輸出總線。它是由IEEE802.3定義的以太網(wǎng)行業(yè)標(biāo)準(zhǔn),它承載著MAC層和物理層通信的重任。MDIO接口包括兩根信號(hào)線:時(shí)鐘線MDC,數(shù)據(jù)線MDIO(雙向),MAC層芯片(或其他控制芯片)可以通過(guò)它們?cè)L問(wèn)物理層芯片的寄存器,并通過(guò)這些寄存器來(lái)對(duì)物理芯片進(jìn)行控制和管理。

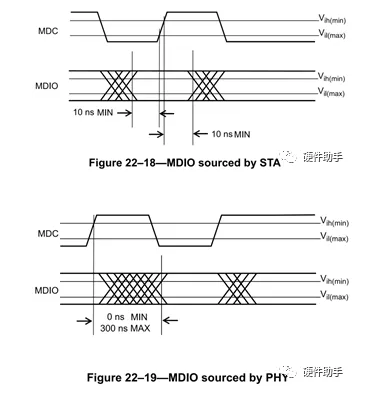

MDC(Management Data Clock):管理接口的時(shí)鐘,是一個(gè)非周期信號(hào),信號(hào)的最小周期為400ns(最快2.5MHz),最小正電平時(shí)間和負(fù)電平時(shí)間為160ns,最大正負(fù)電平時(shí)間無(wú)限制。

MDIO(Management Data Input/Output):是雙向的數(shù)據(jù)線,用來(lái)傳送MAC層的控制信息和物理層的狀態(tài)信息。它與MDC時(shí)鐘同步,在MDC上升沿有效。

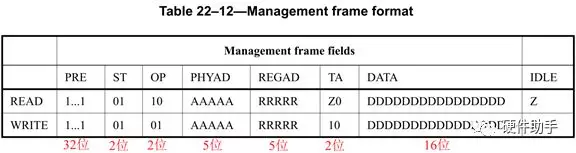

14.1、MDIO幀格式

PRE:幀前綴域,為32個(gè)連續(xù)“1”比特,這幀前綴域不是必需的,某些物理層芯片的MDIO操作就沒(méi)有這個(gè)域。

ST:幀開始標(biāo)識(shí)碼,為“01”。

OP:幀操作碼(讀寫操作),比特“10”表示此幀為一讀操作幀,比特“01”表示此幀為一寫操作幀。

PHYAD:PHY芯片的地址,5個(gè)比特,每個(gè)芯片都把自己的地址與這5個(gè)比特進(jìn)行比較,若匹配則響應(yīng)后面的操作,若不匹配,則忽略掉后面的操作。一個(gè)系統(tǒng)最多聯(lián)31個(gè)PHY(地址0為保留)。

REGAD:用來(lái)選擇物理層芯片的32個(gè)寄存器中的某個(gè)寄存器的地址。一個(gè)PHY上最多32個(gè)寄存器地址(可以使用shadow value技術(shù),訪問(wèn)更多的寄存器)。

TA:狀態(tài)轉(zhuǎn)換域,若為讀操作,則第一比特時(shí)MDIO為高阻態(tài),第二比特時(shí)由物理層芯片使MDIO置“0”。若為寫操作,則MDIO仍由MAC層芯片控制,其連續(xù)輸出“10”兩個(gè)比特。

DATA:幀的寄存器的數(shù)據(jù)域,16比特,若為讀操作,則為物理層送到MAC層的數(shù)據(jù),若為寫操作,則為MAC層送到物理層的數(shù)據(jù)。

IDLE:幀結(jié)束后的空閑狀態(tài),此時(shí)MDIO無(wú)源驅(qū)動(dòng),處于高阻狀態(tài),但一般用上拉電阻使其處在高電平,即MDIO引腳需要上拉電阻。

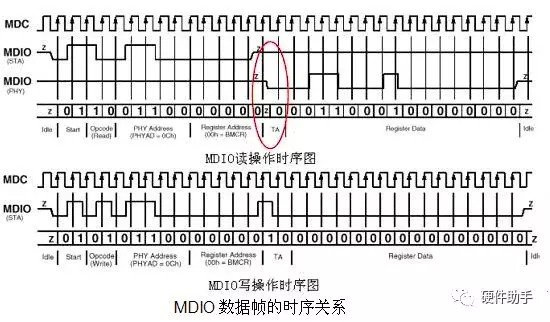

14.2、MDIO操作時(shí)序

MDIO工作流程如下:

- Preamle(PRE):在沒(méi)有傳輸數(shù)據(jù)的空閑狀態(tài)時(shí),數(shù)據(jù)線MDIO處于高阻態(tài)(由于外部上拉,故一直為1)。

- Start of Frame(ST):MAC驅(qū)動(dòng)MDIO線,出現(xiàn)一個(gè)2bit的開始標(biāo)識(shí)碼(01)。

- Operation Code(OP):MAC驅(qū)動(dòng)MDIO線,出現(xiàn)一個(gè)2bit數(shù)據(jù)來(lái)標(biāo)識(shí)是讀操作(10)還是寫操作(01)。

- PHY Address(PHYAD):MAC驅(qū)動(dòng)MDIO線,出現(xiàn)一個(gè)5bit數(shù)據(jù)標(biāo)識(shí)PHY的地址,對(duì)應(yīng)該地址的PHY芯片會(huì)響應(yīng)。

- Reg Address(REGAD):MAC驅(qū)動(dòng)MDIO線,出現(xiàn)一個(gè)5bit的PHY芯片寄存器地址(需要讀/寫的地址)。

- Turnaround(TA):寫操作的話,MAC驅(qū)動(dòng)MDIO線,出現(xiàn)10;讀操作的話,MDIO pin of MAC must be put in high-impedance state,在第二個(gè)周期,PHY驅(qū)動(dòng)MDIO線,出現(xiàn)0。

- Data,MDIO串行讀出/寫入PHY芯片寄存器的數(shù)據(jù)(16bit)。

- 最后MDIO恢復(fù)成空閑狀態(tài)(IDLE),同時(shí)MDIO進(jìn)入高阻狀態(tài)。

本文主要介紹了以太網(wǎng)MAC和PHY之間的接口,支持10Mbps到100Gbps的不同速率等級(jí),同時(shí)介紹了PHY芯片的控制接口MDIO總線。

-

以太網(wǎng)

+關(guān)注

關(guān)注

40文章

5483瀏覽量

173250 -

PHY

+關(guān)注

關(guān)注

2文章

309瀏覽量

52055 -

RMII

+關(guān)注

關(guān)注

0文章

8瀏覽量

12104 -

Side

+關(guān)注

關(guān)注

0文章

2瀏覽量

7732 -

控制接口

+關(guān)注

關(guān)注

0文章

15瀏覽量

10915

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

ML605上的RGMII鏈路速度更改為100Mbps或10 Mbps時(shí)測(cè)試失敗

在哪里可以找到10/100Mbps以太網(wǎng)的示例代碼?

以太網(wǎng)10/100Base-T 接口 以太網(wǎng) 100Base

盤點(diǎn)幾種以太網(wǎng)接口的設(shè)計(jì)與實(shí)現(xiàn)

以太網(wǎng)的接口是怎樣的情況

常見(jiàn)的工業(yè)交換機(jī)接口類型

ADIN1200:堅(jiān)固、工業(yè)、低功耗、10 Mbps和100 Mbps以太網(wǎng)PHY數(shù)據(jù)表

ADIN1300:穩(wěn)健、工業(yè)、低延遲和低功耗10 Mbps、100 Mbps和1 Gbps以太網(wǎng)PHY產(chǎn)品手冊(cè)

UG-1635:評(píng)估ADIN1300堅(jiān)固、工業(yè)、低延遲和低功耗10 Mbps、100 Mbps和1 Gbps以太網(wǎng)PHY

針對(duì)10Mbps到100Gbps不同以太網(wǎng)Drive Side接口類型

針對(duì)10Mbps到100Gbps不同以太網(wǎng)Drive Side接口類型

評(píng)論